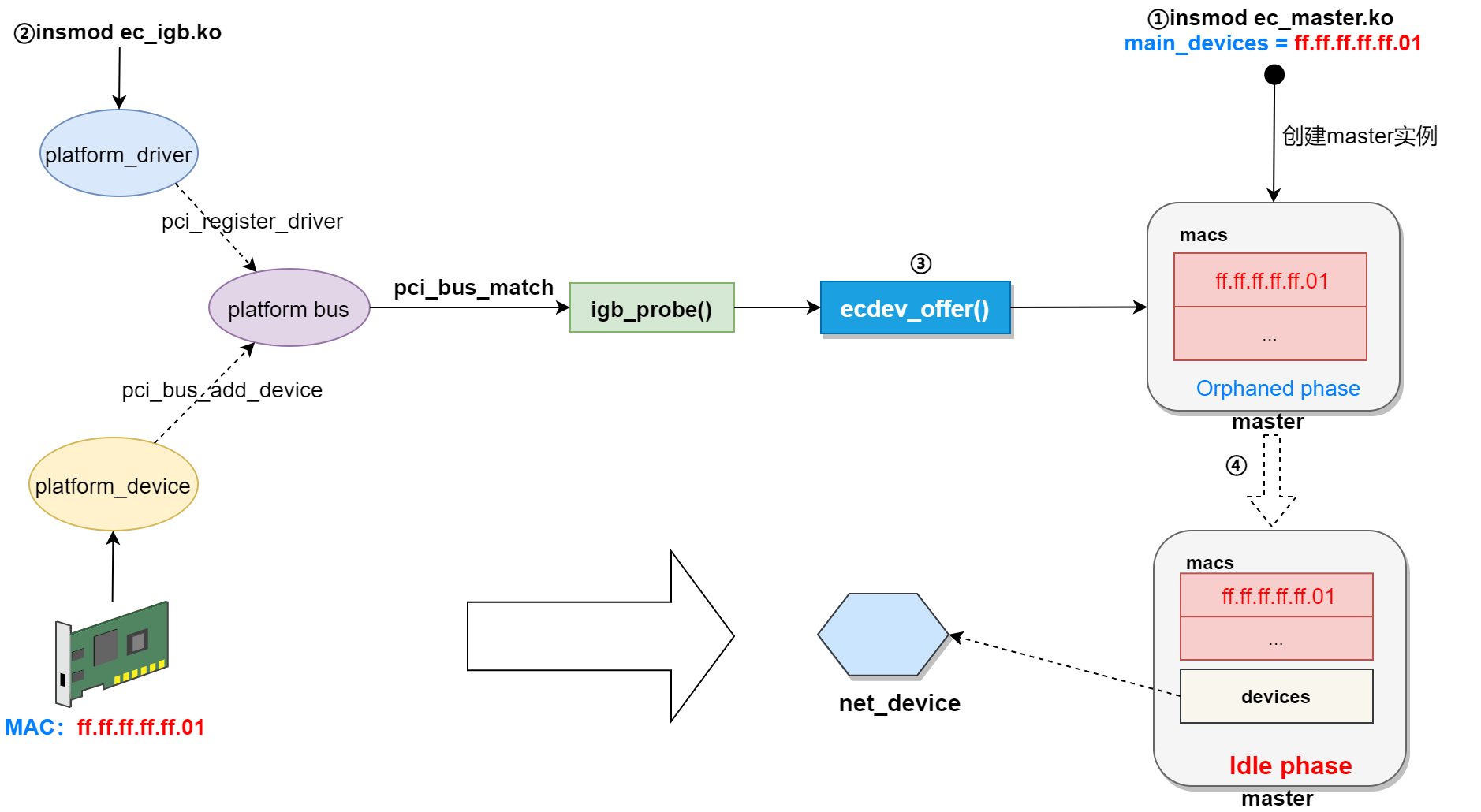

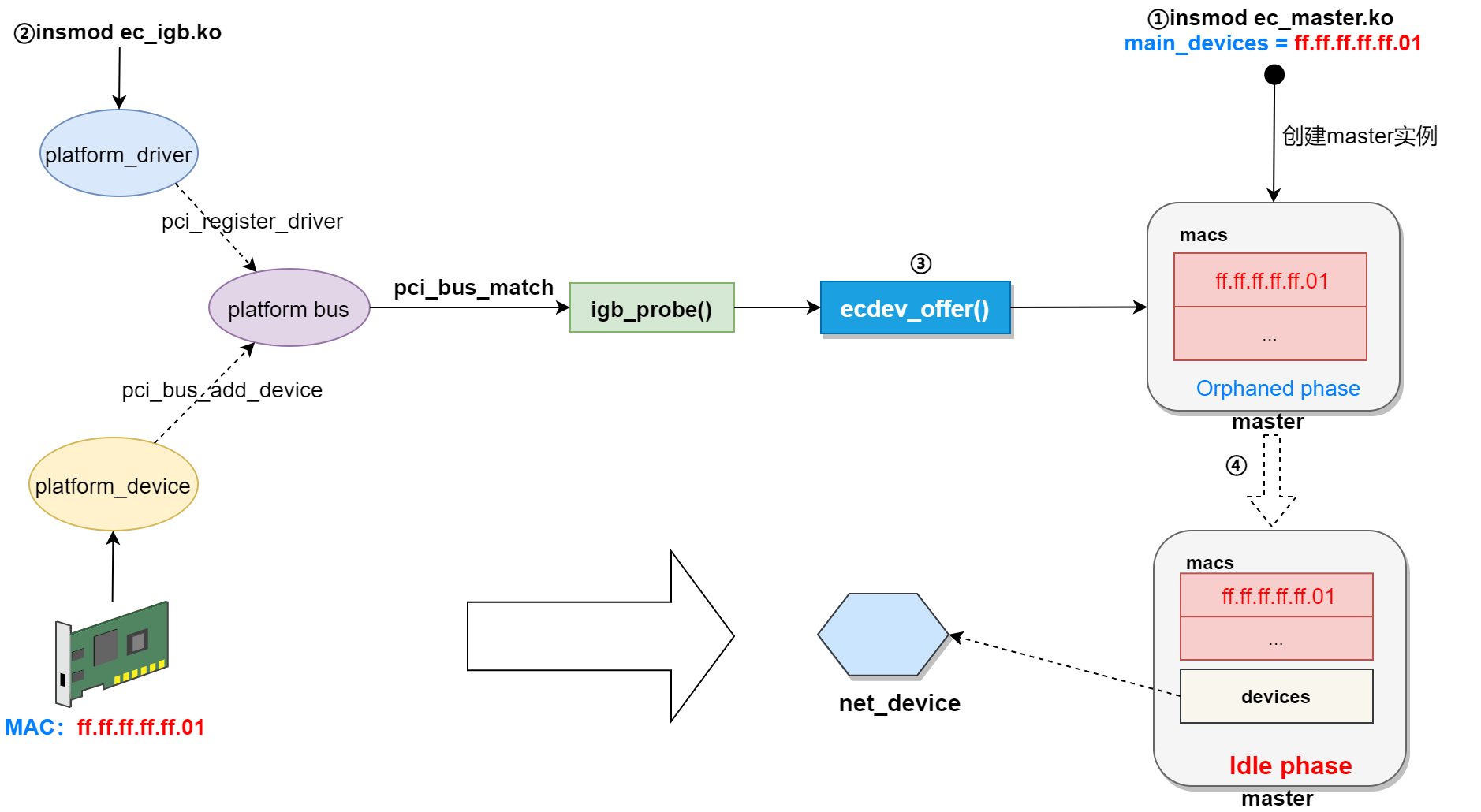

摘要:  目录0 获取源码1 启动脚本1.1 start1.2 stop2 主站实例创建2.1 Master Phases2.2 数据报与状态机数据报状态机2.3 master状态机及数据报初始化2.4 初始化EtherCAT device2.5 设置IDLE 线程的发送间隔:2.6 初始化字符设备3 网卡4 阅读全文

目录0 获取源码1 启动脚本1.1 start1.2 stop2 主站实例创建2.1 Master Phases2.2 数据报与状态机数据报状态机2.3 master状态机及数据报初始化2.4 初始化EtherCAT device2.5 设置IDLE 线程的发送间隔:2.6 初始化字符设备3 网卡4 阅读全文

目录0 获取源码1 启动脚本1.1 start1.2 stop2 主站实例创建2.1 Master Phases2.2 数据报与状态机数据报状态机2.3 master状态机及数据报初始化2.4 初始化EtherCAT device2.5 设置IDLE 线程的发送间隔:2.6 初始化字符设备3 网卡4 阅读全文

目录0 获取源码1 启动脚本1.1 start1.2 stop2 主站实例创建2.1 Master Phases2.2 数据报与状态机数据报状态机2.3 master状态机及数据报初始化2.4 初始化EtherCAT device2.5 设置IDLE 线程的发送间隔:2.6 初始化字符设备3 网卡4 阅读全文

posted @ 2021-02-22 23:39

沐多

阅读(21113)

评论(6)

推荐(8)

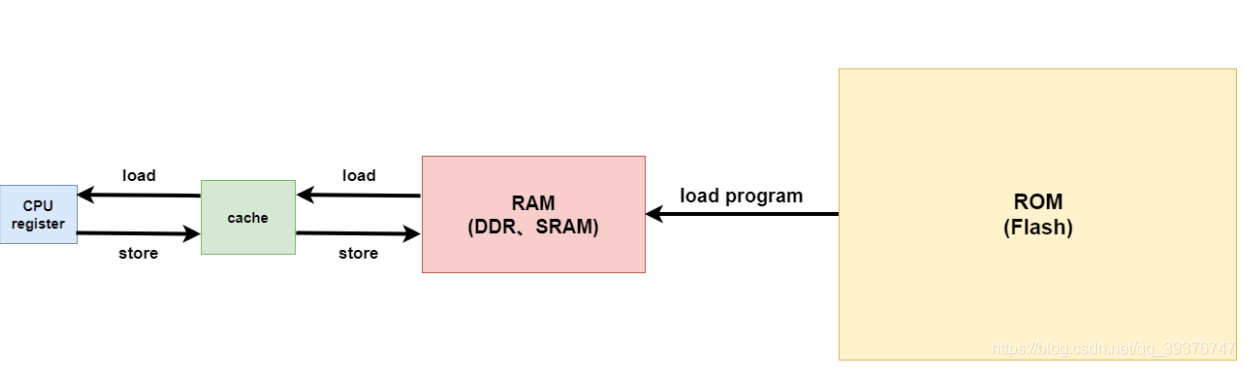

本文主要以DSP讲解cache原理,但原理与CPU是相通的,故转载,原文地址:https://blog.csdn.net/qq_39376747/article/details/112794096 DSP 缓存机制 注:本文说明的DSP基于TI c6000系列的C66x DSP 1.Cache基础

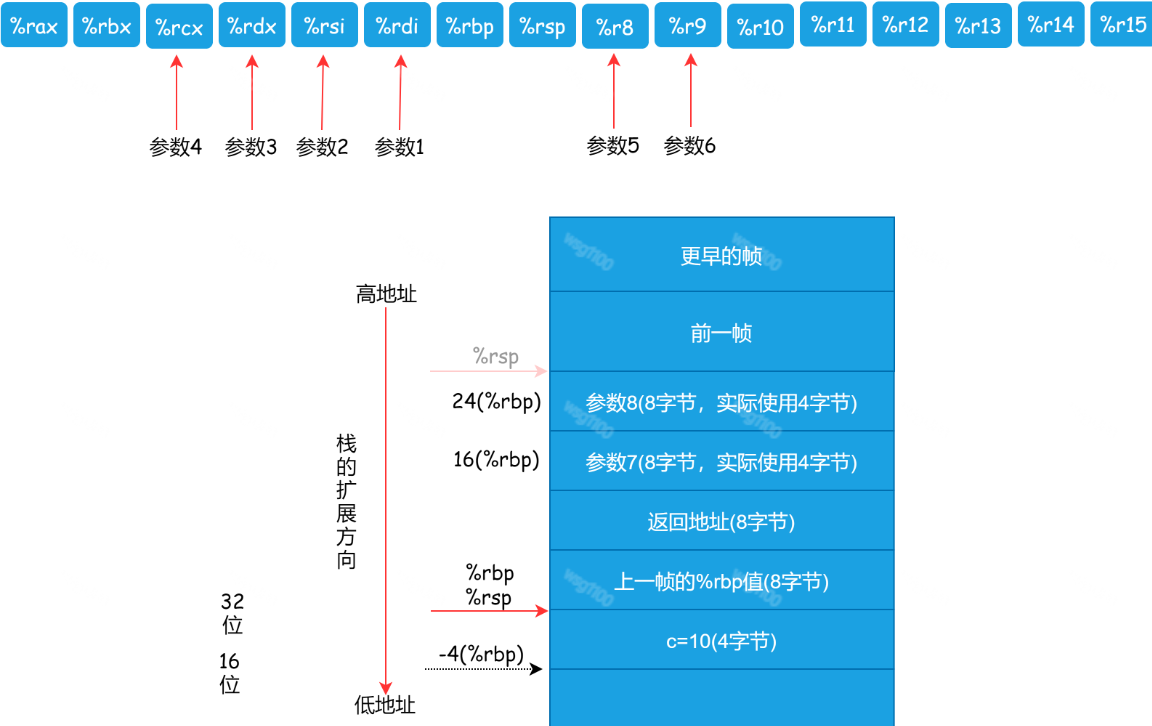

本文主要以DSP讲解cache原理,但原理与CPU是相通的,故转载,原文地址:https://blog.csdn.net/qq_39376747/article/details/112794096 DSP 缓存机制 注:本文说明的DSP基于TI c6000系列的C66x DSP 1.Cache基础  整理的X86_64/X86汇编、寄存器、C内嵌汇编笔记,主要用于查阅使用。 一、汇编语言 计算机的处理器有很多不同的架构,比如 x86-64、ARM、Power 等,每种处理器的指令集都不相同,那也就意味着汇编语言不同。目前的电脑,CPU 一般是 x86-64 架构,是 64 位机。 C语言代码:

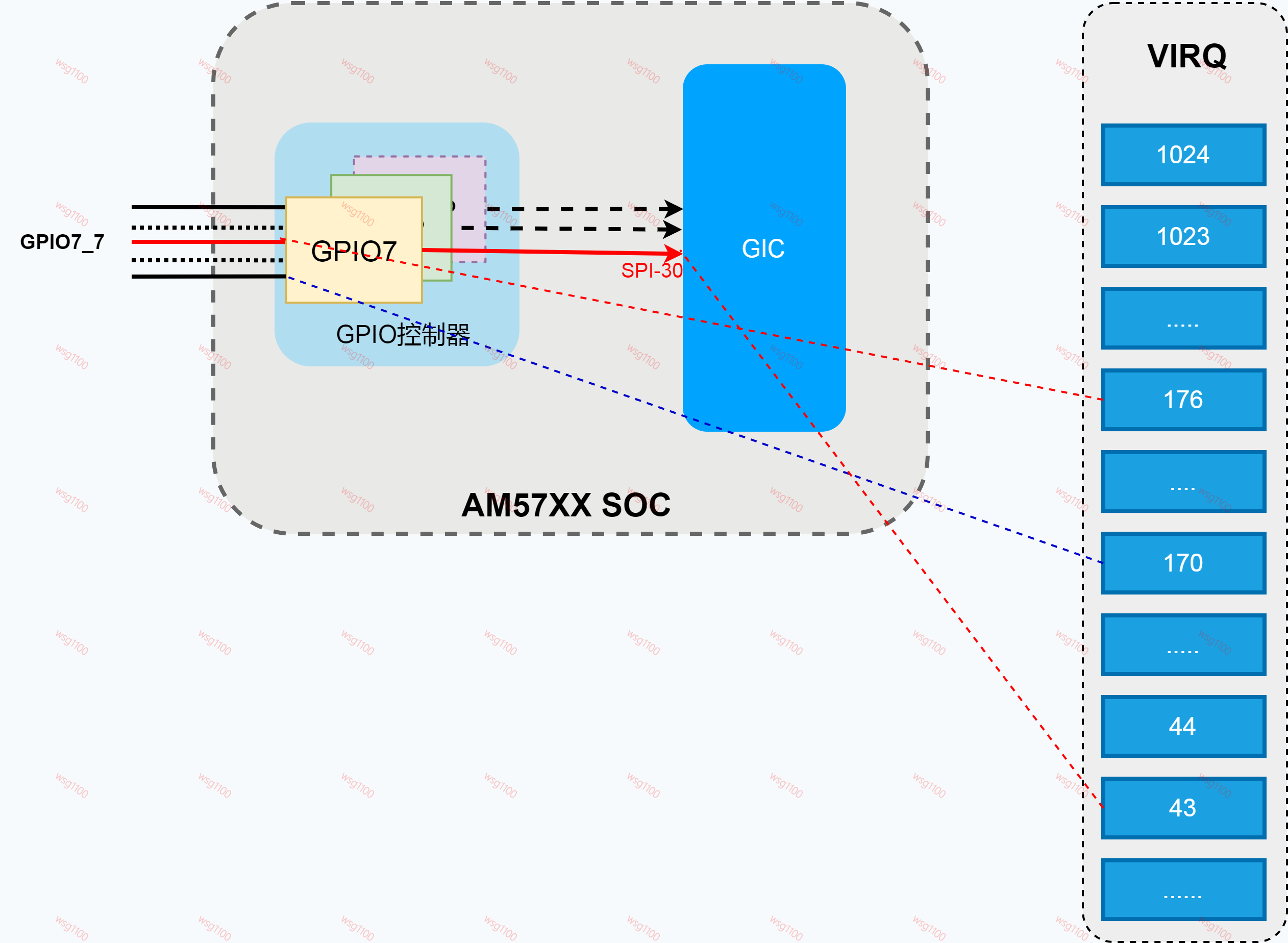

整理的X86_64/X86汇编、寄存器、C内嵌汇编笔记,主要用于查阅使用。 一、汇编语言 计算机的处理器有很多不同的架构,比如 x86-64、ARM、Power 等,每种处理器的指令集都不相同,那也就意味着汇编语言不同。目前的电脑,CPU 一般是 x86-64 架构,是 64 位机。 C语言代码:  本文以AM5728 GPIO中断为例,简单介绍有关从注册GIC中断到 驱动使用GPIO中断的整个过程,主要关注中断相关处理流程,为后续ARM平台xenomai IPIPE中断处理流程做铺垫。 第一部分: GIC中断控制器的注册。 第二部分:设备树的device node在向platform_devi

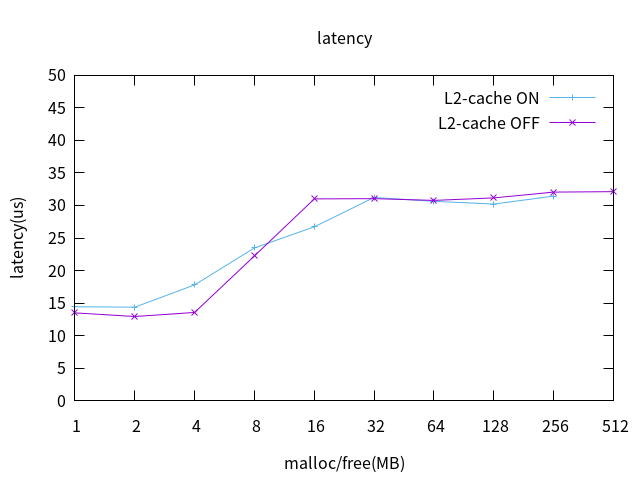

本文以AM5728 GPIO中断为例,简单介绍有关从注册GIC中断到 驱动使用GPIO中断的整个过程,主要关注中断相关处理流程,为后续ARM平台xenomai IPIPE中断处理流程做铺垫。 第一部分: GIC中断控制器的注册。 第二部分:设备树的device node在向platform_devi  ARM平台下内存和cache对xenomai实时性的影响。

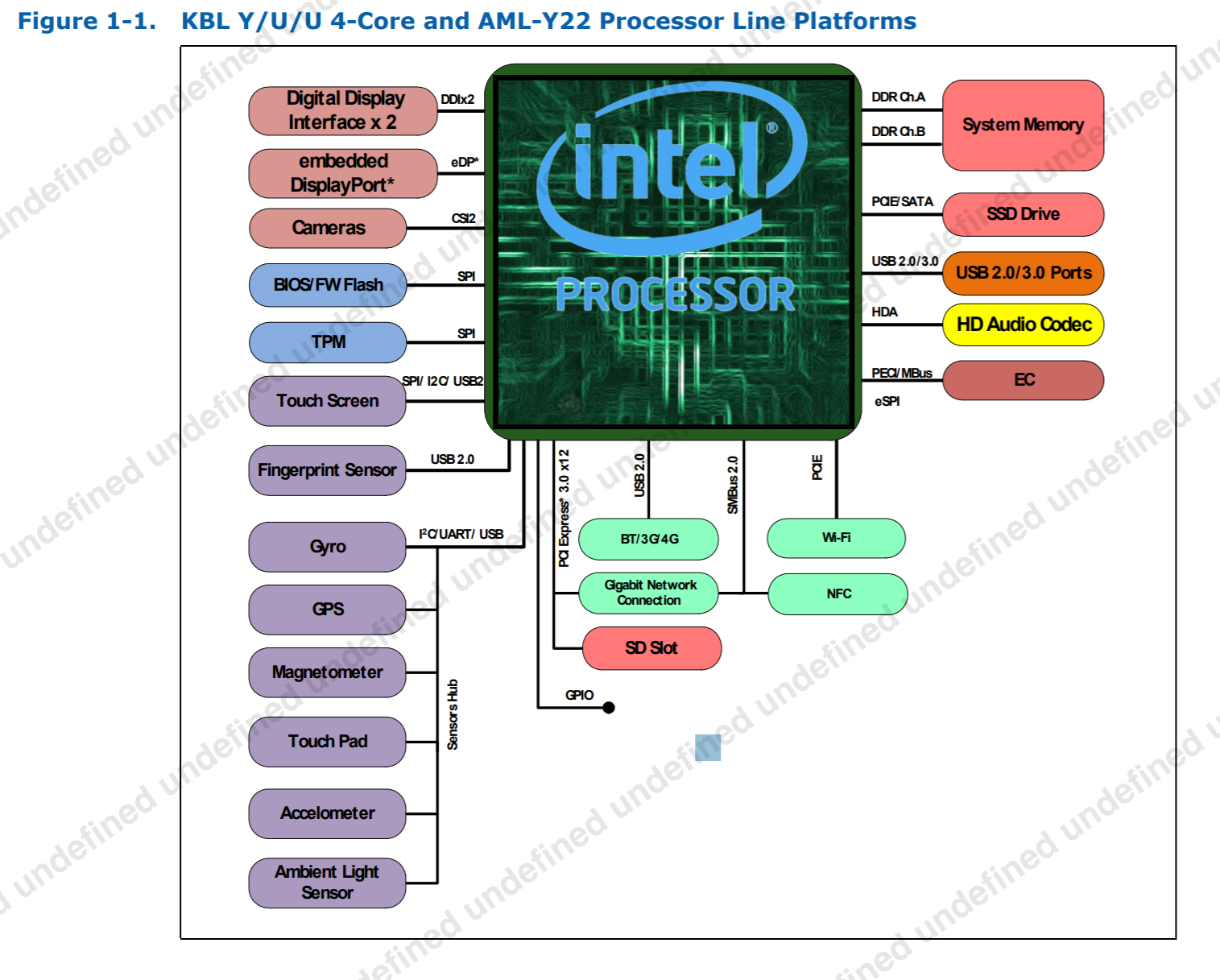

ARM平台下内存和cache对xenomai实时性的影响。  1.前言 在arm嵌入式开发中,各个外设具有固定的物理地址,我们可以直接通过芯片手册来编写驱动配置后使用。但是在x86中有所不同,所有外设控制器集成在PCH(曾经的南桥)中,每个外设都是作为一个PCI设备挂在PCH的PCI总线上,PCH再通过DMI与CPU相联。对于标压处理器H/K系列(也就是我们台

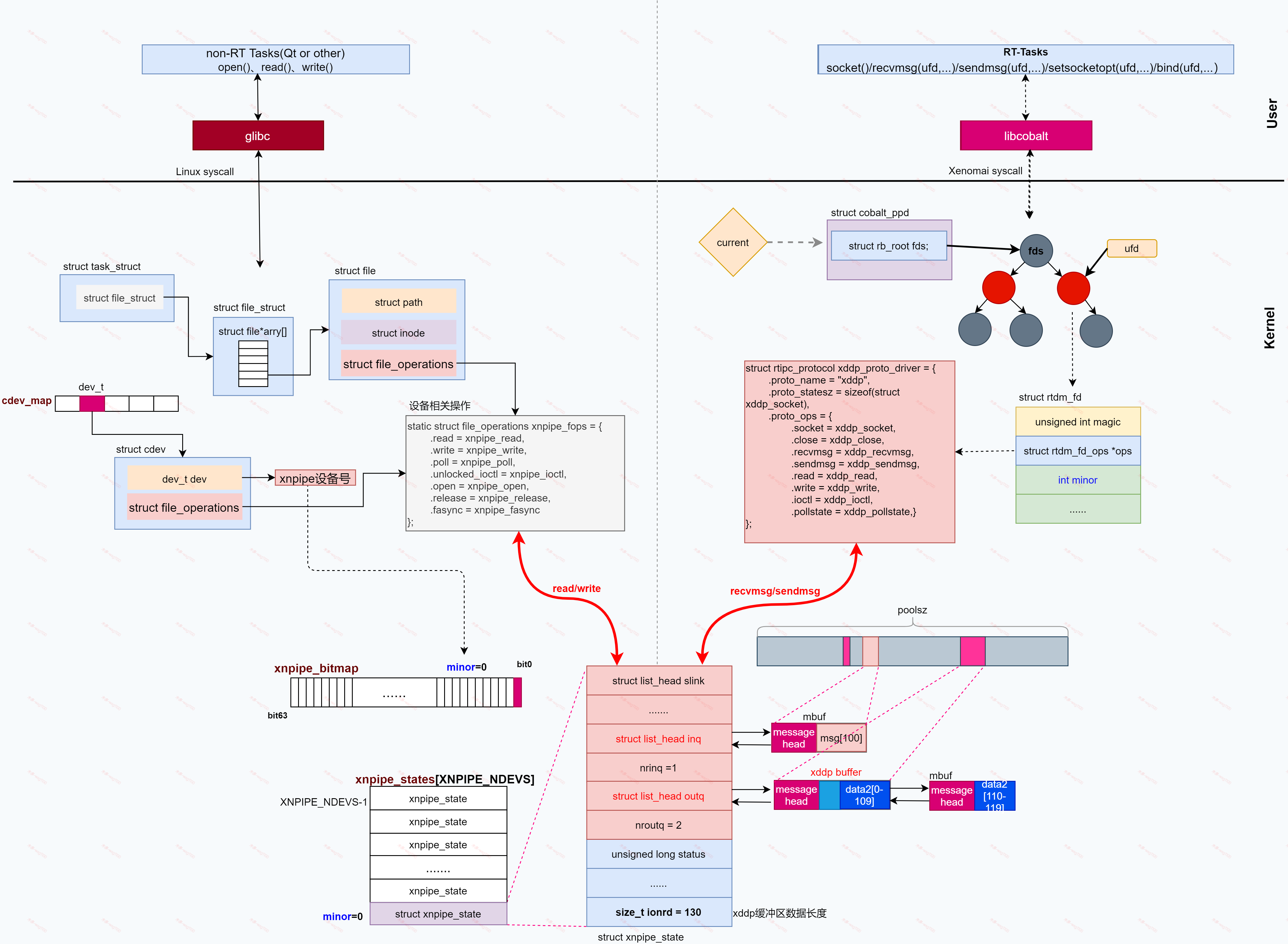

1.前言 在arm嵌入式开发中,各个外设具有固定的物理地址,我们可以直接通过芯片手册来编写驱动配置后使用。但是在x86中有所不同,所有外设控制器集成在PCH(曾经的南桥)中,每个外设都是作为一个PCI设备挂在PCH的PCI总线上,PCH再通过DMI与CPU相联。对于标压处理器H/K系列(也就是我们台  本文介绍了Xenomai中的XDDP(Xenomai Distributed Data Protocol)通信机制,XDDP用于实时和非实时进程之间的数据交换。XDDP在Xenomai内核中涉及的数据结构和管理方式,以及创建XDDP通道后的实时端和非实时端连接过程。

本文介绍了Xenomai中的XDDP(Xenomai Distributed Data Protocol)通信机制,XDDP用于实时和非实时进程之间的数据交换。XDDP在Xenomai内核中涉及的数据结构和管理方式,以及创建XDDP通道后的实时端和非实时端连接过程。  浙公网安备 33010602011771号

浙公网安备 33010602011771号