摘要:在uvm里面的使用: 功能覆盖率的时候使用: covergroup cg_apb_command @(posedge clk iff rstn); endgroup monitor的时候使用: task apb_master_monitor::collect_transfer(); // Advan

阅读全文

摘要:1、`timescale是个编译参数,编译时候起作用。 2、在没有定义`timescale的module中,其timescale使用跟它最近的一个且编译顺序上排在前的module中的timescale。 3、如果编译顺序前的module也没有timescale,则使用编译命令输入的default t

阅读全文

摘要:typedef logic [15:0] r_t;//变量类型; r_t r;//声明变量; integer i = 1; string b = ""; string a = {"Hi", b}; r = r_t'(a); // OK b = string'(r); // OK 注意不需要对等号左边

阅读全文

摘要:在UVM中,使用uvm_field_automation机制注册二维数组需要特殊处理,因为UVM没有直接支持二维数组的宏。以下是三种实现方法,从推荐程度排序: 方法1:使用动态数组的动态数组 + 自定义处理(推荐) class my_item extends uvm_sequence_item; /

阅读全文

摘要:在SystemVerilog中,将1位的bit类型值1扩展为8位的byte类型(所有位均为1,即8'b11111111),可以通过以下两种方法实现: 1. 使用位复制操作符(推荐) bit a = 1'b1; // 1位变量,值为1 byte b; // 8位有符号整数类型 assign b = {

阅读全文

摘要:句柄的传递 句柄可以用来创建多个对象,也可以前后指向不同对象 Transaction t1,t2; // 声明句柄 t1 = new(); // 创建对象并将其指针赋予t1 t2 = new(); // 创建对象并将其指针赋予t2 t1 = t2; // 将t2的值赋予t1,t1和t2指向同一对象,

阅读全文

摘要:做IC 验证进行transaction比对时,发现曾经验证通过的module总是发生mismatch的情况,这是不应该发生的情况,因为这个module曾经已经验证通过并且RTL已经稳定,bench也很稳定,但是出现了mismatch的情况。最后经过debug发现两种不同写法的代码会导致不同的结果:

阅读全文

摘要:使用SystemVerilog搭建环境的时候,经常会遇到需要对一个对象进行复制,以防止对象的方法修改原始对象的值。对于初学者经常会使用new函数来实现class的内建的复制功能,但是,当要复制的对象中含有其他对象(object)时,使用内建的复制功能将会得到不期望的结果。本文将示例说明shallow

阅读全文

摘要:当某个信号出现多于一个驱动源的时候,或者某个信号是双向(inout)的时候,都需要使用wire来完成线网连接。具体用法就是声明某个信号为wire sigal_a;或者wire logic signal_a;就可以了。 注意直接声明为logic signal_a;是不行的,会报类似如下的错误:xmel

阅读全文

摘要:Verilog/SystemVerilog ``` //条件语句 if () else if() else //条件编译 `ifdef macro `ifndef macro `elsif macro `else `endif ``` bash shell ``` //条件语句 if command

阅读全文

摘要:``` 在搭建验证环境时,经常需要在环境中插入很多info用于输出一定的log信息用于进行debug,在插入这些info方法的时候,经常需要同时输出该方法执行的具体时间,用于方便定位问题,为此在Verilog和SystemVerilog中提供了一堆关于time的方法,如果对于这些方法使用的不是很恰当

阅读全文

摘要:这个系统函数在[IEEE]SystemVerilog.std.1800_2017里你是搜索不到的,但是你在SystemVerilog的环境中是可以使用的。 你可以使用$stack()这个系统函数来查看报错的文件层次,类似于python的trackback,可以帮助你定位异常问题,从而协助你进行deb

阅读全文

摘要:``` 本文主要给大家介绍SV宏,谈到SV宏大家应该不会感到陌生,因为大家在做前端设计或验证的时候会用到`define定义宏,进行条件编译,或者使用宏来定义参数等,做前端验证的工程师会使用`define来定义一些信号路径等。这些SV宏的用法都是比较常规的用法,很少有验证工程师使用SV宏来处理一些其他

阅读全文

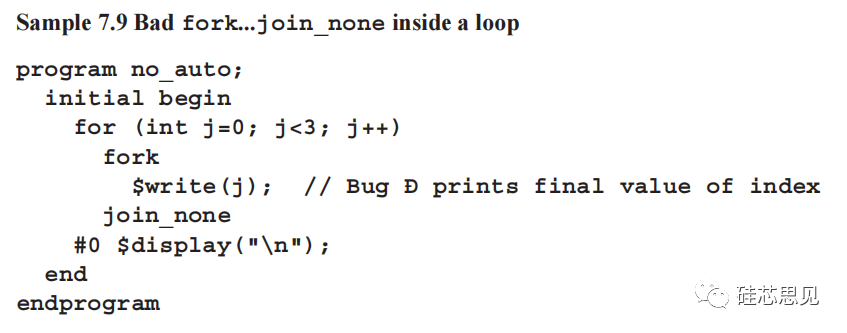

摘要: 示例中,在for循环中使用了fork...join_none结构调用$write显示每次循环执行过程中循环变量的

阅读全文

摘要:我们在工作中常常会针对数组施加各式的约束,下面列举一下有趣的Systemverilog数组约束示例: 1、如何约束动态数组的最后一个元素为特定值。(事先不知道数组的大小) ``` rand int some_dynamic_array[]; constraint last_elem_c { some

阅读全文

摘要:为了方便与C、C++等语言的交互,uvm中引入了DPI接口,自定义的函数需要写函数主体,然后再import后声明和使用,验证环境中便可以像调用system verilog中的函数一样使用这些函数。而且,对于C语言中内置的函数,不需要写函数主体,直接声明使用。同理c语言也可以调用sv里面的函数或者ta

阅读全文

摘要:定宽和动态数组初始化时需要加符号';队列不需要。 定宽数组的声明: int lo_hi[0:15];//16个整数[0]...[15] int c_style[16];//16个整数[0]...[15] 声明并使用多维数组: int array2[0:7][0:3];//完整的声明 int arra

阅读全文

摘要:在一个父类与子类中: 在父类中有一个变量,在子类中有一个不一样的变量; 在父类和子类中都有一个virtual的且同名的函数; 如果将子类句柄赋值给父类句柄时: 在父类句柄中引用一个变量时,会先从子类里面找,如果找不到再到父类里面找。 父类与子类中的变量和函数没有任何关系。 虚方法:

阅读全文

摘要:soft表示的是软约束,如果在一个约束块中使用soft,那么表示这个约束块相比于没有使用soft的约束块(硬约束块)的优先级要低。 在constraint中的约束表达,可以使用soft修饰,当该约束和其他非soft约束冲突时,soft修饰的约束会失效。 要注意的是除了soft软约束块外,所有的约束块

阅读全文

摘要:#100 intf.drv_ck.ch_valid <= 1; 延迟一百个时间单位后,执行后面的语句。 2. #100; intf.drv_ck.ch_valid <= 1; 延迟一百个事件单位后,执行后面的语句。 3. @(posedge clk); clk上升沿到来后,执行后面的语句。 4. r

阅读全文