sytemverilog中timescale的用法小结

1、`timescale是个编译参数,编译时候起作用。

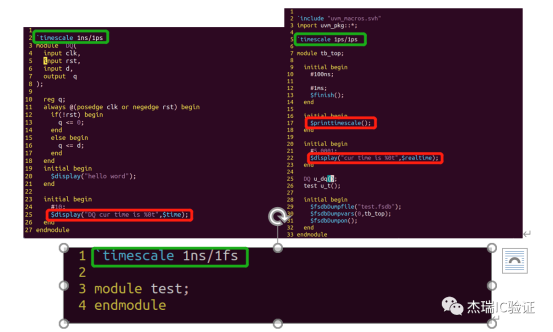

2、在没有定义`timescale的module中,其timescale使用跟它最近的一个且编译顺序上排在前的module中的timescale。

3、如果编译顺序前的module也没有timescale,则使用编译命令输入的default timescale。default timescale就是指我们编译时输入的timescale的编译器命令选项。

4、推荐使用SystemVerilog的系统函数$printtimescale来打印timescale信息。这个函数可以带参数。

大家先看看上面的打印结果,自己先思考下原因:

这是个仿真时起作用的参数,它由我们所有定义的timeprecision里的最小的一个来决定!

跟global相对的就是local timeprecision,它是我们所在module或者文件的timeprecision,生命周期只到此module或者文件,此为编译参数,与仿真无关。

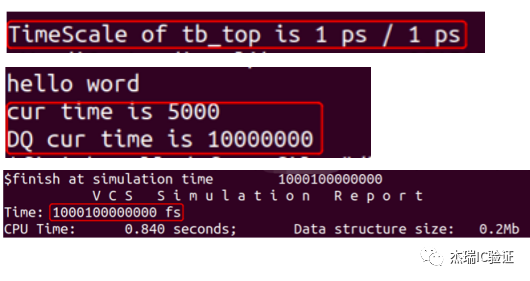

1、首先printtimescale对应的打印信息就是我们对应的`timescale 1ps/1ps,module tb_top的timeunit为1ps,local timeprecision为1ps 。

2、从上图可以看出我们的最小的参与仿真的timeprecision为module test头上对应的1fs,所以global timeprecision也就是1fs,global timepricision为仿真参数。从vcs的打印上我们也能看出对应的global timeprecison,Time:1000100000000fs,对应的仿真时间精度就是fs。

3、结合1和2,tb_top中的第22行display对应的5000就可以很好理解了,#5.0001 == #5ps(此处理解可参考黄鸭哥的timescale的第一期,相当于timeunit和local timeprecision的比例关系,简单的说local timeprecision管的是编译,global timerecision管的是运行,例如#5.0001是在编译时就决定了,tb_top中的第22行$display是在仿真时才决定),5ps == 5000fs,仿真运行到此处时就应该输出cur time is 5000。对于module DQ的第25行的输出也是和3一样的道理。

浙公网安备 33010602011771号

浙公网安备 33010602011771号