参考文档:https://www.intel.com/content/www/us/en/docs/programmable/683525/21-3/eol.html

1. Introduction to the Avalon® Interface Specifications:

Avalon总线是一种协议较为简单的片内总线,主要用于连接片内处理器与外设,以构成片上可编程系统(SOPC)。使用Avalon接口能够轻松连接Intel (Altera) FPGA中的各个组件,从而简化了系统设计。Avalon接口常用于高速数据流传输、读写寄存器和存储器、控制片外器件等。此外,也可以使用Avalon接口自定义组件,以增强设计的互操作性。Avalon共有以下七种接口:

- Avalon Clock Interface, Avalon时钟接口 -- 驱动或接收时钟信号的接口。

- Avalon Reset Interface, Avalon复位接口 -- 驱动或接收复位信号的接口。

- Avalon Memory Mapped Interface (Avalon-MM), Avalon存储器映射接口 -- 基于地址的读/写接口,是主-从连接的典型接口。

- Avalon Streaming Interface (Avalon-ST), Avalon Streaming接口 --支持单向数据流的接口,包括多数据流、数据包和DSP数据的传输。

- Avalon Conduit Interface, Avalon Conduit接口--适用于不适合任何其他Avalon类型的单个/多个信号。使用该接口可以将信号导出到顶层SOPC系统,这样就可以将它连接到设计的其他模块。

- Avalon Tri-State Conduit Interface (Avalon-TC), Avalon 三态Conduit接口 -- 与片外设备的接口。多个外设可以通过信号的多路复用共享引脚,从而减少FPGA引脚数和PCB走线数。

- Avalon Interrupt Interface, Avalon 中断接口--允许组件向其他组件发送事件信号的接口。

一个组件可以包含多个不同类型的接口,也可以包含多个相同类型的接口。

Avalon接口通过属性(property)描述它们的行为。每种接口类型的规范定义了所有接口的属性和默认值。比如,Avalon-ST接口的maxChannel属性指定接口支持的通道数量,Avalon Clock接口的clockRate属性描述时钟信号的频率。

每个Avalon接口都定义了一系列的信号及其行为,并且多数信号都是可选的,这允许组件设计者能够更加灵活地选择需要的信号类型。例如,Avalon-MM接口包含可选的beginbursttransfer和burstcount信号,用于那些支持突发(bursting)传输的组件。Avalon-ST接口包含可选的startofpacket和endofpacket信号,用于支持数据包的接口。

每种接口都有时序方面的信息,这些时序信息描述了针对单个类型的传输。

注:一般用户只用了Avalon时钟接口、Avalon复位接口、Avalon存储器映射接口和Avalon Conduit接口,下面将着重介绍这四种接口,其余接口请参考请参考Intel FPGA的Avalon Interface Specification文档。

Avalon时钟接口

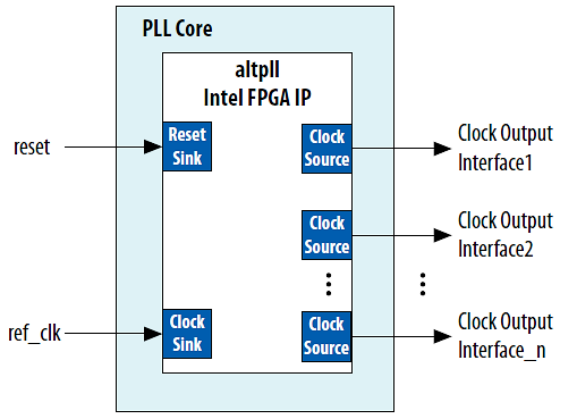

Avalon时钟接口定义了组件使用的时钟,一个组件可以有时钟输入、时钟输出或时钟输入输出都含有。例如,锁相环(PLL)是一个包含了时钟输入和时钟输出的组件,如图2所示。

PLL Core的时钟输入和输出

Clock Sink信号

Clock sink为其他接口和内部逻辑提供时钟和时序参考,clock sink的属性有clockRate,用来表示clock sink接口的频率(Hz),默认值为0。

表1.1 Clock Sink信号

|

信号 |

宽度 |

方向 |

必需 |

描述 |

|

clk |

1 |

Input |

是 |

时钟信号,为其他接口和内部逻辑提供时钟和时序参考 |

表1.2 Clock Sink属性

|

属性名称 |

默认值 |

合法值 |

描述 |

|

clockRate |

0 |

0 ~ 232-1 |

表示clock sink接口的频率(Hz)。如果为0,那么时钟速率支持任何频率。如果为非0,那么当连接的clock source不是指定的频率时Platform Designer会发出一个警告消息。 |

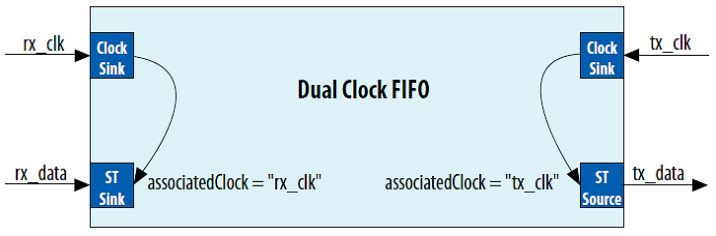

所有同步接口都有一个associatedClock 属性,该属性指定组件上的哪个时钟源(clock source)用作接口的同步参考,如图所示。

associatedClock属性

Clock Source信号

Clock source接口从一个组件中输出一个时钟信号。clock source有三个属性,associatedDirectClock表示直接驱动该时钟的时钟名称,clockRate表示时钟输出的频率,clockRateKnown指示时钟频率是否已知。

表1.3 Clock Source信号

|

信号 |

宽度 |

方向 |

必需 |

描述 |

|

clk |

1 |

Output |

是 |

一个输出时钟信号 |

表1.4 Clock Source属性

|

属性名称 |

默认值 |

合法值 |

描述 |

|

associatedDirectClock |

N/A |

输入时钟名 |

直接驱动此时钟输出的时钟输入的名称(如果有)。 |

|

clockRate |

0 |

0 ~ 232-1 |

表示驱动时钟输出的频率(Hz)。 |

|

clockRateKnown |

false |

true, false |

指示时钟频率是否已知。如果是,那么可以自定义系统中的其他组件。 |

Avalon复位接口

与Avalon时钟接口类似,Avalon复位接口也分为Reset Sink和Reset Source。

Reset Sink

Reset sink包含两个信号,reset/reset_n和reset_req,reset_req是一个可选的信号。Reset sink有两个属性,associatedClock表示与该接口同步的时钟,synchronous-Edges表示复位所需要的同步类型,NONE表示不需要同步,DEASSERT表示复位是异步的,取消复位是同步的,BOTH表示复位和取消复位都是同步的。所有同步接口都有一个associatedReset属性,用于指定哪个复位信号对接口逻辑进行复位。

表1.5 Reset Sink信号

|

信号 |

宽度 |

方向 |

必需 |

描述 |

|

reset, reset_n |

1 |

Input |

是 |

将接口或组件的内部逻辑复位成用户定义的状态。复位的同步属性由synchronousEdges参数定义。 |

|

reset_req |

1 |

Input |

否 |

复位信号的早期指示。此信号用作ROM原语的待定复位的一个周期警告。使用reset_req 来禁止时钟使能或屏蔽片上存储器的地址总线,在异步复位输入置位时防止地址转变。 |

表1.6 Reset Sink属性

|

属性名称 |

默认值 |

合法值 |

描述 |

|

associatedClock |

N/A |

时钟名称 |

与此接口同步的时钟的名称。如果synchronousEdges的值为DEASSERT或者BOTH,那么需要使用此属性。 |

|

synchronous-Edges |

DEASSERT |

NONE DEASSERT BOTH |

表明复位输入所需要的同步类型。定义为: NONE -- 不需要同步,因为组件包含用于复位信号内部同步的逻辑。 DEASSERT -- 复位是异步的,取消复位是同步的。 BOTH –- 复位和取消复位是同步的。 |

Reset Source

Reset source也是包含两个信号,reset/reset_n和reset_req,reset_req是一个可选的信号。Reset source有四个属性,associatedClock表示与该接口同步的时钟;associatedDirectReset表示复位输入的名称,此复位输入通过one-to-one 链路直接驱动此复位源;associatedResetSinks用来指定复位输入,使复位源对复位进行复位;synchronous-Edges表示复位所需要的同步类型,NONE表示不需要同步,DEASSERT表示复位是异步的,取消复位是同步的,BOTH表示复位和取消复位都是同步的。

表1.7 Reset Source信号

|

信号 |

宽度 |

方向 |

必需 |

描述 |

|

reset, reset_n |

1 |

Output |

是 |

将接口或组件的内部逻辑复位成用户定义的状态。 |

|

reset_req |

1 |

Output |

否 |

使能复位请求生成,这是一个早期信号,在复位之前被置位。一旦置位此信号,在复位完成之前不能置低此信号。 |

表1.8 Reset Source属性

|

属性名称 |

默认值 |

合法值 |

描述 |

|

associatedClock |

N/A |

时钟名称 |

与此接口同步的时钟的名称。如果synchronousEdges的值为DEASSERT或者BOTH,那么需要使用此属性。 |

|

associatedDirectReset |

N/A |

复位名称 |

复位输入的名称,此复位输入通过one-to-one链路直接驱动此复位源(reset source)。 |

|

associatedResetSinks |

N/A |

复位名称 |

指定复位输入,使复位源对复位进行复位。例如,reset synchronizer,执行与多个复位输入的OR操作来生成一个复位输出。 |

|

synchronous-Edges |

DEASSERT |

NONE DEASSERT BOTH |

表明复位输入所需要的同步类型。以下值定义为: NONE -- 不需要同步,因为组件包含用于复位信号内部同步 的逻辑。 DEASSERT -- 复位是异步的,取消复位是同步的。 BOTH –- 复位和取消复位是同步的。 |

Avalon存储器映射接口

Avalon存储器映射接口主要用于实现主-从(Master-Slave)组件的读写接口,微处理器、存储器、UART、DMA、定时器(Timer)是常用的包含Avalon存储器映射接口的组件。Avalon-MM接口有简单的也有复杂的。例如,SRAM接口有固定周期的读写传输,具有简单的Avalon-MM 接口。能够进行突发传输的流水线接口(pipelined interface)有更为复杂的Avalon-MM接口。

这里我们只介绍简单的Avalon-MM接口,较为复杂的流水线接口请参考Intel FPGA的Avalon Interface Specification文档。

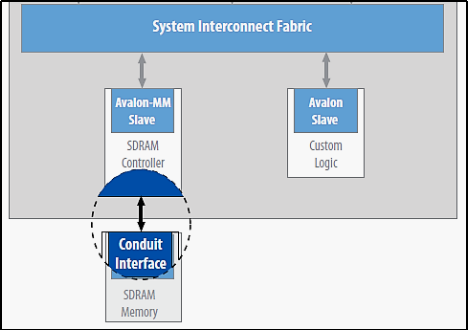

下图是一个典型的系统,图中加亮并画圈的是Avalon-MM slave接口与互连(interconnect)架构的连接。

Avalon-MM Slave传输

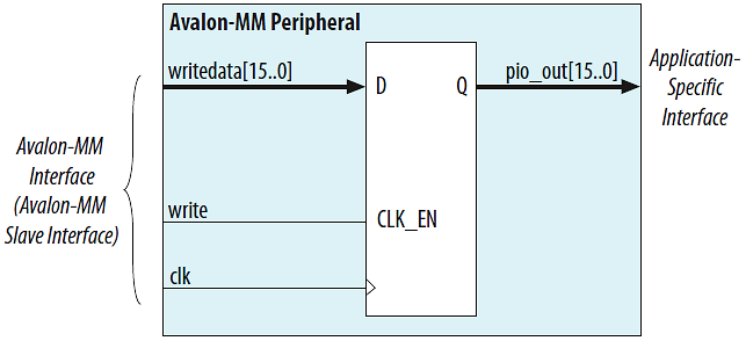

下图为16-bit通用I/O外设仅响应写请求,该组件只包含写传输所需的从信号

Avalon-MM Slave组件示例

Avalon存储器映射接口信号及属性

Avalon® Interface Specifications文档的 Table 9 列出了Avalon-MM接口的信号。注意:Avalon规范不要求所有信号都存在于一个Avalon-MM接口中,即当一个接口为Avalon-MM接口时,只包含所需要的某些信号即可。例如,对于只支持读操作(read-only)的接口,最少可只包含readdata信号;对于只支持写操作(write-only)的接口,最少可只有writedata和wrtie信号。

Avalon® Interface Specifications文档的 Table 10 列出了Avalon-MM接口信号的属性。

Avalon-MM典型的读传输和写传输

在介绍Avalon-MM典型的读写传输之前,先来介绍两个基本概念:

- 传输(Transfer) -- 传输是一个字或者一个或多个符号的数据的读或写操作。传输发生在Avalon-MM 接口与互连之间。传输需要一个或多个时钟周期才能完成。master和slave都是传输的一部分。Avalon -MM master启动传输, Avalon -MM slave作出响应。

- Master-slave pair -- 指在一个传输中涉及到master接口和slave接口。在一个传输过程中,master接口控制和数据信号遍历互连架构,并与slave接口进行交互。

下面介绍一个典型的Avalon-MM接口进行读写传输的范例,该接口包含waitrequest信号,通过将waitrequest(高电平有效)信号置为高电平,slave可将互连暂停。

通常,slave在时钟上升沿之后接收address、byteenable、read 或者write和writedata信号,在时钟上升沿之前将waitrequest置为高电平来暂停传输。当slave拉高waitrequest信号时,数据传输被延迟,此时地址线和其他控制信号保持不变。在slave将waitrequest拉低后的第一个时钟上升沿,读写传输完成。

Avalon-MM包含waitrequest的读写传输

Slave可以无期限的拉高waitrequest信号,但是在设计中必须确保slave接口不要无期限的拉高waitrequest信号,以免出现slave一直不响应、master一直等待的现象。图为使用了waitrequest的读传输和写传输。

我们来分析上图中每个数字标注的时刻,Avalon-MM总线上的操作:

1. clk上升沿后,address、byteenable、read信号被置为有效;slave将waitrequest拉高,暂停数据传输。

2. clk上升沿,waitrequest被master采样;由于waitrequest有效,此时处于等待状态(wait-state),address、read和byteenable保持不变。

3. slave 在clk上升沿之后将waitrequest置为低电平,之后将readdata、responese置为有效。

4. clk上升沿,master检测到waitrequest拉低,捕获readdata、response,读数据传输完成。

5. clk上升沿后,address、writedata、byteenable和write信号被置为有效;slave将waitrequest拉高,暂停数据传输。

6. slave 在clk上升沿之后将waitrequest置为低电平。

7. clk上升沿,slave捕获到writedata,写数据传输完成。

地址对齐

互连仅支持地址对齐的访问方式。Master只能发送其数据位宽倍数的地址。Master可通过拉低byteenable_n的某几位来写入部分数据。例如,向地址2写入2字节的数据时,byteenable_n = 4’b1100。

Avalon-MM寻址

动态地址对齐(Dynamic bus sizing)在不同数据宽度的master-slave对传输期间管理数据。从机数据在主机地址空间中以连续字节的方式对齐。

如果master的数据宽度大于slave的数据宽度,mster地址空间中的字会映射到slave地址空间中的多个位置。例如,32位的master读取16位的slave时,会在slave端进行两次读传输,这两次读传输的地址是连续的。

如果master的数据宽度小于slave的数据宽度时,互连会管理slave的各个字节通道。当master从slave读取数据时,互连只会把相应的字节通道的数据传输给master。当master向slave写数据时,互连会自动将相应字节通道的byteenables信号置为有效。

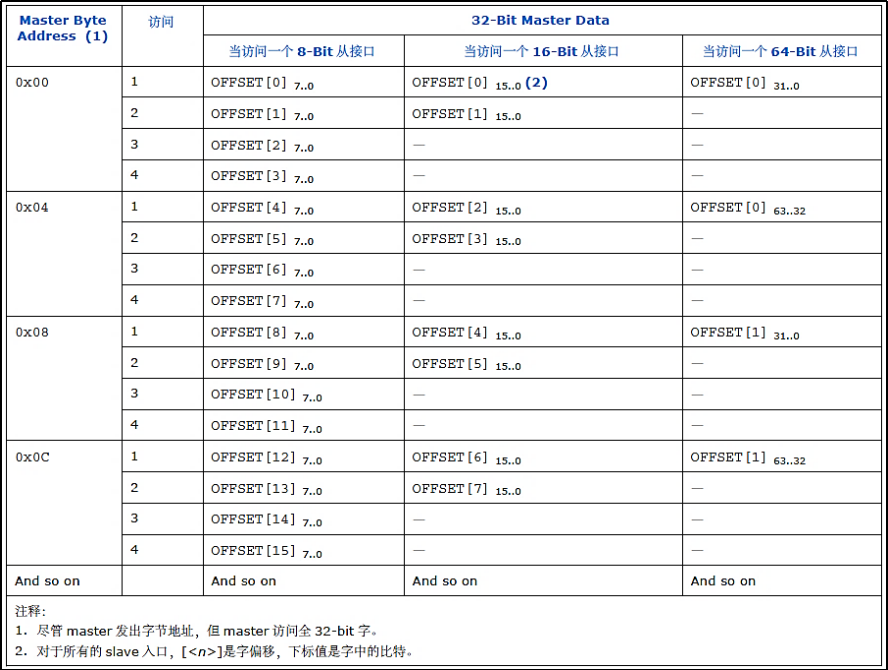

Slave的数据宽度必须是8、16、32、64、128、256、512 或者1024位。下表列出了32位的master按字访问不同位宽的slave数据时是如何与master对齐的,OFFSET[N]表示slave地址空间字的偏移量。

表1.9

动态地址对齐的Master-Slave之间的地址映射

Avalon Conduit接口

Avalon Conduit接口是那些不适合任何其他Avalon类型的单个/多个信号的集合,使用该接口可以将信号导出到顶层SOPC系统,这样就可以将它连接到设计的其他模块。一个Avalon Conduit接口可以包括输入、输出和双向信号,并且一个模块/组件可以有多个Avalon Conduit接口。管道(Conduit)接口通常用于驱动片外器件信号,比如SDRAM的地址、数据和控制信号线,如下图所示。

Avalon Conduit接口示例

Avalon conduit接口的信号可以是任意的,并且该接口的信号没有任何属性。

表1.10 Conduit接口信号

|

信号 |

宽度 |

方向 |

描述 |

|

"any" |

"n" |

Input, Output, Bidirectional |

管道接口由一个或多个任意宽度的输入/输出/双向信号组成。管道接口的信号是任意的。您可以在一个Platform Designer(Standard)系统中连接兼容的Conduit接口,但前提是角色和宽度要匹配,方向要相反。 |

往期推荐阅读:

浙公网安备 33010602011771号

浙公网安备 33010602011771号