1. Quartus 工程创建

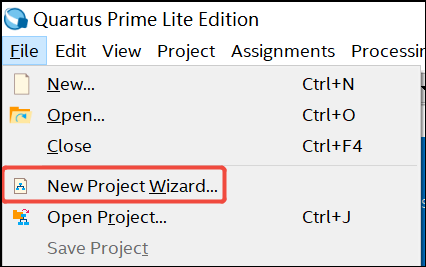

2. 点击Quartus工具的File——New Project Wizard:

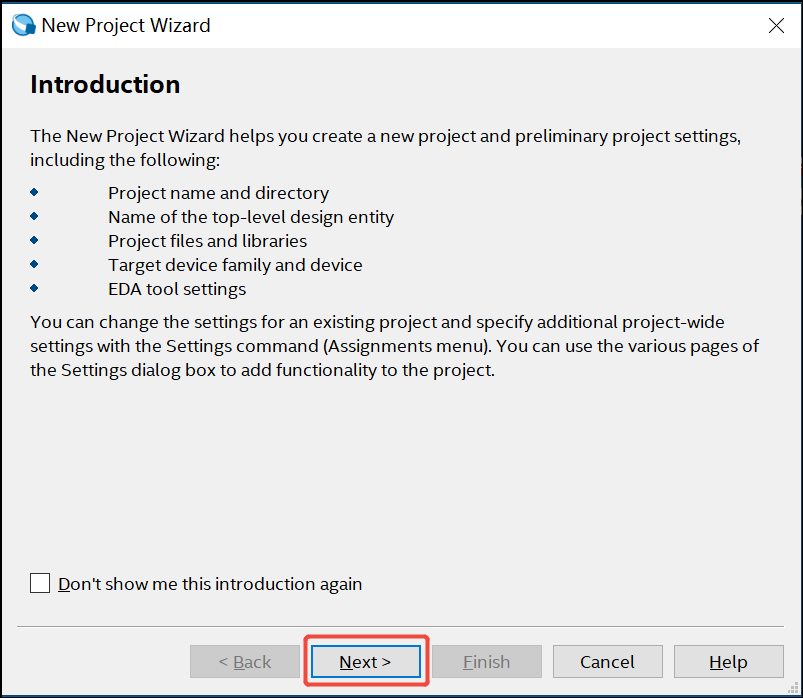

3. 弹出如下对话框时点击Next:

4. 在你的工作目录创建一个DE10_Standard_ADC文件夹:

5. 设置工程路径,指定到你刚才创建的DE10_Standard_ADC文件夹下,然后给工程命名DE10_Standard_ADC, 点击Next:

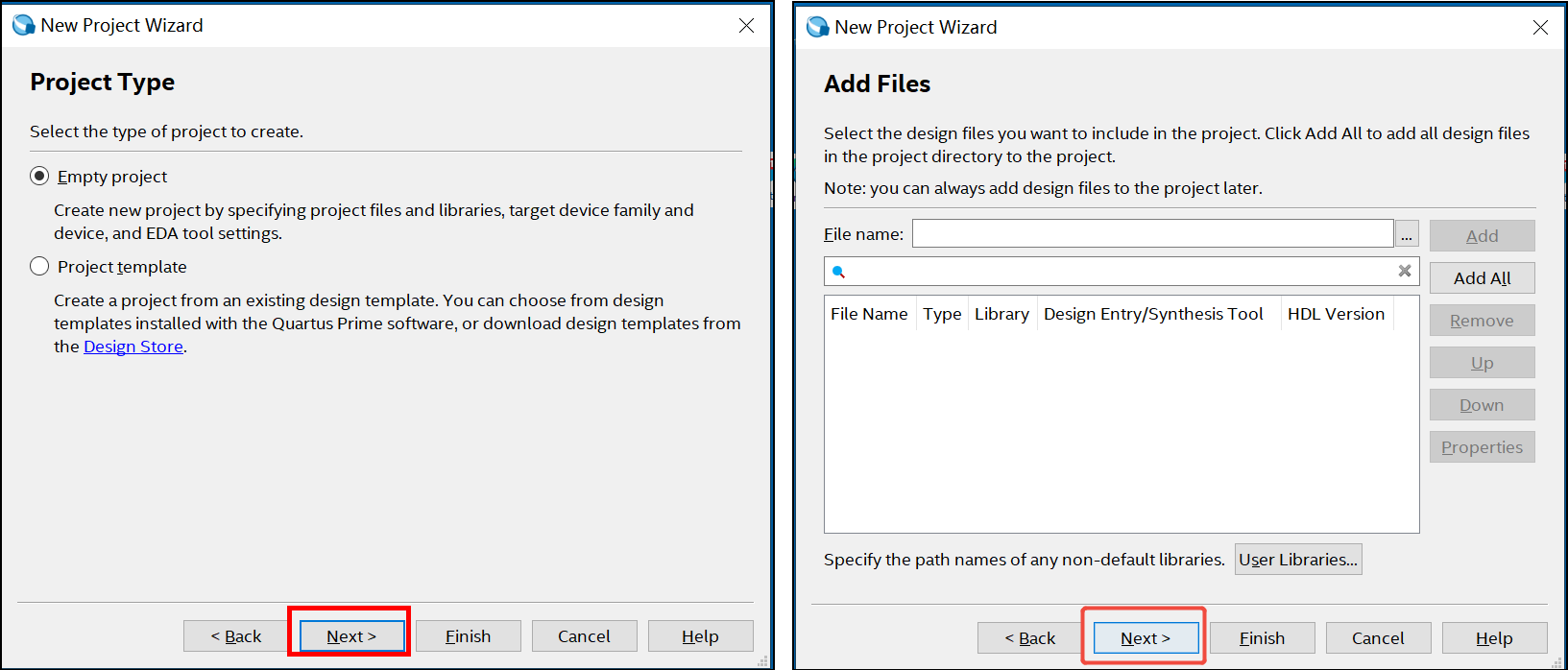

6. 点击Next:

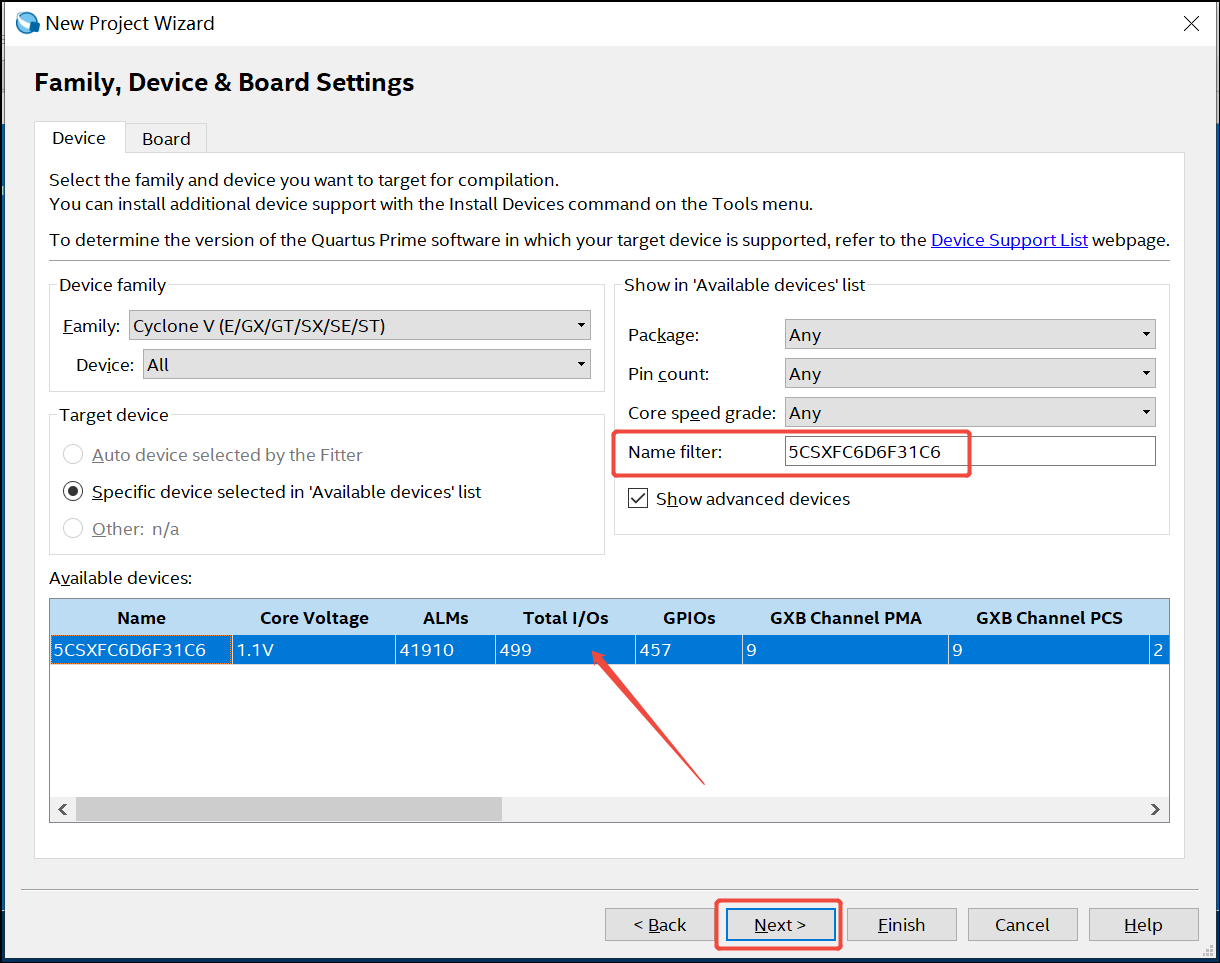

7. 在Name Filter处键入你的开发板对应的FPGA器件型号,从而在Avaliable devices窗口筛选出你要的器件(比如DE10-Standard开发板对应的FPGA 器件是5CSXFC6D6F31C6),点击该器件,然后点击Next:

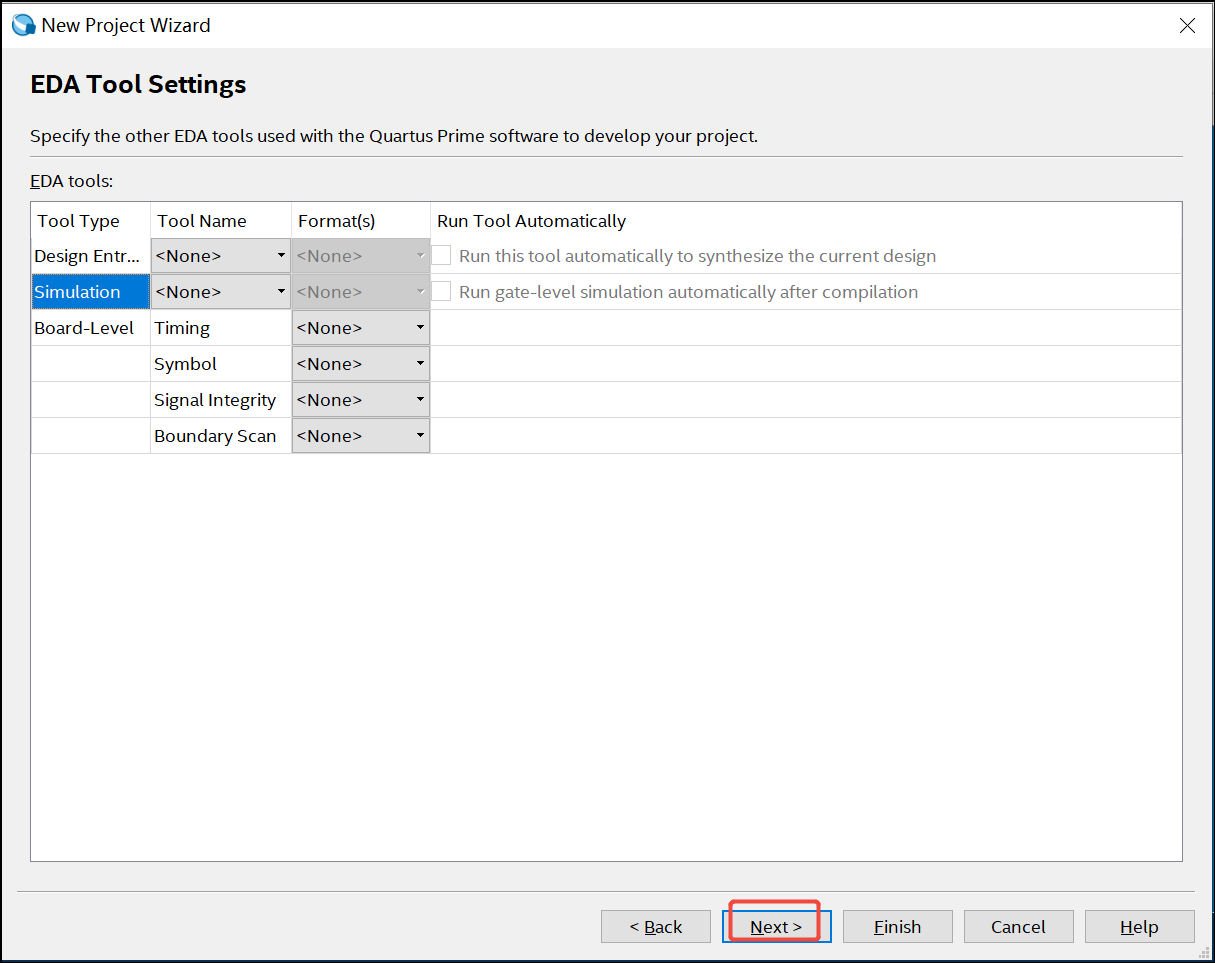

8. 继续点击Next:

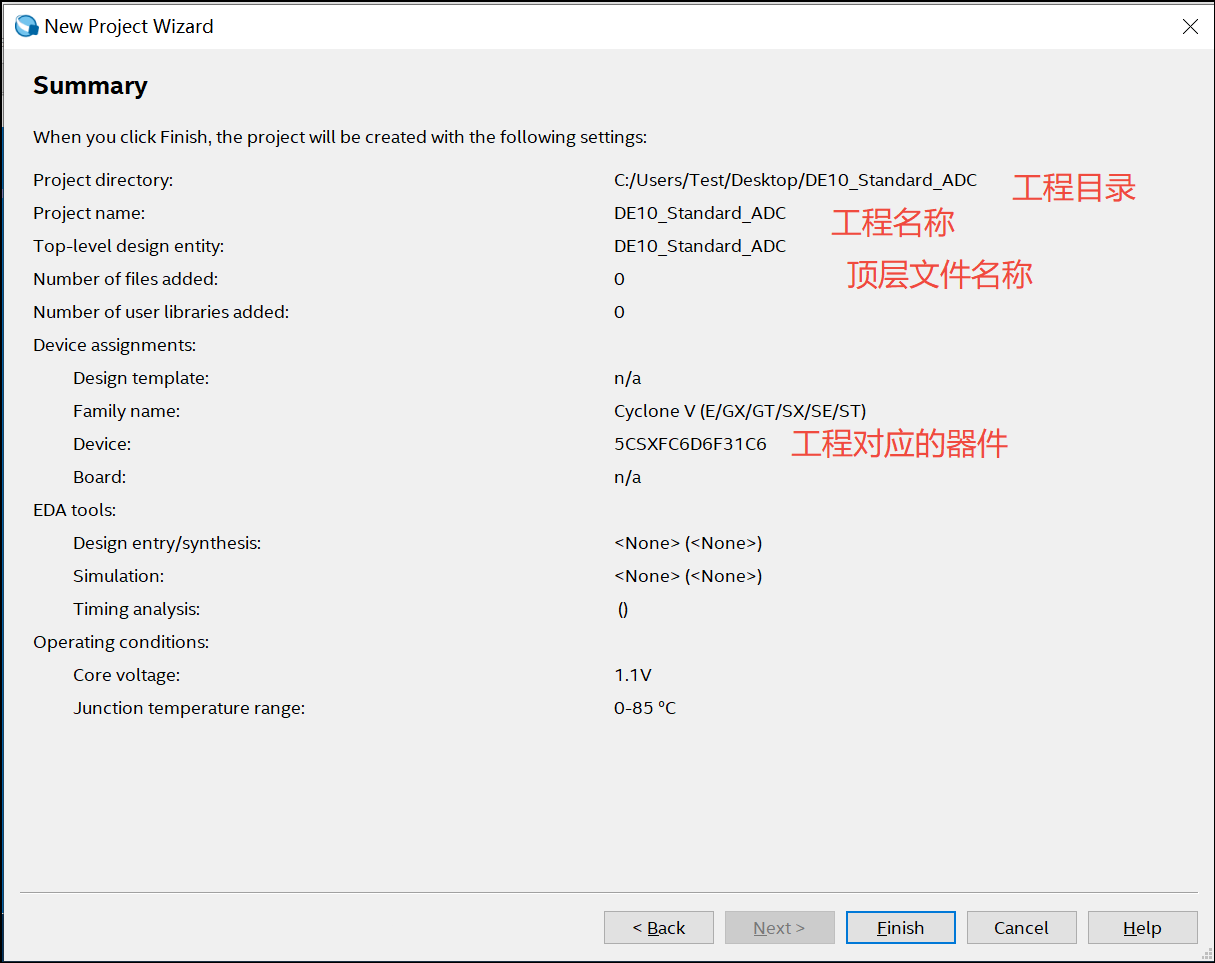

9. 这时候汇总出一个工程创建的报告如下,点击Finish完成工程创建:

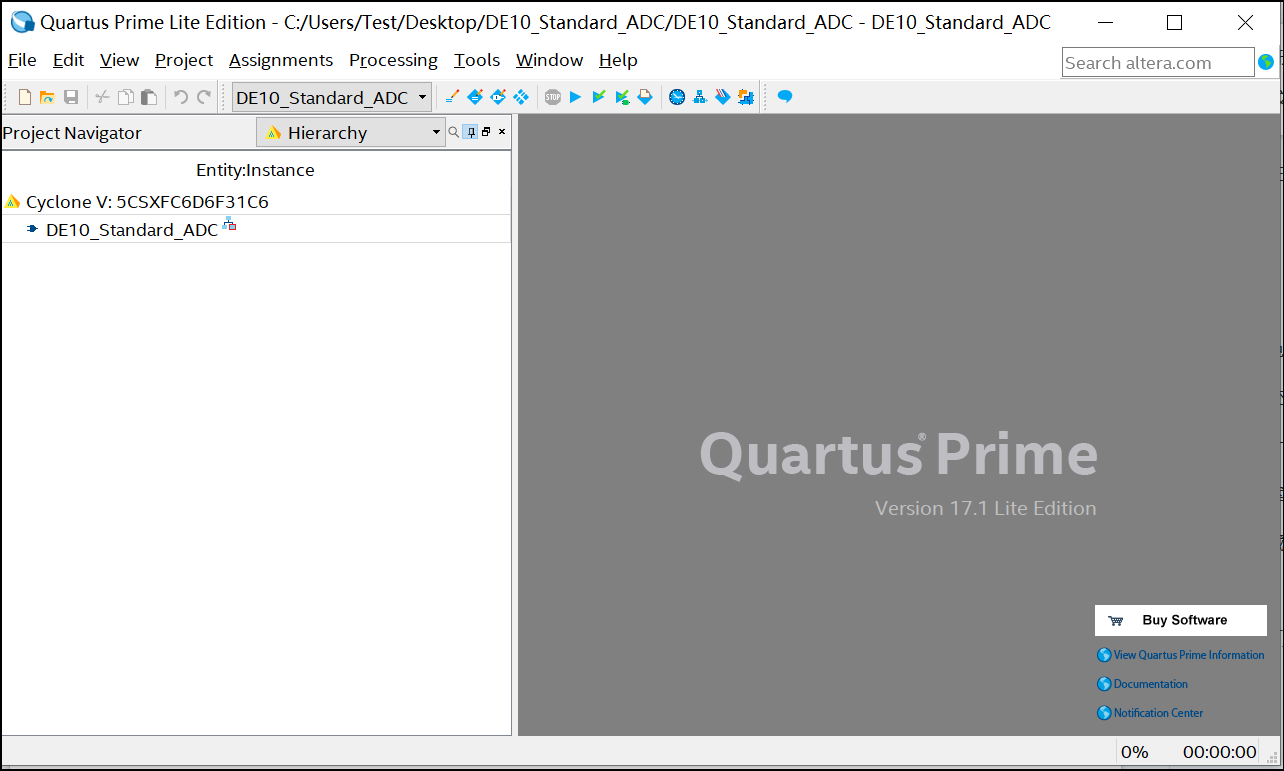

10. 工程创建完成后界面如下:

11. 按照文章 9-LTC2308控制器设计——自定义IP(Avalon MM) 完成自定义IP(adc_ltc2308)的封装。

接下来开始搭建Platform Designer系统。

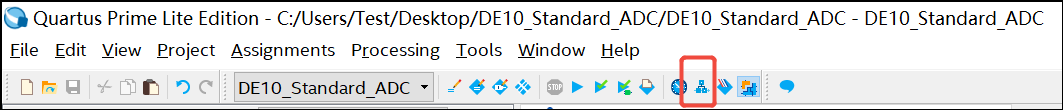

12. 点击如下Platform Designer 按钮:

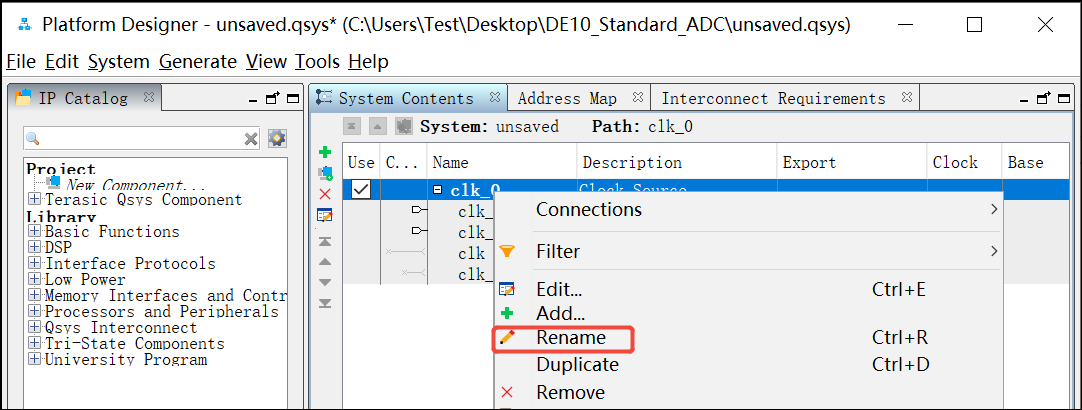

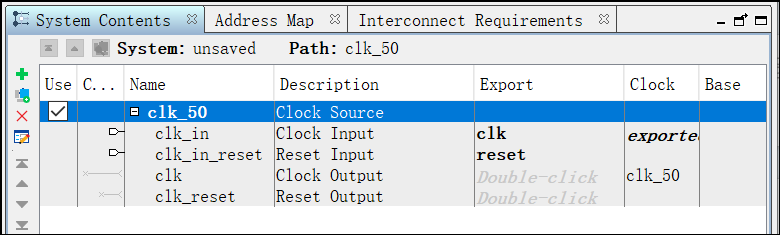

13. 右击clk_0组件,选择Rename,将组件clk_0命名为clk_50:

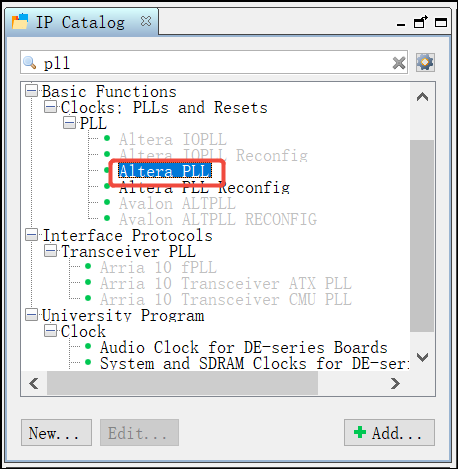

14. 在IP Catalog处键入pll搜索找到Altera PLL IP,双击打开它的配置界面:

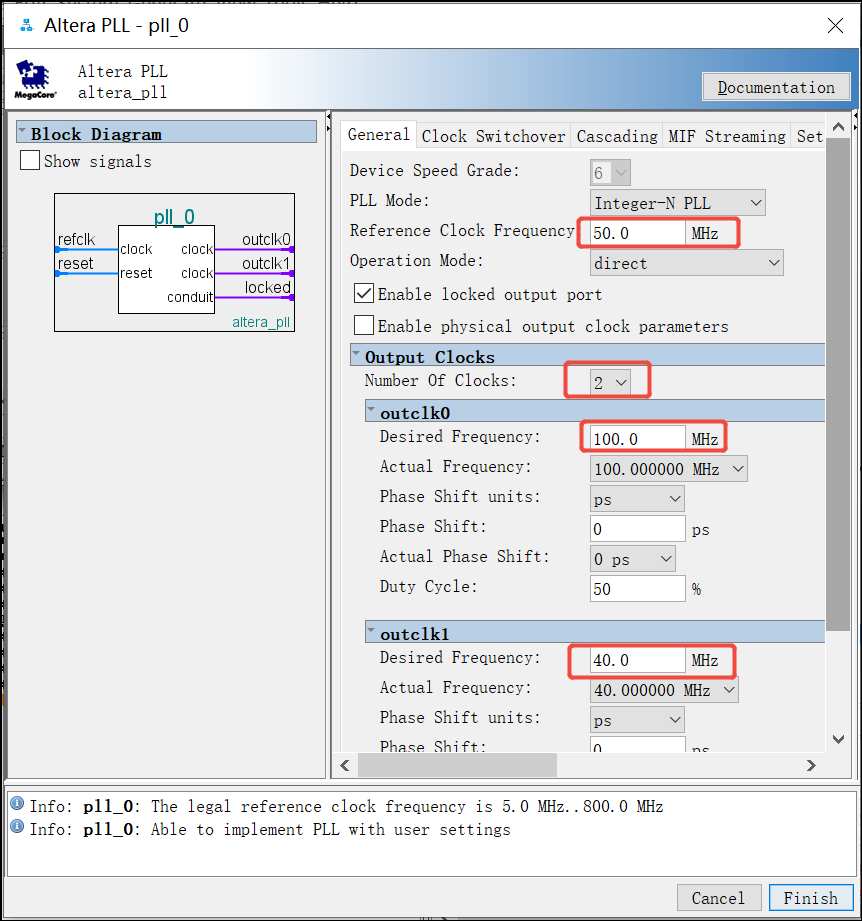

15. 设置 Reference Clock Frequency 为50MHz, 输出2路时钟,一路是100M, 用于各个模块的工作时钟,一路是40MHz, 用于输出给LTC2308器件,最后点击Finish完成PLL 模块的设置:

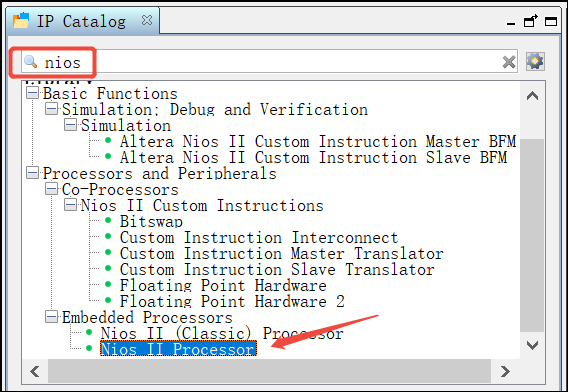

16. 在IP Catalog处键入nios 搜索找到Nios II Processor,双击打开它的配置界面:

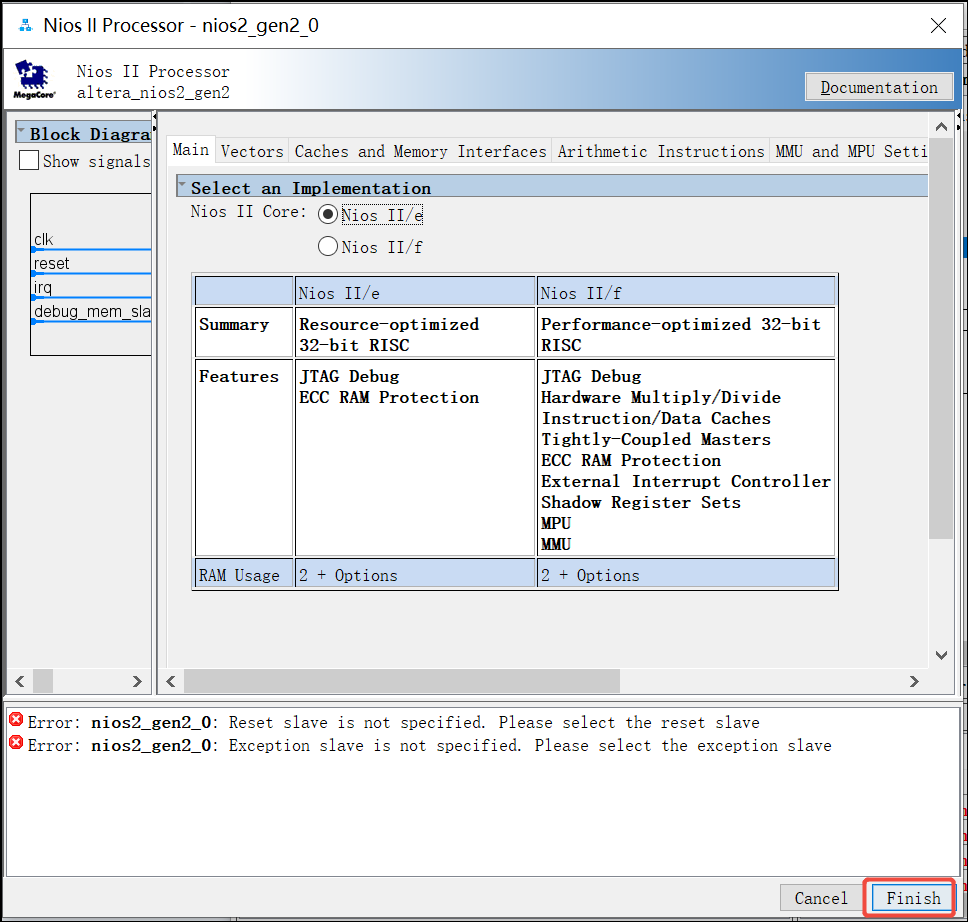

17.如果是免费版本的Quartus Prime( 即Lite版本), 请选择Nios II/e,然后点击Finish结束Nios II IP的设置:

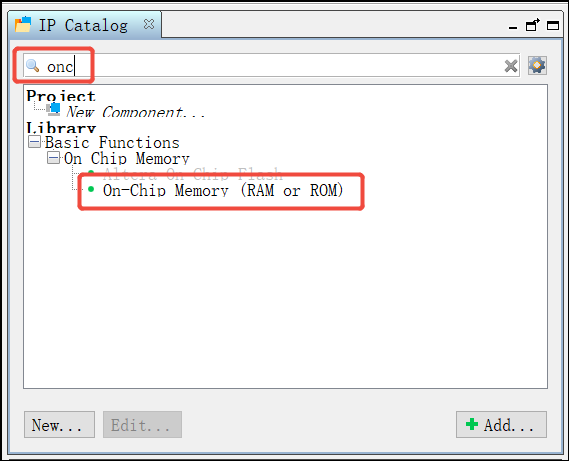

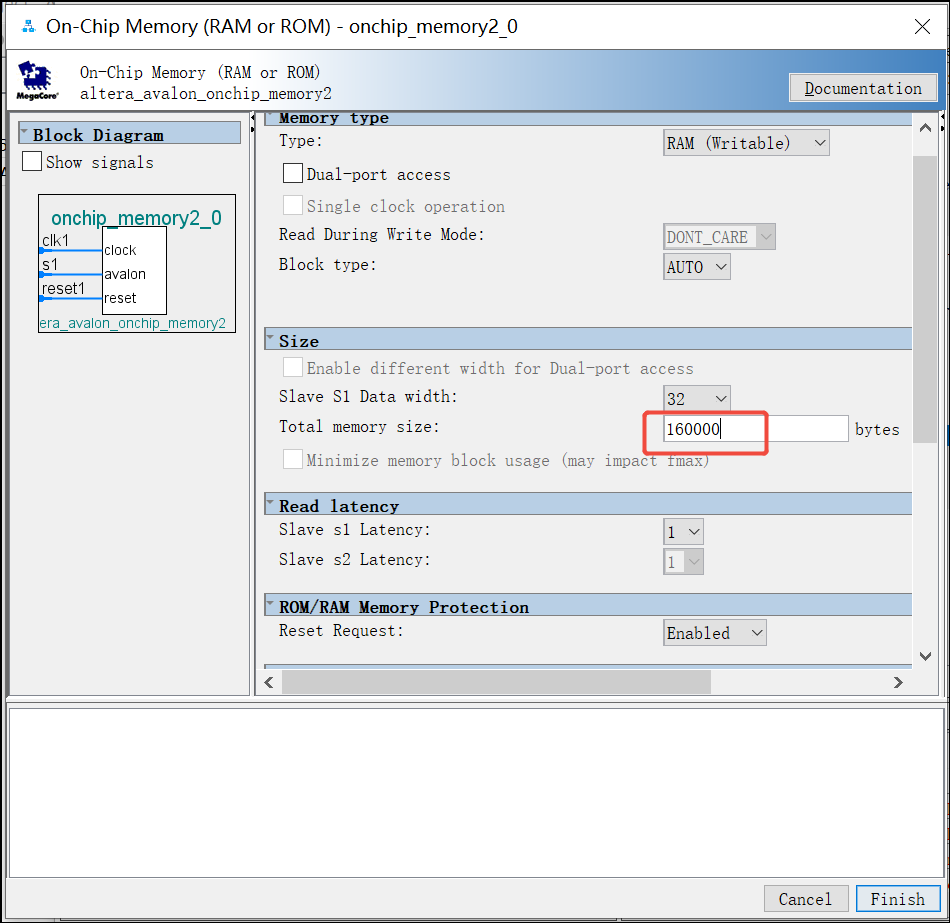

18. 在IP Catalog处键入onc 搜索找到On-Chip Memory,双击打开它的配置界面:

19. 数据宽度保持32bit, Memory Size设置160000字节, 然后点击Finish结束该IP的设置:

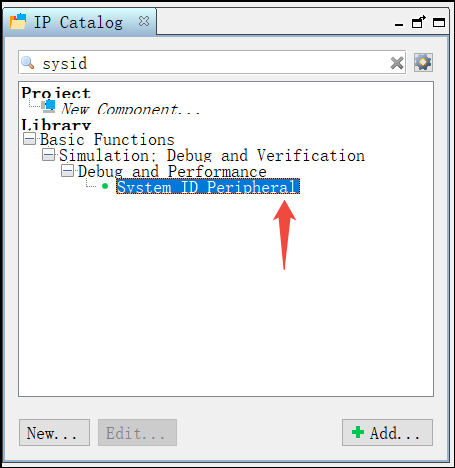

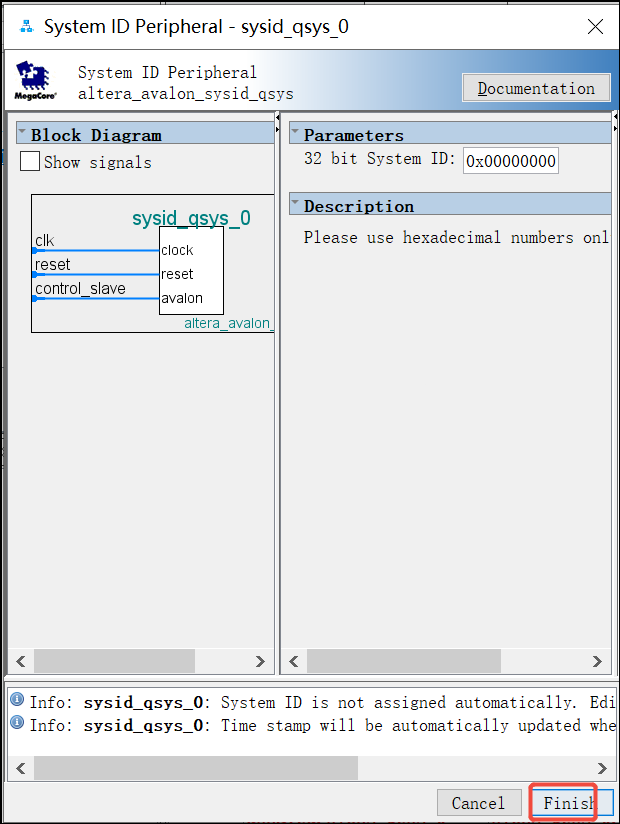

20. 在IP Catalog处键入sysid搜索找到System ID Peripheral IP,双击打开它的配置界面:

21. 保持System ID Peripheral IP的默认设置不变,点击Finish:

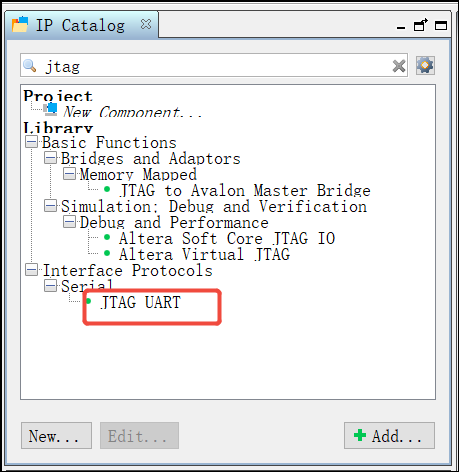

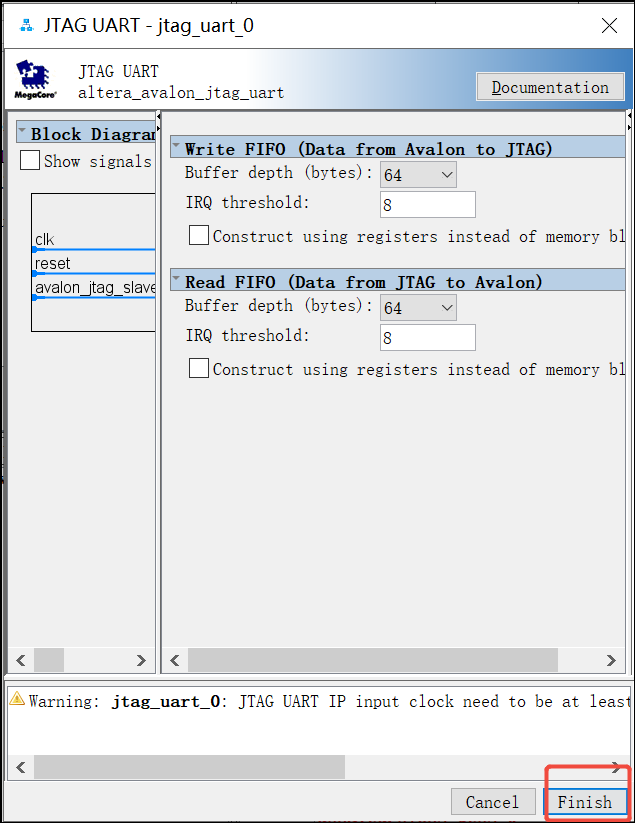

22. 在IP Catalog处键入jtag搜索找到JTAG UART IP,双击打开它的配置界面:

23.保持JTAG UART IP的默认设置不变,点击Finish:

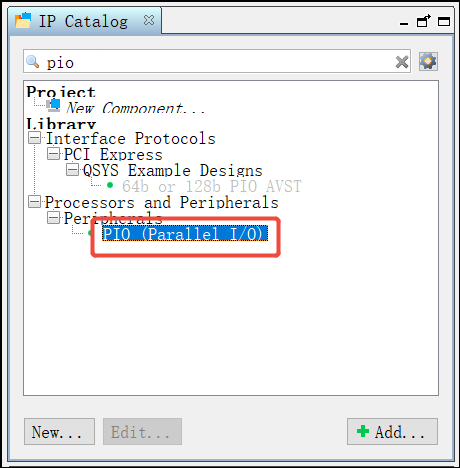

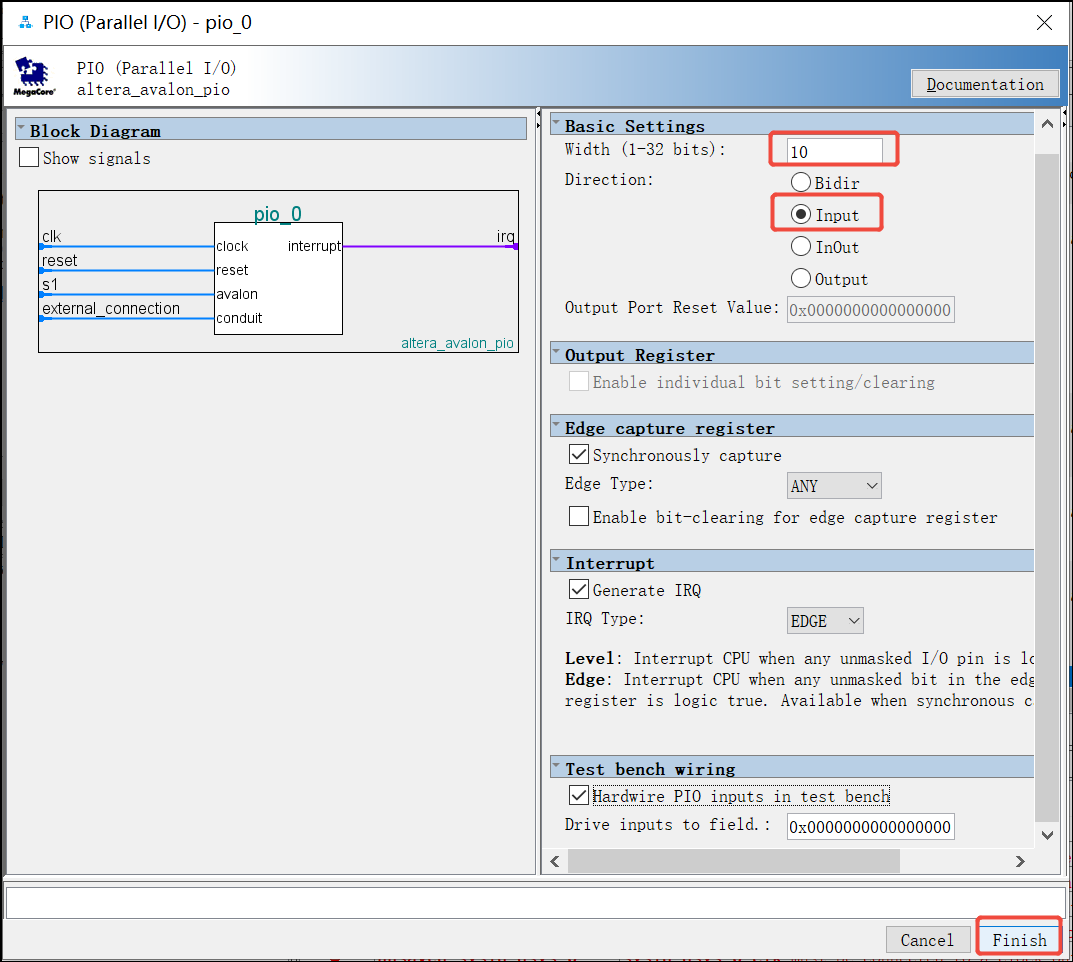

24. 在IP Catalog处键入pio搜索找到PIO(Parallel I/O) IP,双击打开它的配置界面:

25. 将PIO IP 的位宽设置为10, Direction设置为Input,然后点击Finish结束PIO IP 的设置:

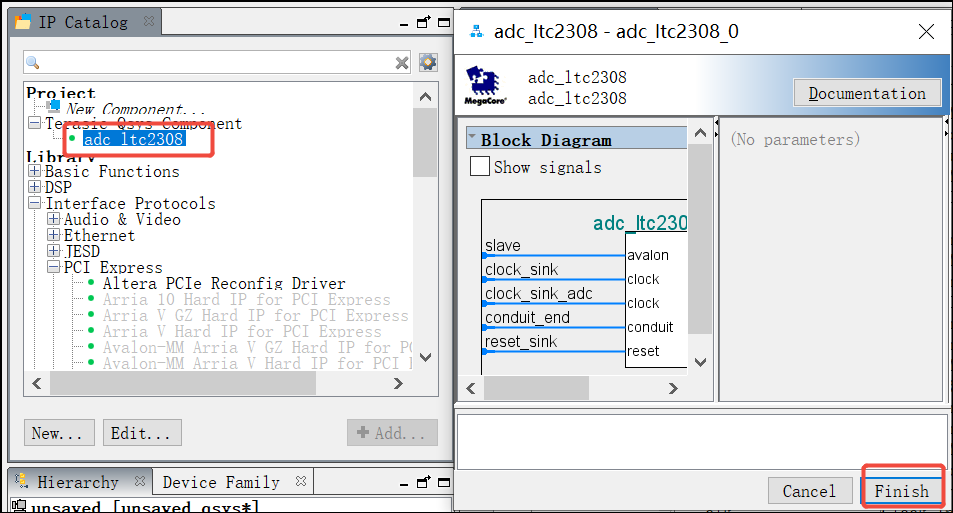

26. 双击IP Catalog 里面的自定义IP adc_ltc2308, 然后点击Finish:

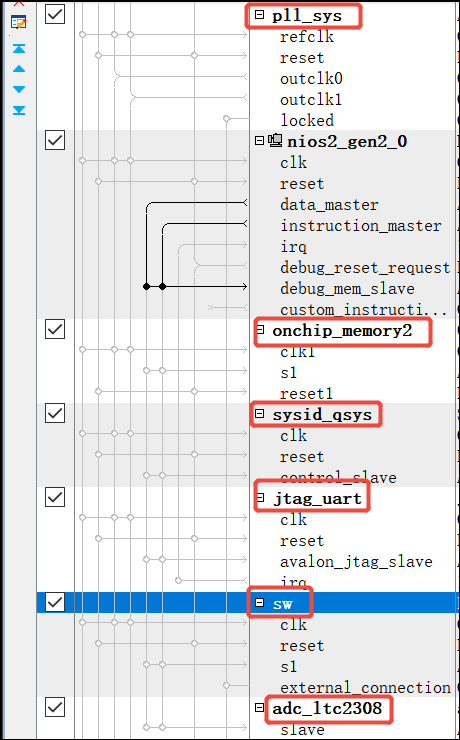

27. 接下来将这些模块名称重命名如下:

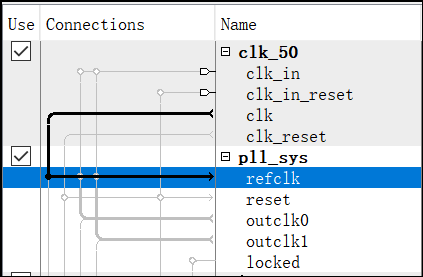

28. IP添加完成以后就可以进行IP之间的互连。Platform Designer 界面已经把可能互连的信号端口用暗浅色线相连,用户只需将鼠标放到两个端口相连的小圆圈处点击一下,就完成了真正的端口相连。首先是连接时钟网络。clk_50 的clk端口输出50MHz给PLL 模块 作为参考时钟,互联关系如下黑色粗线连接:

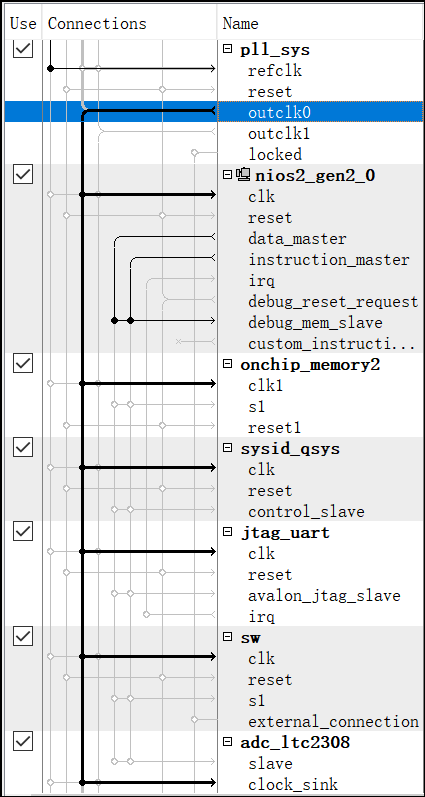

29. 然后是PLL 模块的outclk0 输出的100MHz时钟给其他所有模块,互连情况如下粗黑线:

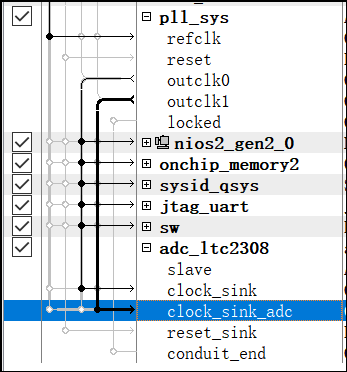

30. 接下来是PLL 模块的outclk1 输出的40MHz时钟给LTC2308,连接情况如下粗黑线:

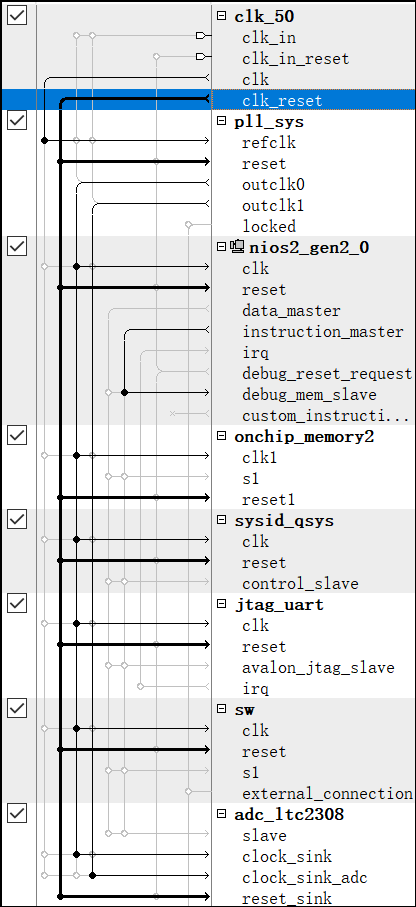

31. 将所有模块的复位端口都连接到clk_50 模块的复位端口,连接情况如下粗黑线:

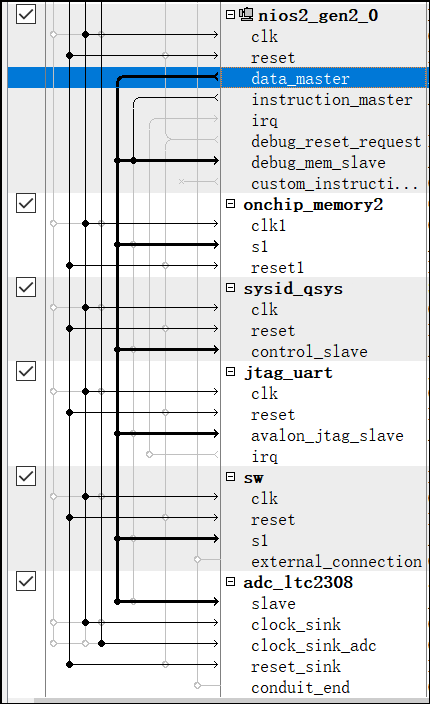

32. 将所有模块的slave端口都连接到nios2_gen2_0模块的data_master端口,连接情况如下粗黑线:

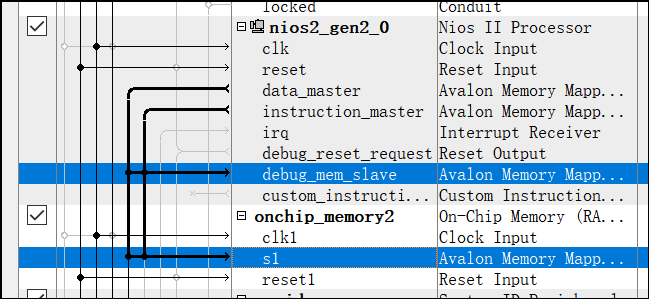

33. 将nios2_gen2_0的数据总线、指令总线跟debug_mem_slave和onchip_memory2的slave总线相连如下:

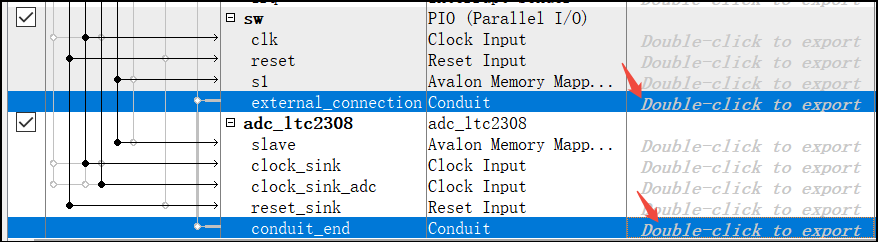

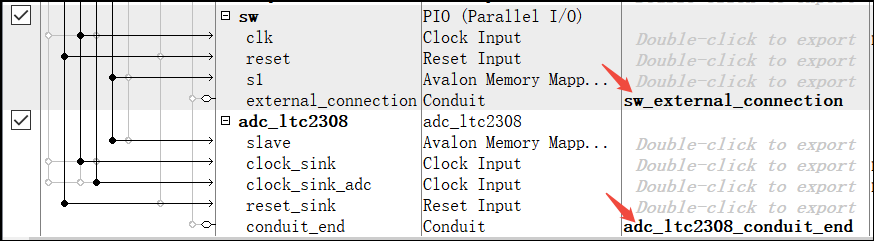

34. 双击pio 模块conduit_end端口对应的Export列(上面显示Double-click to export)将该端口导出(双击后显示pio_external_connection),同样的,双击adc_ltc2308模块conduit_end端口对应的Export列将其端口导出(双击后显示adc_ltc2308_conduit_end):

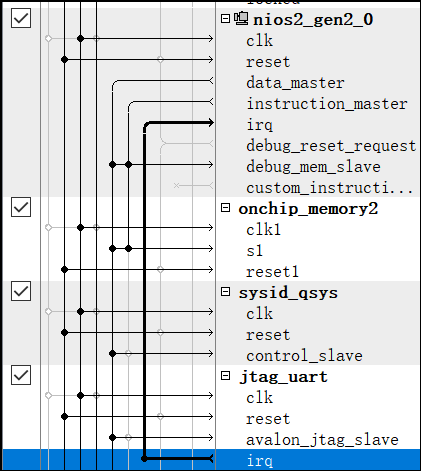

35.将jtag_uart的中断端口连接到nios2_gen2_0 的irq端口:

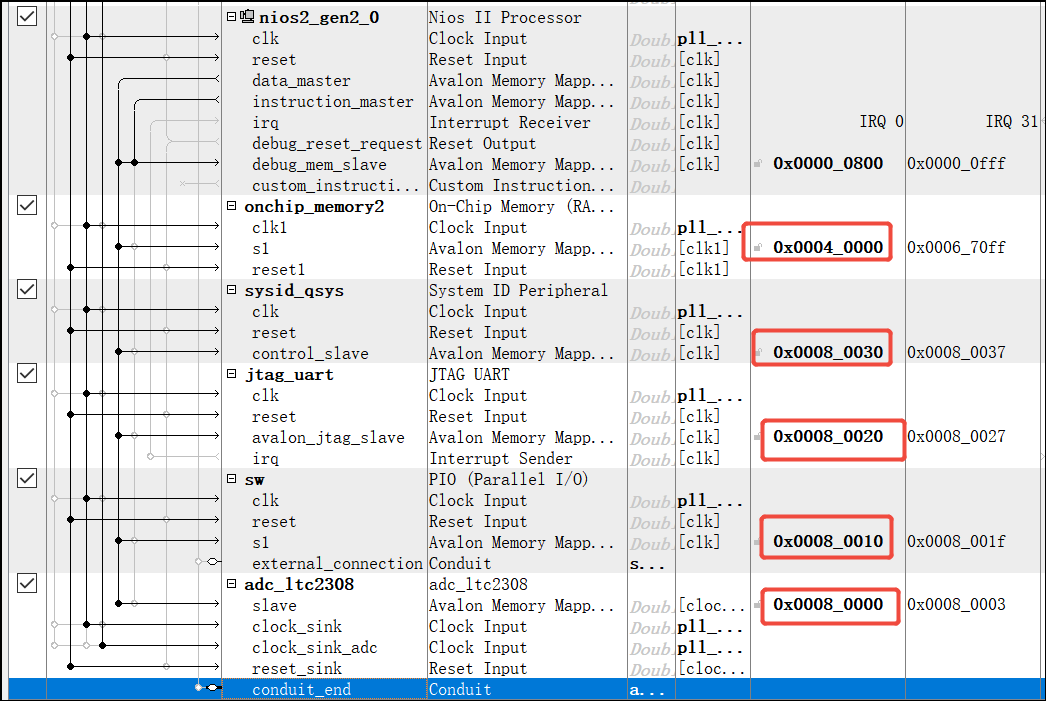

36. 然后是地址分配。双击每个模块的Base列的地址即可修改该模块的基地址:

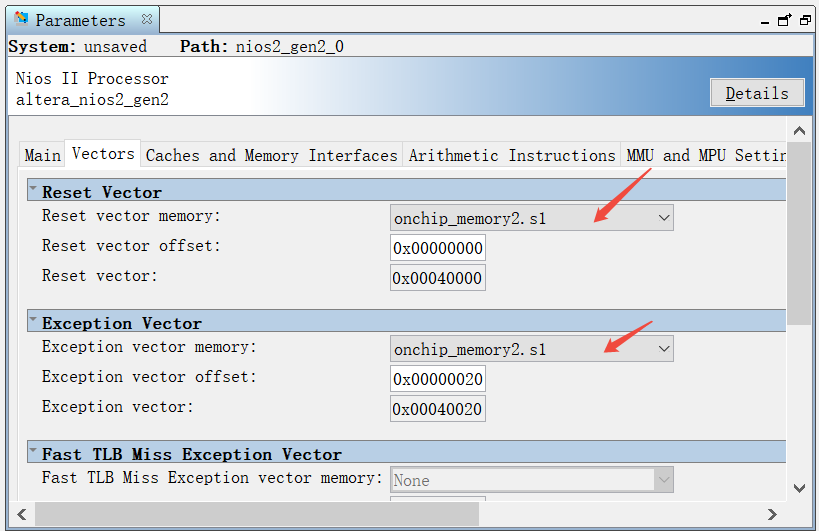

37.设置nios2_gen2_0的Reset vector memory 为onchip_memory2.s1,以及设置Exception vector memory 也为onchip_memory2.s1:

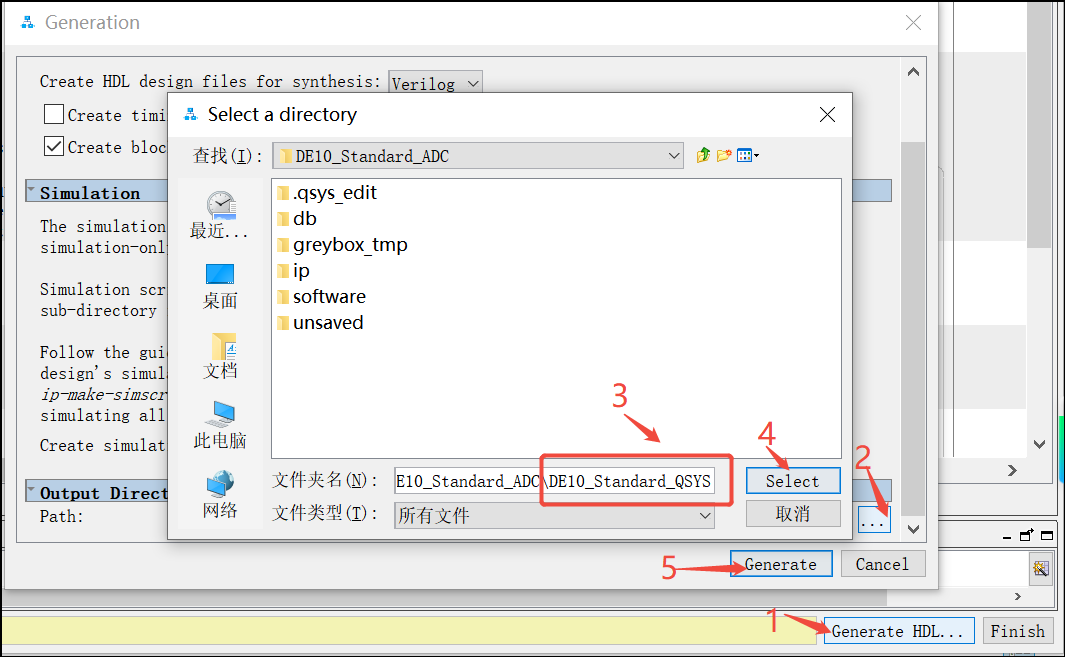

38. 点击Generate HDL...,然后在Path处点击...,这里直接将文件生成的路径设置到~DE10_Standard_ADC\DE10_Standard_QSYS,然后点击Select,然后点击Generate:

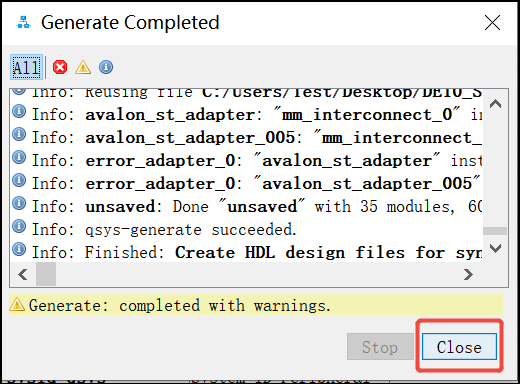

39. 点击Close:

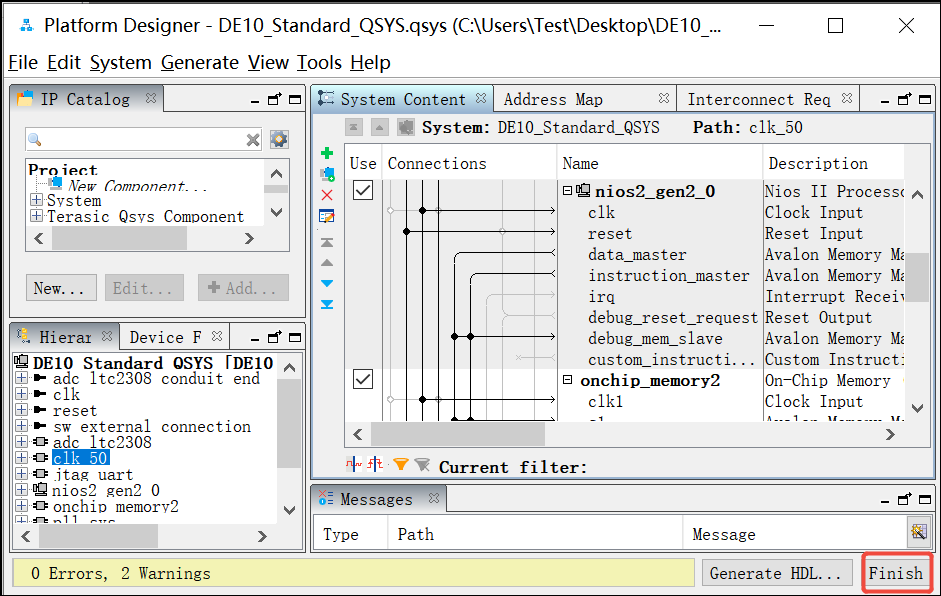

40. 点击Finish:

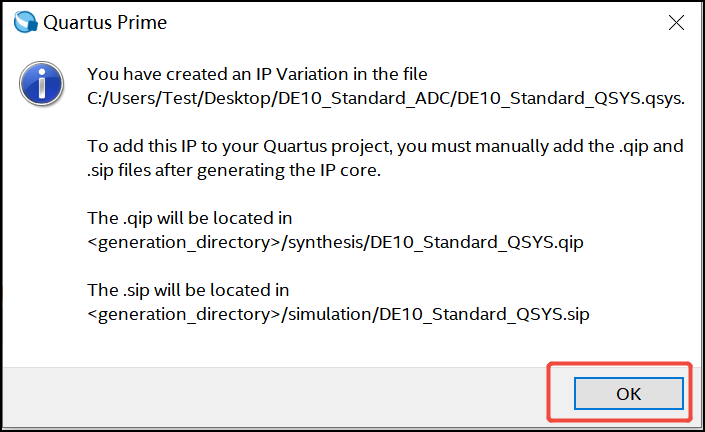

41. 点击OK:

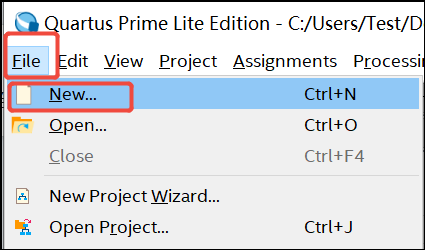

42. 接下来开始创建top-level文件,点击File——New:

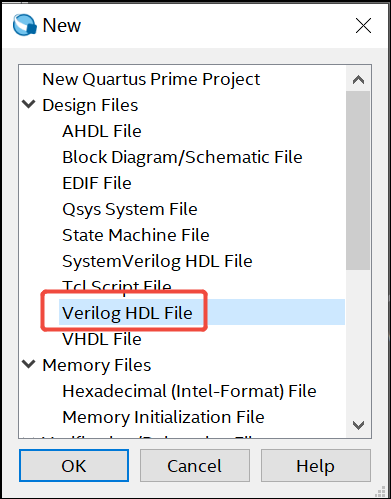

43. 选择Verilog HDL File, 然后点击OK:

44. 然后弹出如下界面:

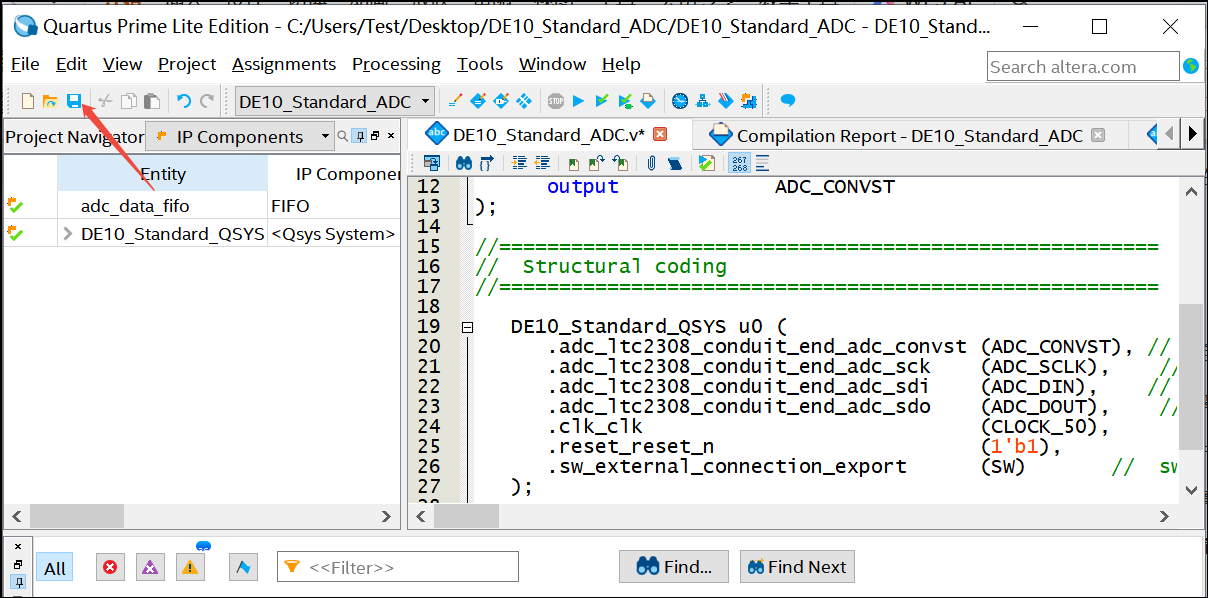

45. 将如下代码拷贝到该新建的.v文件里面:

module DE10_Standard_ADC(

///////// CLOCK /////////

input CLOCK_50,

///////// SW /////////

input [ 9: 0] SW,

///////// ADC /////////

output ADC_SCLK,

input ADC_DOUT,

output ADC_DIN,

output ADC_CONVST

);

//=======================================================

// Structural coding

//=======================================================

endmodule

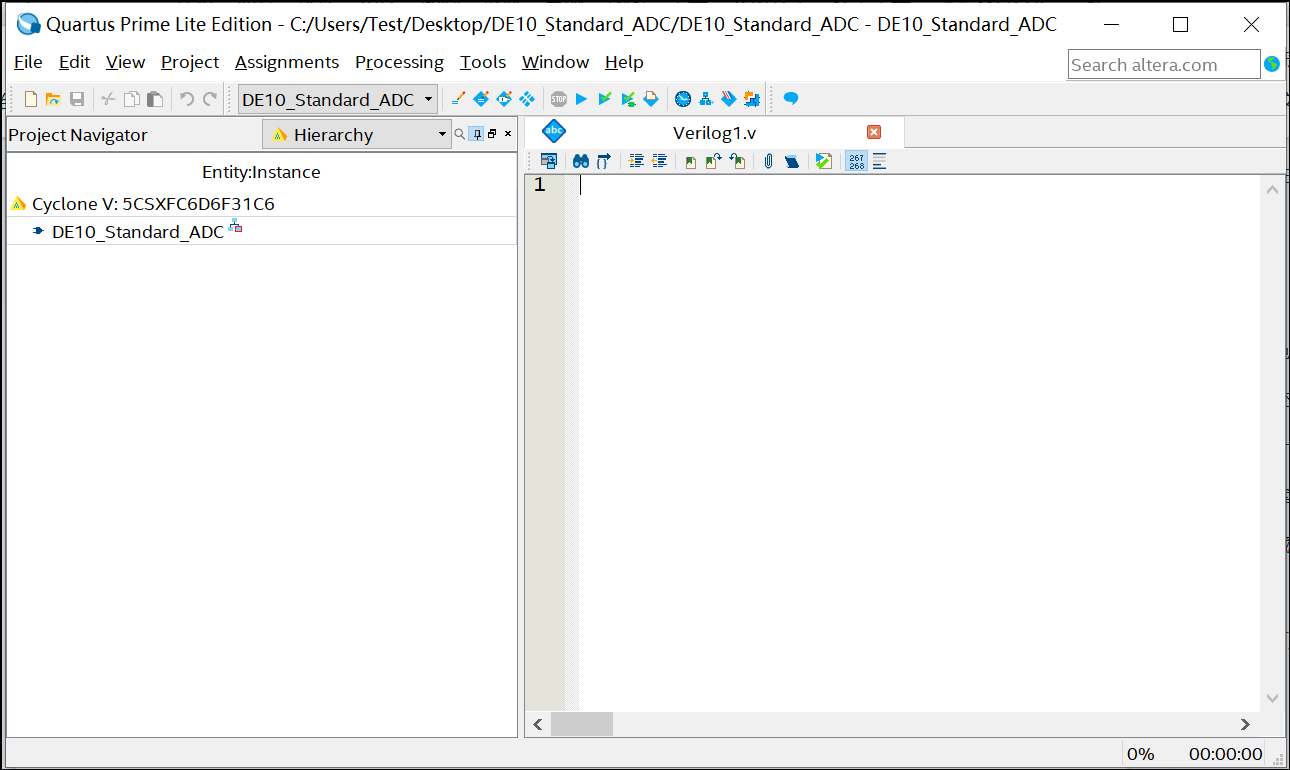

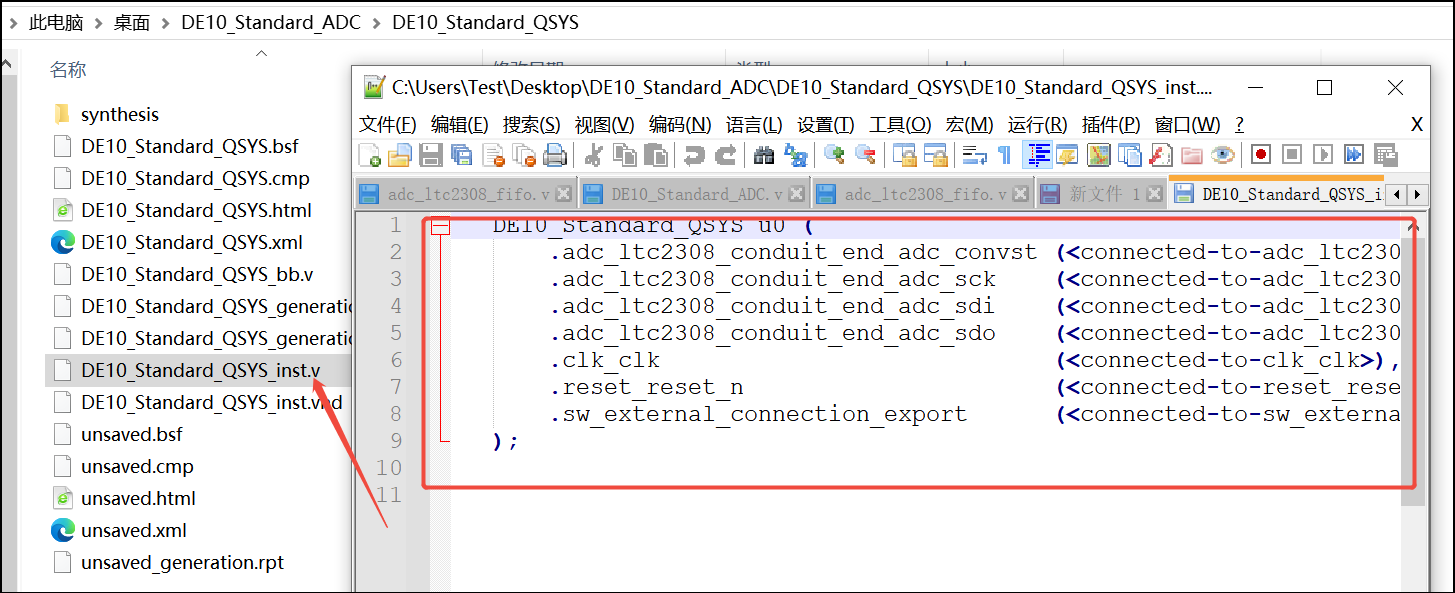

46. 打开~DE10_Standard_ADC\DE10_Standard_QSYS\DE10_Standard_QSYS_inst.v,将文件中的内容拷贝到刚才新建的.v文件里面:

47.然后修改代码(将FPGA对外的端口与FPGA内部模块信号连接起来)如下:

DE10_Standard_QSYS u0 ( .adc_ltc2308_conduit_end_adc_convst (ADC_CONVST), // adc_ltc2308_conduit_end.adc_convst .adc_ltc2308_conduit_end_adc_sck (ADC_SCLK), // .adc_sck .adc_ltc2308_conduit_end_adc_sdi (ADC_DIN), // .adc_sdi .adc_ltc2308_conduit_end_adc_sdo (ADC_DOUT), // .adc_sdo .clk_clk (CLOCK_50), // clk.clk .reset_reset_n (1'b1), // reset.reset_n .sw_external_connection_export (SW) // sw_external_connection.export );

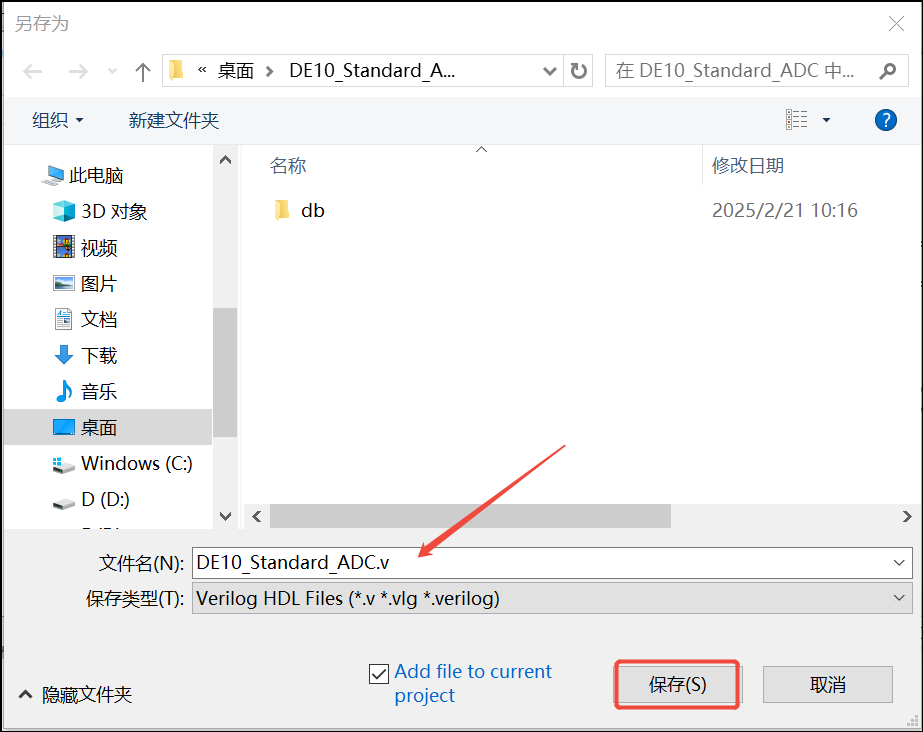

48. 点击保存:

49. 保存时保持文件名称默认是DE10_Standard_ADC:

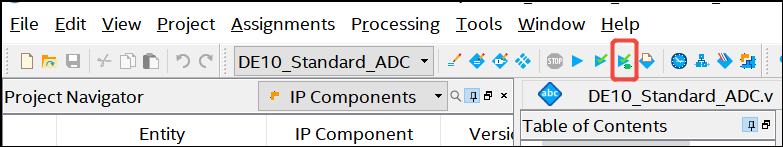

50. 点击分析与综合:

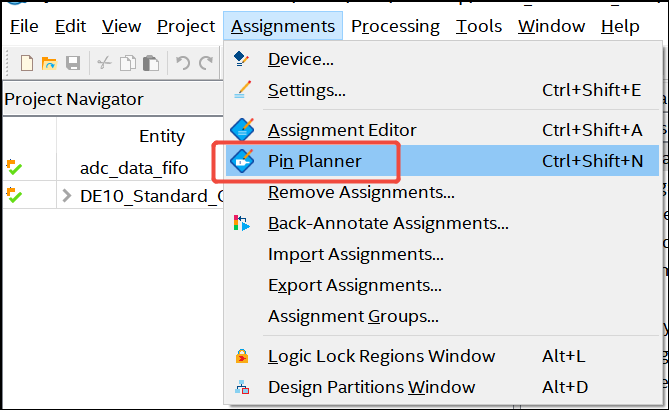

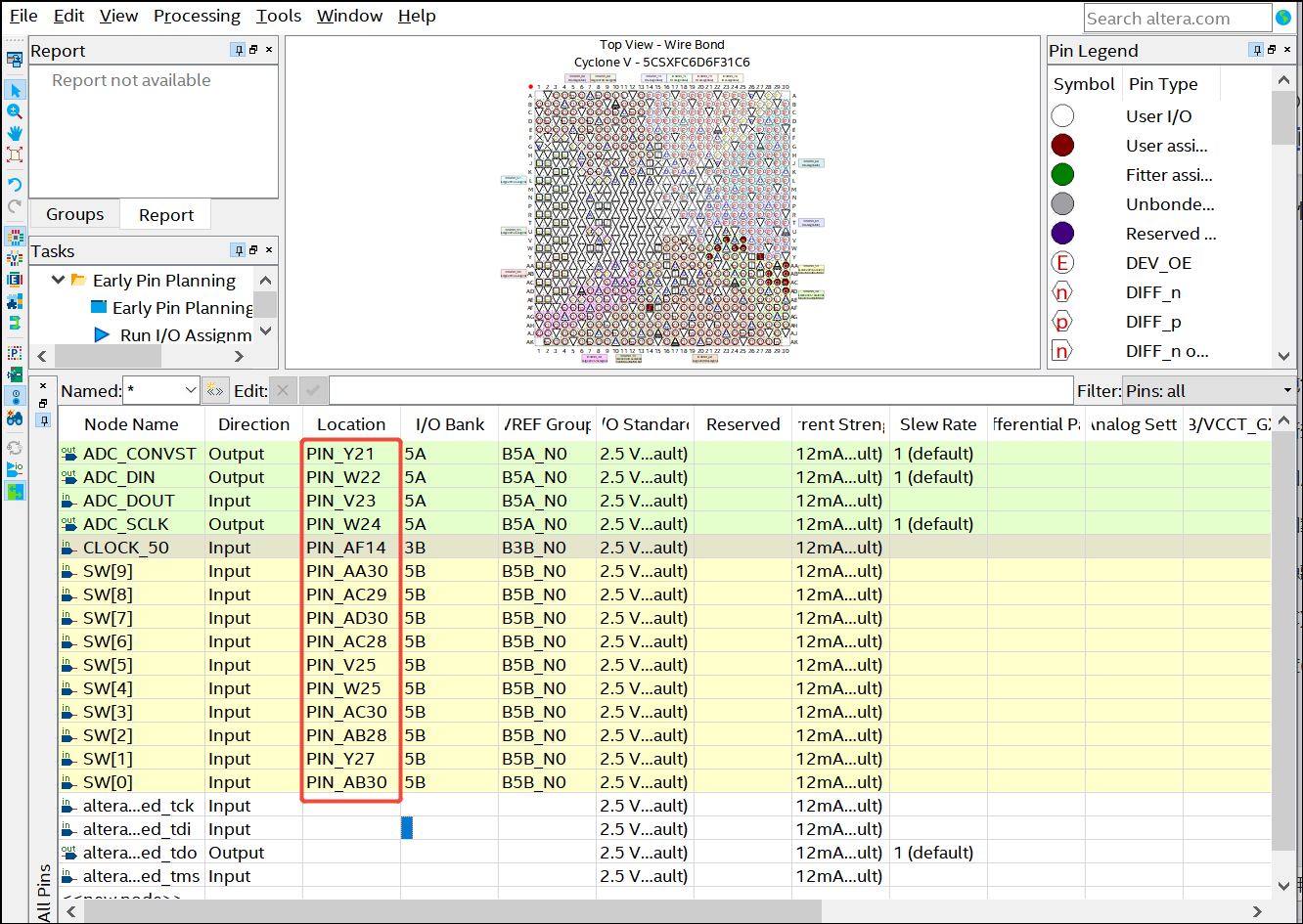

51. 点击Quartus的菜单Assignments——Pin Planner来打开引脚分配的界面:

52. 引脚分配请参考友晶官方发布的DE10-Standard_User_manual.pdf手册,具体的引脚分配如下:

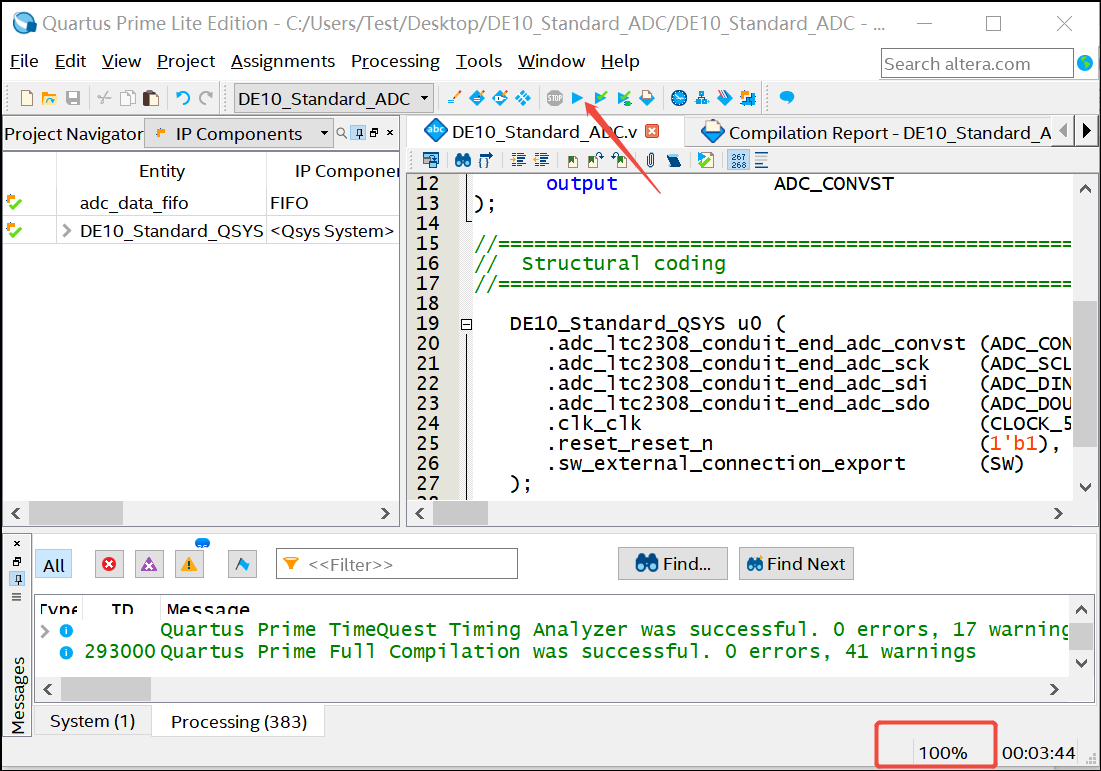

53. 点击编译按钮进行工程编译,编译成功后页面最下面会显示100%:

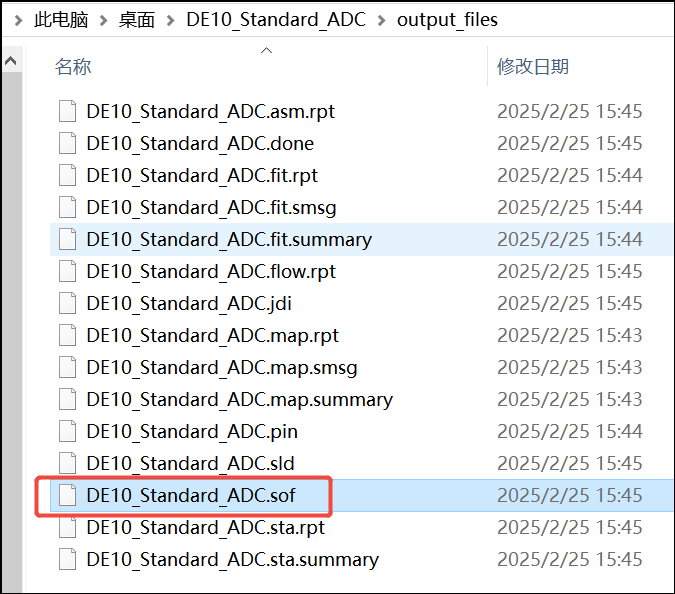

54. 最后在Quartus工程目录下可以看到生成的sof文件:

往期推荐阅读:

浙公网安备 33010602011771号

浙公网安备 33010602011771号