【ARM CoreLink 系列 3.2 -- CCI-400,CCI-500, CCI-550 差异】

CCI-400 和 CCI-500 差异

ARM 的 CCI(Cache Coherent Interconnect)系列产品是用于多核处理器之间的高性能缓存一致性互连。CCI-400 和 CCI-500 是该系列中的两种设计,它们旨在允许多个处理器核心和其他资源(如GPU、DMA控制器等)有效地共享数据,同时保持内存内容的一致性。CCI-400 和 CCI-500 有着不同的特性和性能指标,它们之间的主要区别如下:

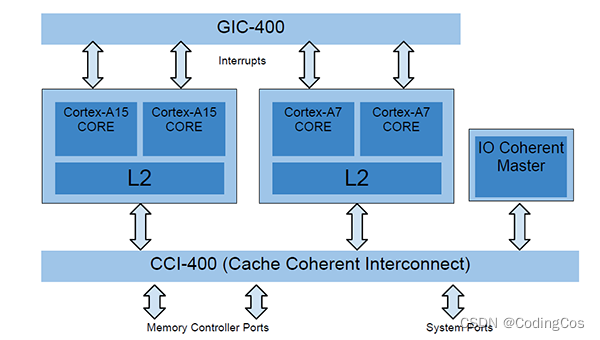

ARM CCI-400

CCI-400 是较早的互连设计,为 ARM Cortex -A15 和 Cortex-A7 这样的处理器提供了 缓存一致性 支持。以下是其特点:

- 核心支持 :设计用于支持最多 四个 Cortex-A15 或 Cortex-A7 处理器集群。

- snoop控制单元(SCU) :支持高效的缓存一致性操作。

- 接口 :提供了两个或三个 AMBA AXI3 或 AXI4 接口,用于与处理器集群或其他系统资源连接。

- 内存一致性 :支持全系统范围内的缓存一致性。

- 性能 :CCI-400 提供了有限的吞吐量和频率,适用于早期的中端和高端移动设备。

- 配置灵活性 :在一定程度上可以配置以匹配不同的系统需求。

详细见 :【ARM CoreLink 系列 2 -- CCI-400 控制器简介】

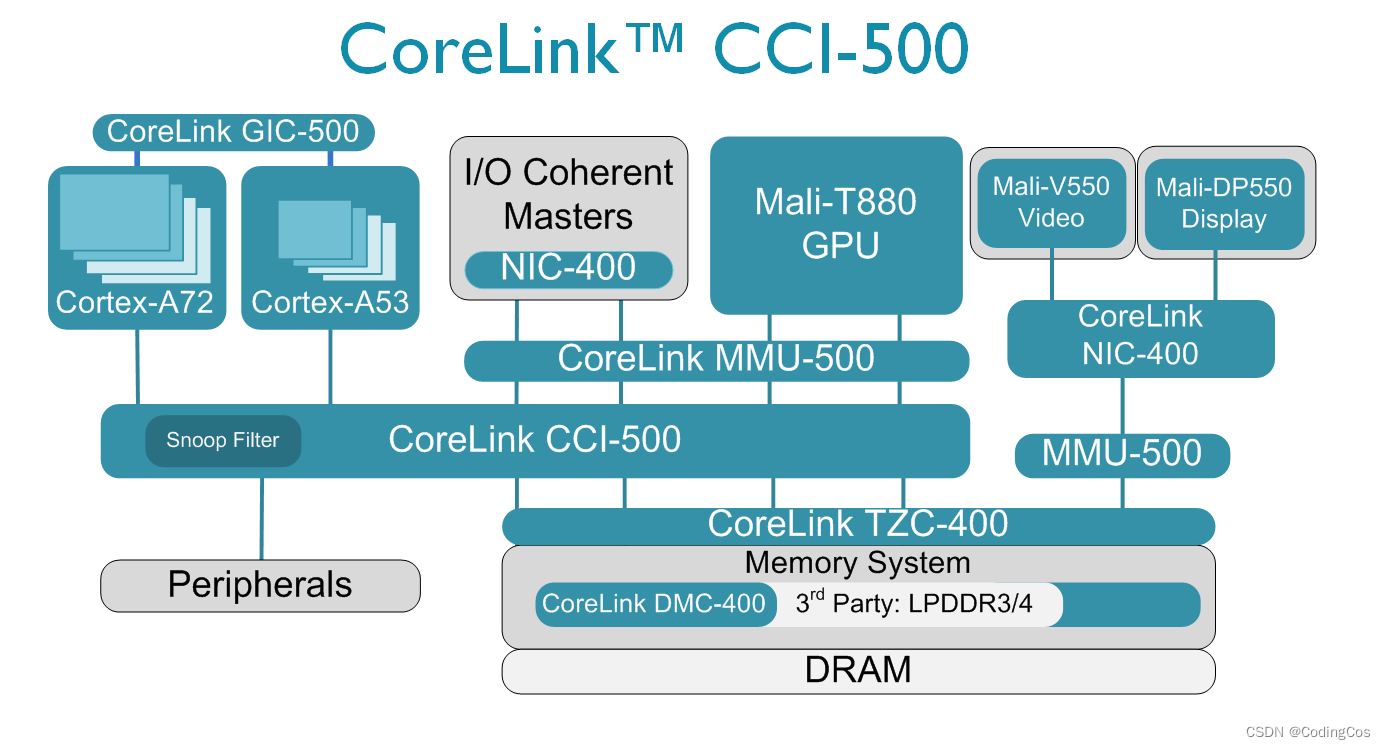

ARM CCI-500

详细内容见:【ARM CoreLink 系列 3.1 -- CCI-500 详细介绍 -上半部】

CCI-500 是一个更新和更高性能的互连设计,提供了更好的吞吐量和更低的延迟。以下是其特点:

- 发布时间 :CCI-500 早于 CCI-550,是 ARMv8 架构推出的初期产品之一。

- 核心连接 :设计用于支持多达六个不同的处理器集群,包括 ARM Cortex-A57 和 Cortex-A53 核心。

- 增强的snoop和目录结构 :提供更高效的缓存一致性机制。

- 接口 :提供多达六个 AMBA AXI4 接口,支持更高带宽和更低延迟的连接。

- 内存一致性 :支持全系统范围内的缓存一致性, 并引入了新的特性,如 Quality of Service(QoS) 和 DVM(Distributed Virtual Memory)的支持 。

- 性能 :CCI-500 提供了更高的频率和更大的带宽,适用于高性能计算和数据密集型任务。

- 扩展功能 :包括动态电压频率调整(DVFS)支持和更强的错误检测与纠正(EDAC)功能。

总结来说,CCI-500 是 CCI-400 的一个高性能版本,适用于要求更高的系统设计。 CCI-500 提供了更高的处理器集群支持 、更大的带宽、更低的延迟和额外的系统功能,这使得 CCI-500 更适合用于高端移动设备、企业级服务器和高性能计算应用。

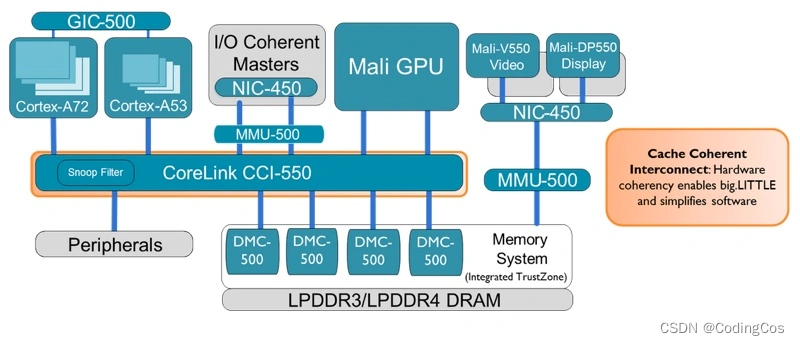

ARM CCI-550

- 发布时间 :CCI-550 是在 CCI-500 之后推出的,针对一些性能和功能进行了提升。

- 核心连接 :CCI-550 支持最多 6 个 CPU 集群连接, 包括 ARM Cortex-A57 和 Cortex-A72 核心。

- 缓存一致性 :除了提供缓存一致性外,CCI-550 引入了更复杂的缓存管理功能,比如 QoS(Quality of Service)和 DVM(Distributed Virtual Memory)的支持。

- 带宽 :CCI-550 提供了更高的系统总线带宽和更低的延迟,适用于更高性能的处理器和内存控制单元。

- 功能 :CCI-550 在功能上也有所增加,如支持动态调频(DVFS)和QoS,从而可以更好地适应不同的使用场景和性能需求。

- 内存子系统 :CCI-550 支持更大的系统缓存(System Cache),可以带来更好的数据缓存性能。

详情见: 【ARM CoreLink 系列 3 -- CCI-550 控制器介绍 】

总体来说,CCI-550 是 CCI-500 的升级版,提供了更多的核心连接、更高的带宽和更先进的缓存管理功能,更适合高性能计算和数据密集型应用。CCI-550 的设计更加注重性能和高级缓存一致性特性,而 CCI-500 则更适合对性能要求不是特别高的系统。当选择这两种互联技术时,应考虑系统的性能需求、成本以及其他系统架构的限制。

浙公网安备 33010602011771号

浙公网安备 33010602011771号