DDR4仿真之仿真环境搭建(一)

最近在进行DDR4仿真时,移植Xilinx example工程里的DDR4仿真模型遇到了一个问题,特此记录一下。

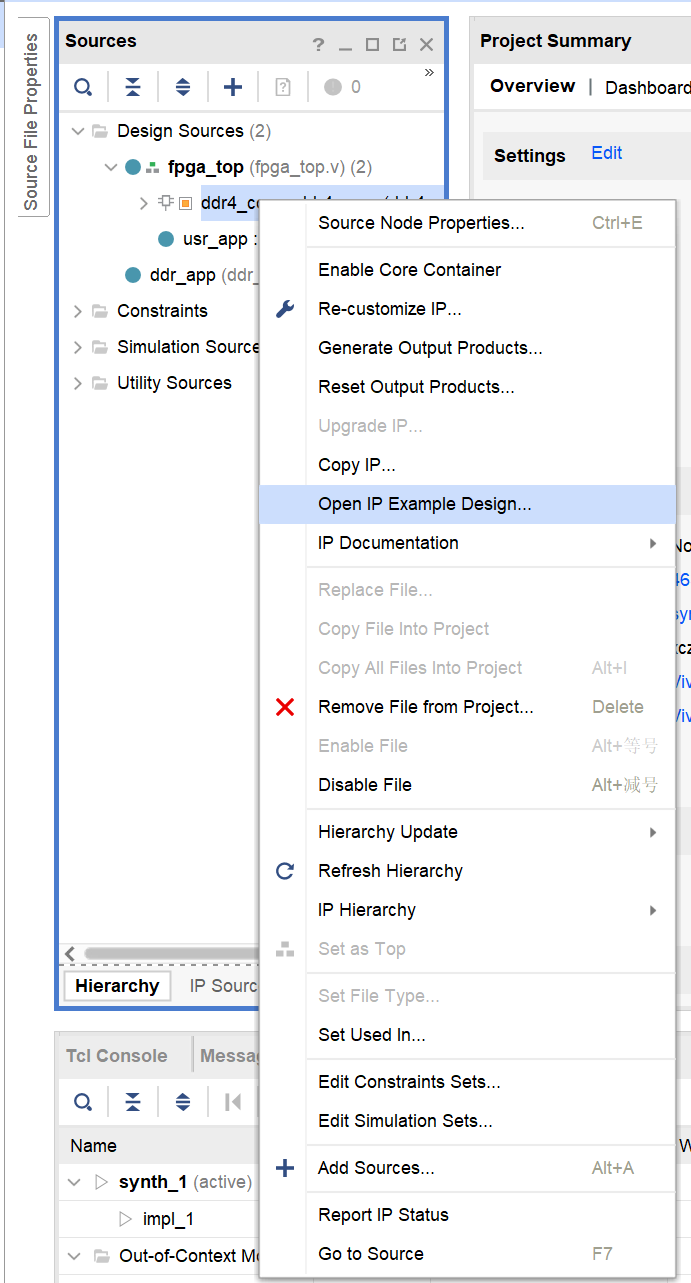

1. 配置好DDR4 IP参数生成example 工程

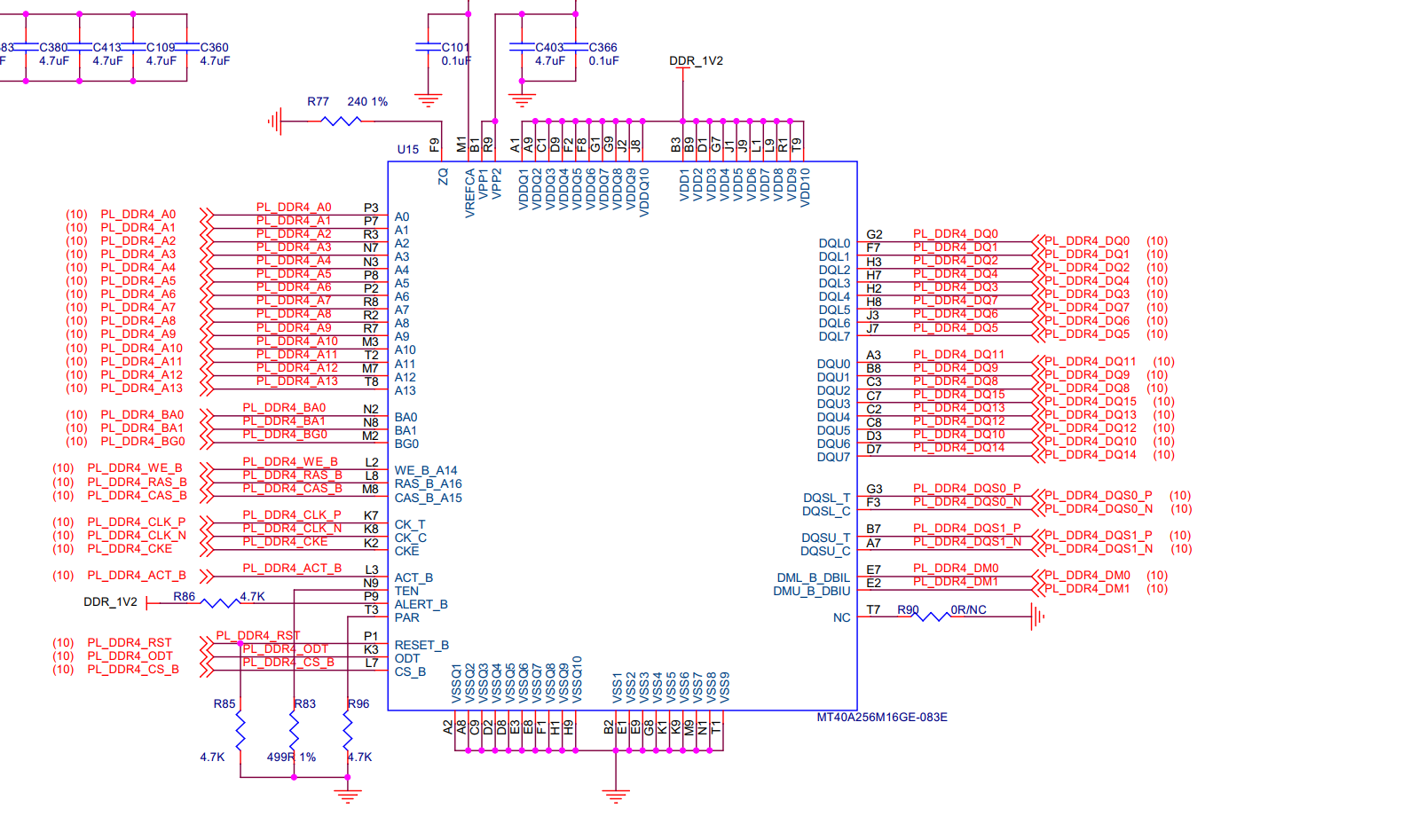

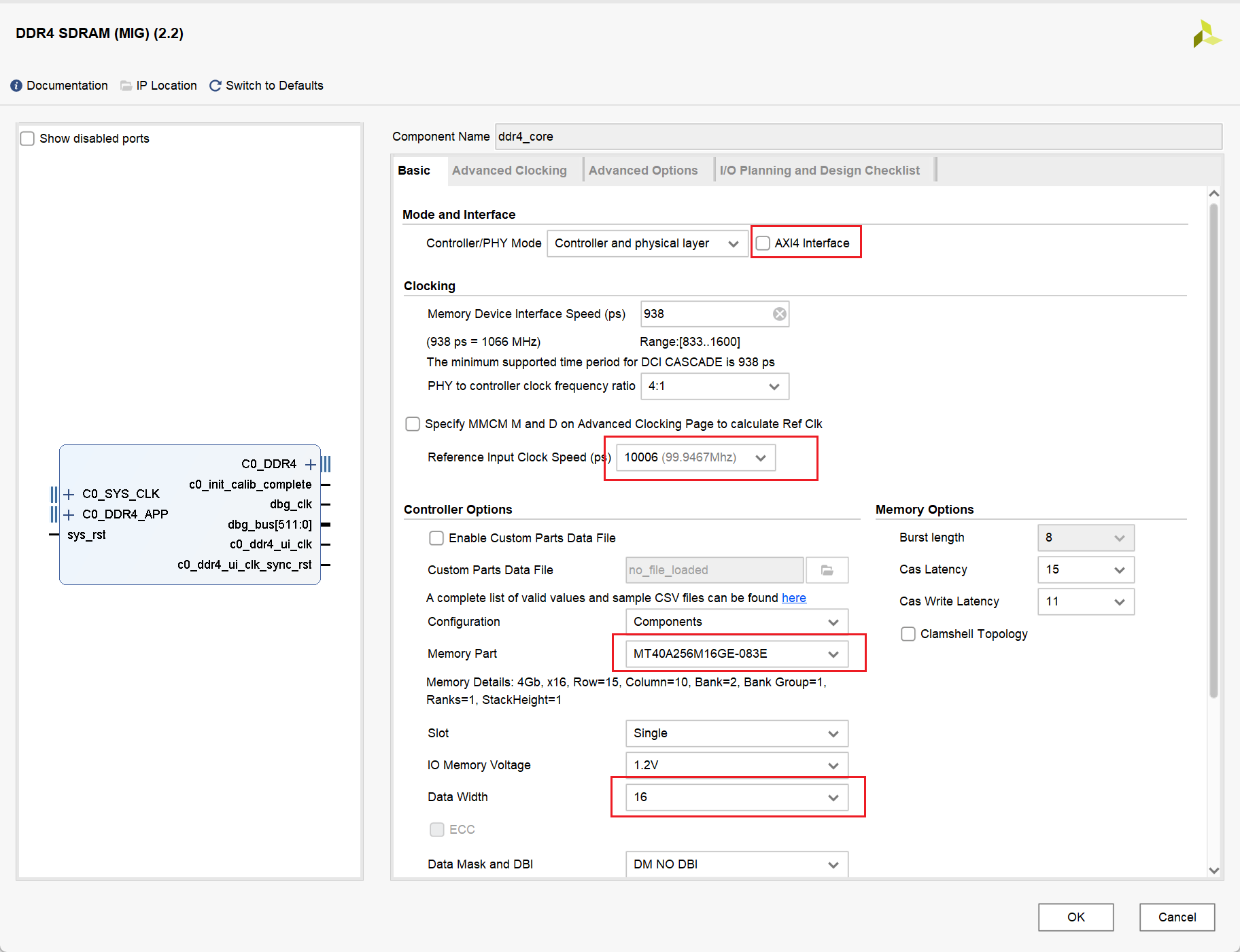

根据自己使用的DDR4型号和硬件原理图进行配置。这里我所使用的是镁光MT40A256M16GE-083E(容量256,数据位宽16),如果没有具体型号也可以选择自定义,按所用DDR4芯片手册进行相关参数配置。

4:1指的是DDR clock与refclk的比值,这里我板载的晶振是100M时钟,所以选了一个最接近的频率

2. 移植DDR4仿真模型

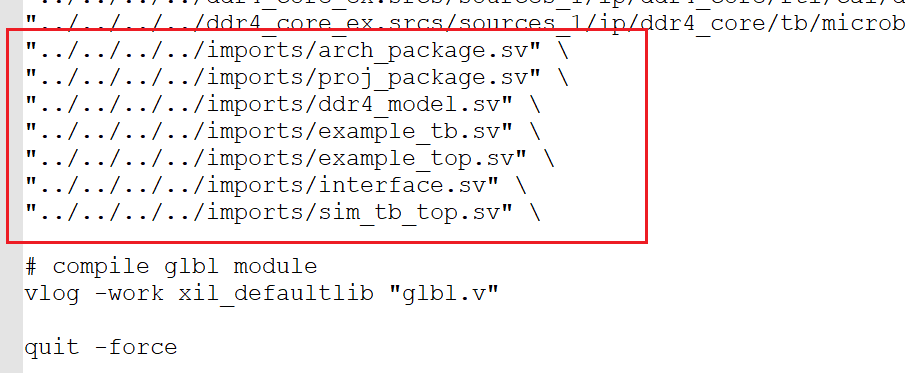

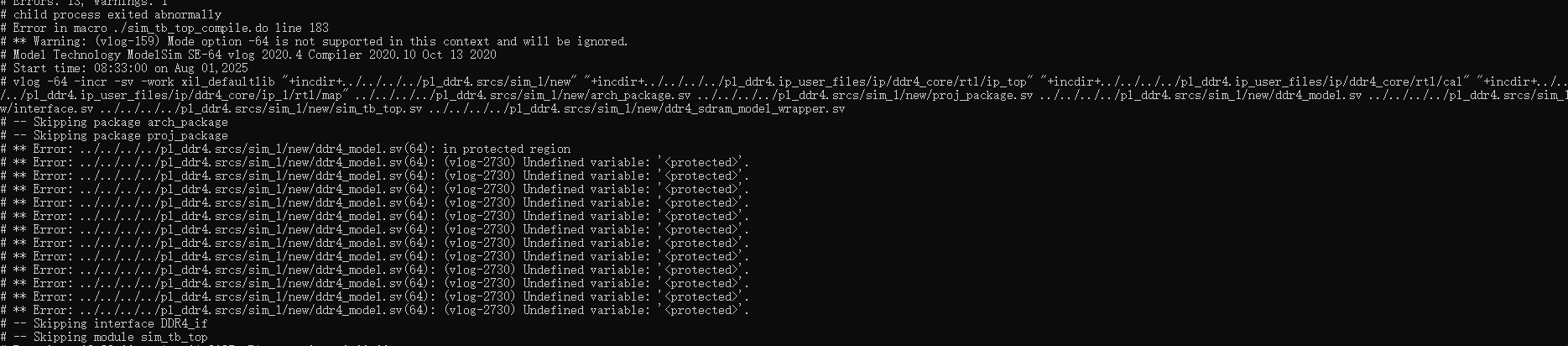

起初我以为按照仿真脚本下compile.do文件里所涉及的文件进行添加即可,结果发现仿真编译根本通不过,编译老是卡在ddr4_model.sv这个example提供的加密文件上

就算编译通过了,仿真的结果完全不对,有bug。

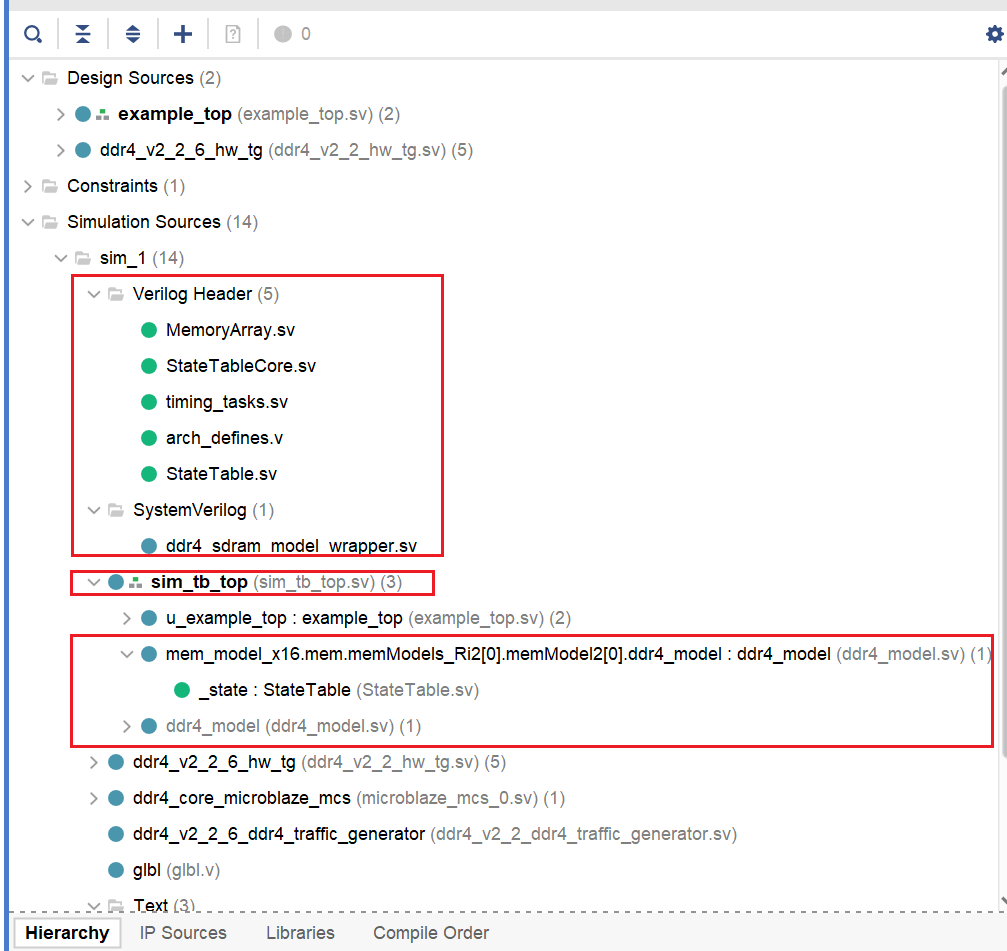

通过对example仿真目录下的文件进行挨个添加,才解决这个问题(example_top是官方设计文件,可以不用添加,但仿真目录结构下的Verilog header和system Verilog文件都要添加)

text我不知道不添加会不会有问题,没试过。

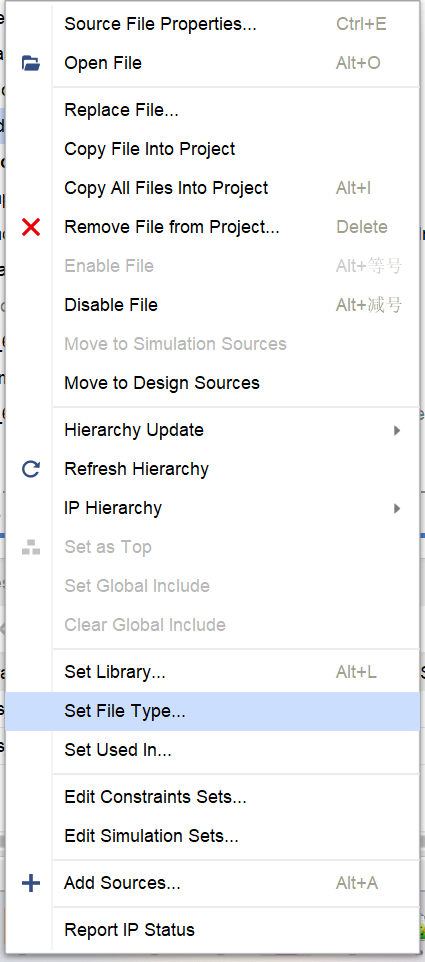

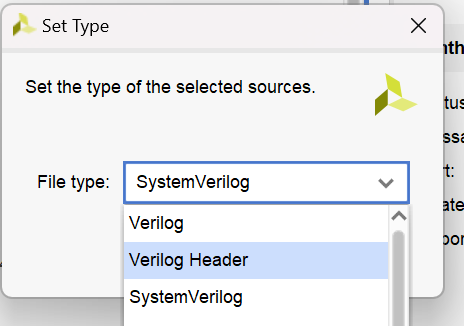

sv文件添加过来不会直接在Verilog Header下,需要手动改一下设置

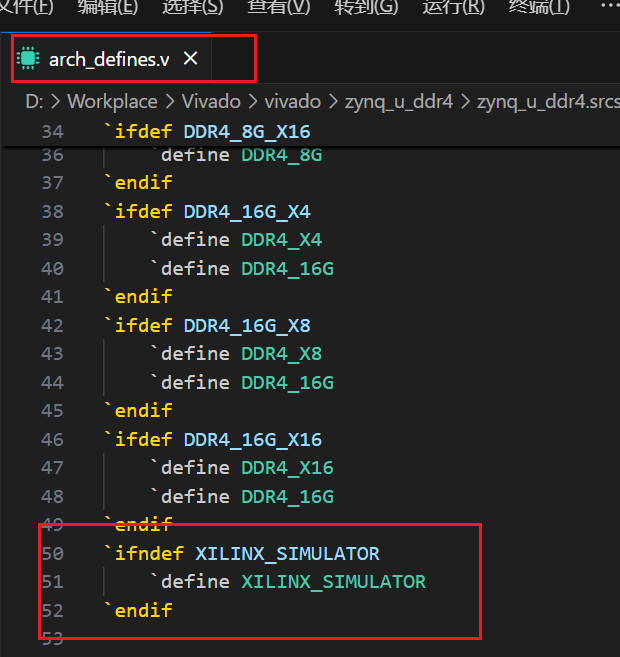

还有一个需要改的地方是这里,手动添加上XILINX_SIMULATOR,不然仿真也是有问题的

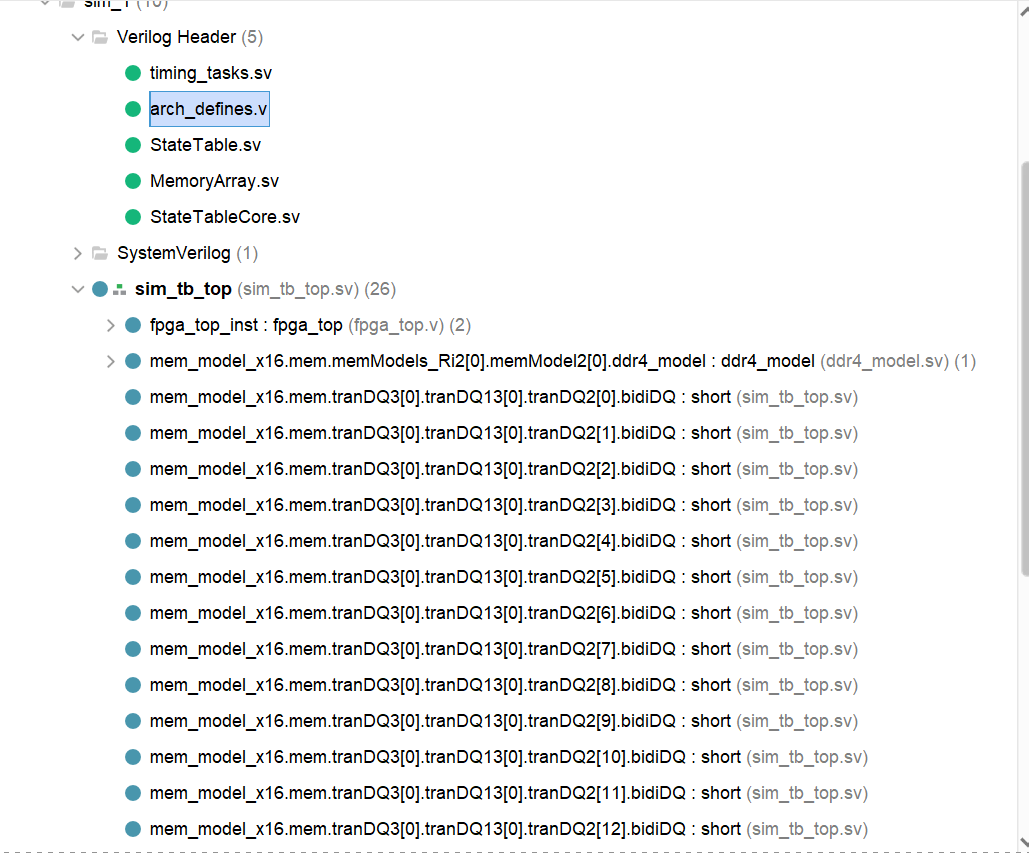

添加以后目录结构是这样(仅截图部分)

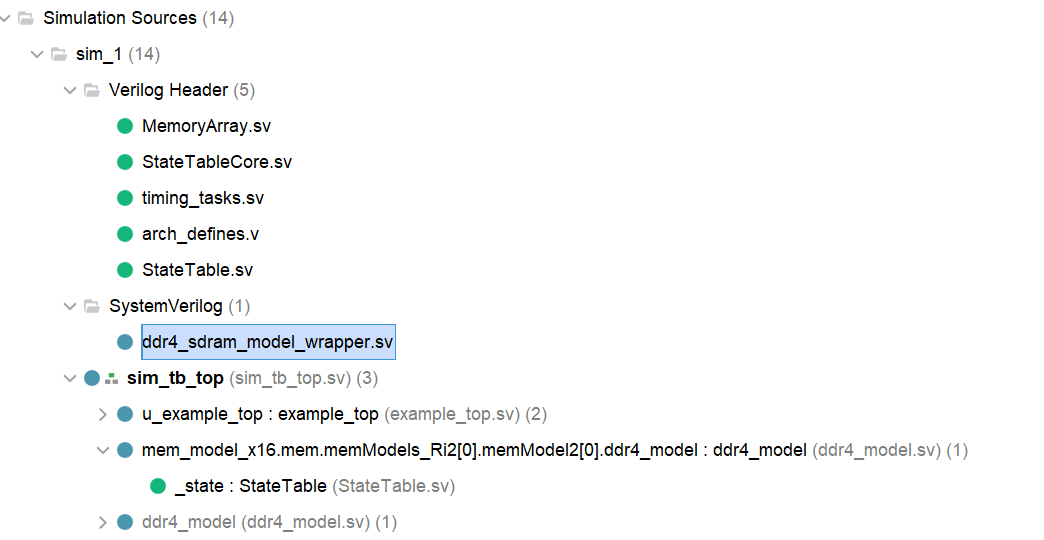

没有XILINX_SIMULATOR就会是这样

完成以上步骤就完成DDR4仿真环境的搭建,正常情况下仿真编译不会报错

如遇到报错,可能是文件编译顺序或者其他问题,请参考这篇文章[https://www.cnblogs.com/always0624/p/19005859](DDR4仿真之System Verilog编译顺序问题)

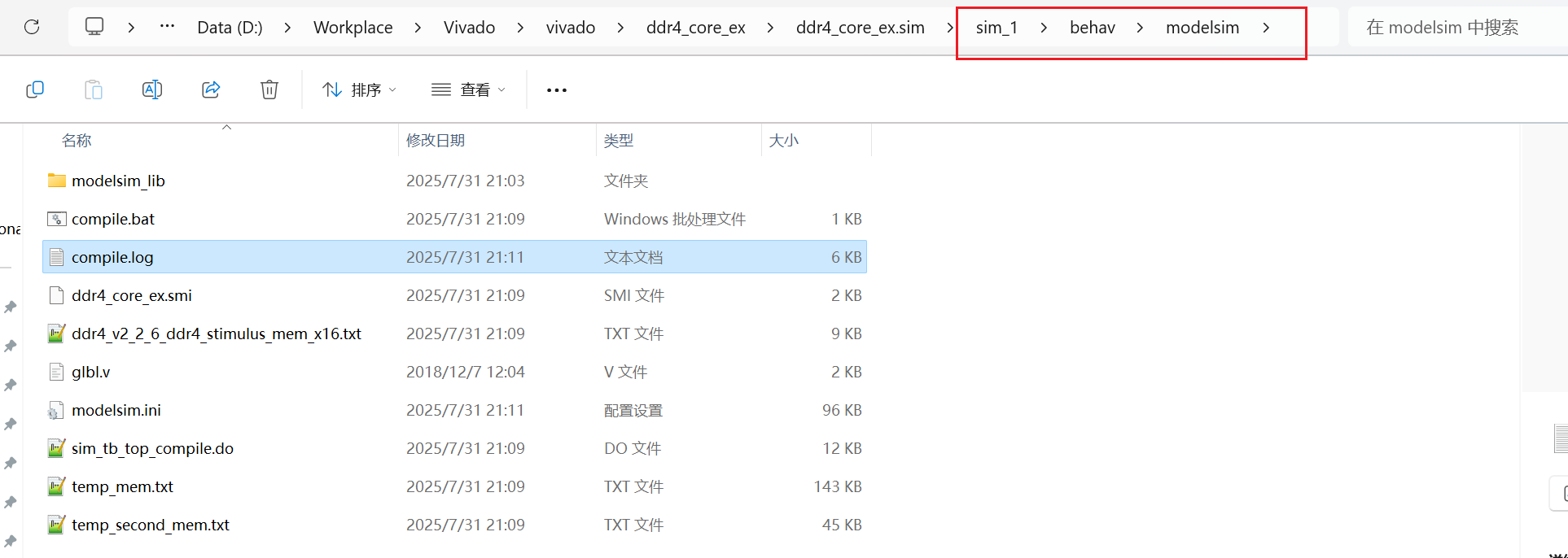

或者看compile.log(具体在工程目录下)

浙公网安备 33010602011771号

浙公网安备 33010602011771号