这个案例1-【友晶科技Terasic】基于FPGA实现LTC2308控制器的设计——总概述里面的fifo是调用的Altera现成的IP(adc_data_fifo.v),现在直接用前面掰开揉碎讲 FIFO(同步FIFO和异步FIFO)设计的 async_fifo 替换掉它Altera FIFO IP:

具体的做法是:

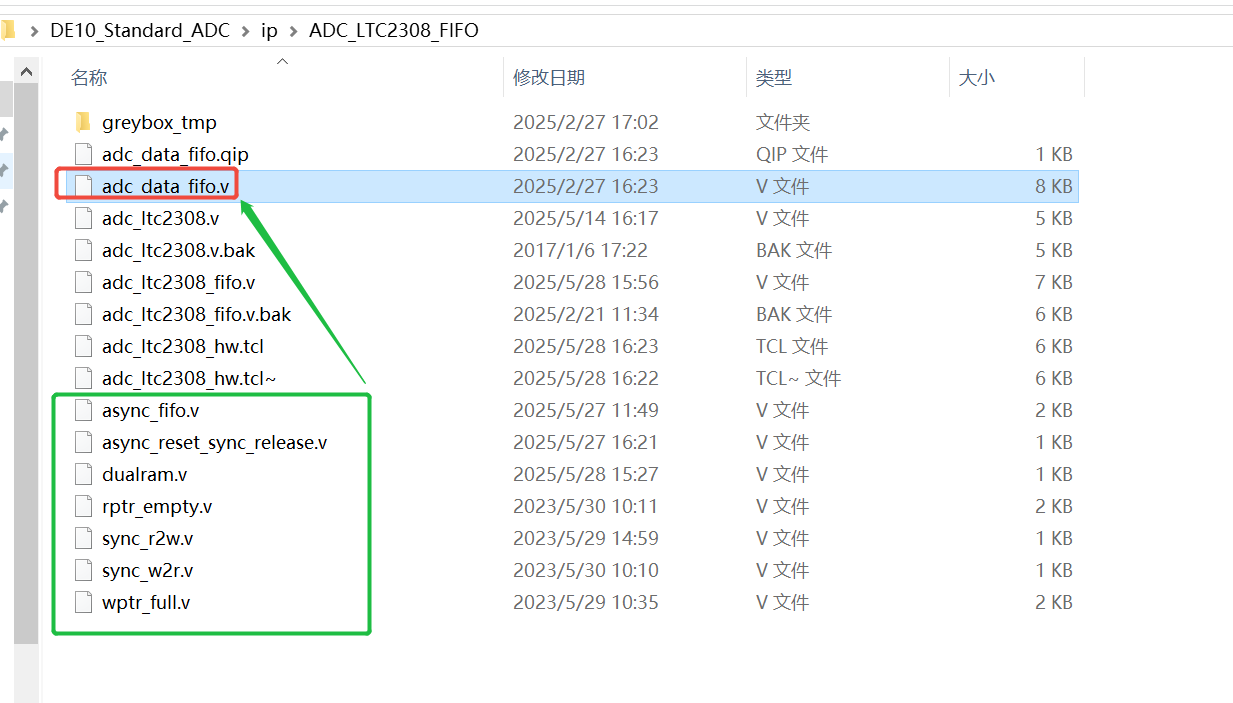

1. 删除adc_data_fifo.v文件, 增加async_fifo.v, async_reset_sync_release.v,dualram.v,rptr_empty.v,sync_r2w.v,sync_w2r.v,wptr_full.v 7个文件。

2. 在自定义 LTC2308 控制器IP 的top文件adc_ltc2308_fifo.v当中做如下修改:

3. 记得将自定义IP ADC_LTC2308_FIFO 重新生成一遍,步骤参考:

9-【友晶科技Terasic】基于FPGA实现LTC2308控制器的设计——自定义IP设计步骤(Avalon MM)(17.1)

4. 重新生成Qsys系统。步骤参考下面链接的Qsys设计部分:

8-【友晶科技Terasic】基于FPGA实现LTC2308控制器的设计——Quartus工程创建(17.1) 主要是参考该文章中 adc_ltc2308 IP 的设置部分。

5. 重新generate Qsys系统。

6. 重新编译Quartus文件,下载sof文件到DE10-Standard开发板。

7. Nios 工程代码无需更改,直接run Nios II 工程代码,按照下文章去测试:

1-【友晶科技Terasic】基于FPGA实现LTC2308控制器的设计——总概述

无

浙公网安备 33010602011771号

浙公网安备 33010602011771号