会员

周边

新闻

博问

闪存

众包

赞助商

Chat2DB

所有博客

当前博客

我的博客

我的园子

账号设置

会员中心

简洁模式

...

退出登录

注册

登录

阳光灿烂的日子

博客园

首页

新随笔

联系

订阅

管理

1

2

3

下一页

2025年12月30日

修改vscode插件语法高亮

摘要: 一般在vscode里实现某个语言的语法高亮都是借助插件实现的,但是无奈有些情况下咱觉得这个插件的高亮不太满意(闲的。。。),最近我折腾了下verilog的语法高亮部分,修改了它原本插件在某些关键字的语法高亮颜色,记录下,希望帮到有强迫症的小伙伴 首先,我用到的插件是这三个: 第一个插件的语法高亮总体

阅读全文

posted @ 2025-12-30 13:48 原声带1993

阅读(33)

评论(0)

推荐(0)

2025年12月29日

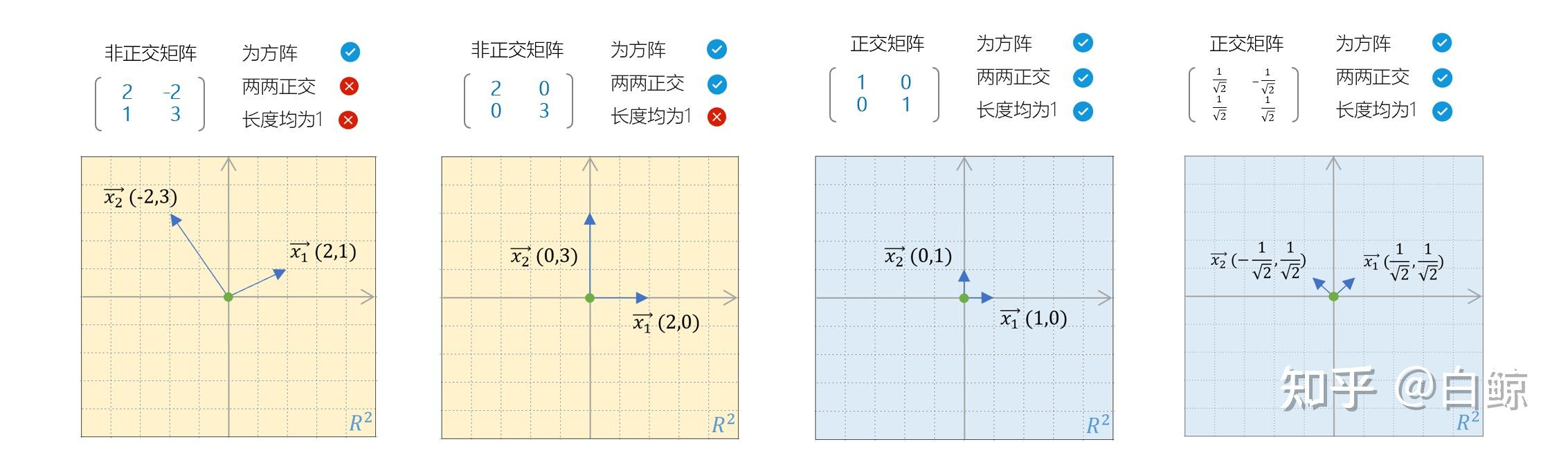

正交矩阵

摘要:

阅读全文

posted @ 2025-12-29 16:25 原声带1993

阅读(5)

评论(0)

推荐(0)

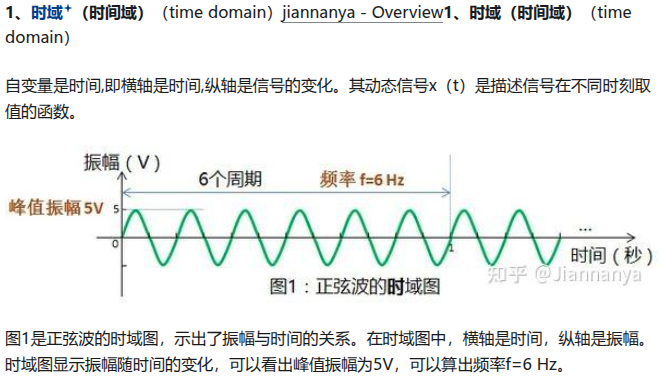

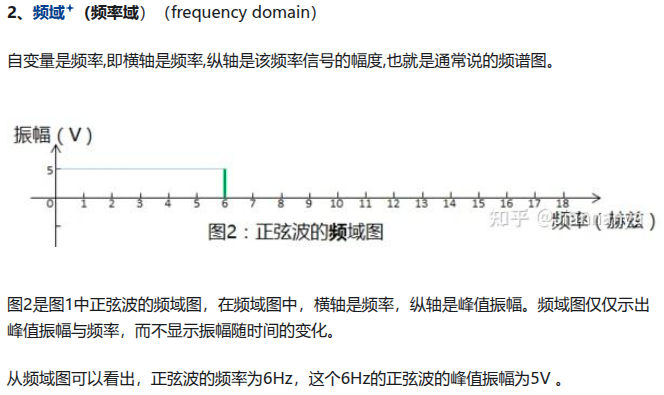

时域和频域

摘要:

阅读全文

posted @ 2025-12-29 16:25 原声带1993

阅读(5)

评论(0)

推荐(0)

pytest相关

摘要: pytest相关 pytest --ignore=tests/foobar/test_foobar_03.py --ignore=tests/hello/ 忽略tests/foobar/test_foobar_03.py 以及 tests/hello/所有测试用例 addopts是联合参数的意思 -

阅读全文

posted @ 2025-12-29 16:15 原声带1993

阅读(3)

评论(0)

推荐(0)

docker相关

摘要: 官网安装docker for pkg in docker.io docker-doc docker-compose docker-compose-v2 podman-docker containerd runc; do sudo apt-get remove $pkg; done sudo apt-

阅读全文

posted @ 2025-12-29 16:11 原声带1993

阅读(2)

评论(0)

推荐(0)

linux常用命令

摘要: sudo find / -path /media -prune -o -type f -name "routing.rules" -print sudo find / -path /media -prune -o -name "*.desktop" sudo find / -path /media

阅读全文

posted @ 2025-12-29 16:08 原声带1993

阅读(4)

评论(0)

推荐(0)

为什么74汉明码只能检测2bit以内的错误

摘要: 74汉明码是奇偶校验的加强版,属于块校验。即假设信息位有n位,校验位k位,假设只有1bit错误的前提下,n+k位就有n+k种1bit错误情况,加上没有出错的情况,总共n+k+1种情况,k位校验要覆盖以上所有的n+k+1,则有 2^k >= n+k+1 假设n = 4 ,则根据上式,得出k=3 其实就

阅读全文

posted @ 2025-12-29 15:31 原声带1993

阅读(18)

评论(0)

推荐(0)

petalinux常用命令

摘要: petalinux常用命令 petalinux-package --boot --format BIN --fsbl ./images/linux/zynqmp_fsbl.elf --u-boot ./images/linux/u-boot.elf --pmufw ./images/linux/pm

阅读全文

posted @ 2025-12-29 15:13 原声带1993

阅读(18)

评论(0)

推荐(0)

vsftpd设置外网访问

摘要: vsftpd如果要外网访问,要配置成被动模式,vsftpd默认是主动模式,被动模式就是将21端口映射出去,监听,连接后,服务端将本地数据放在额外的映射好的对外端口,使客户端 主动来拉取,这个对客户端没有公网要求,所以要映射21端口,然后再映射一个范围的数据端口出去 pasv_promiscuous=

阅读全文

posted @ 2025-12-29 15:04 原声带1993

阅读(8)

评论(0)

推荐(0)

浅谈DDR以及MIG核的配置

摘要: DDR基础 先说下DDR的基础内容,典型的计算机存储架构是:Channel -> DIMM -> Rank -> Chip -> Bank -> row/col Channel,通道,其实可以理解为内存控制器,这个通常是由主控芯片决定的,比如常见的家用cpu处理器就是双通道的,就是有两个控制器,数据

阅读全文

posted @ 2025-12-29 14:48 原声带1993

阅读(30)

评论(0)

推荐(0)

1

2

3

下一页

公告