libero ProASIC3 A3P250 RAM Dual Port 真双端口

DS0097: ProASIC3 Flash Family FPGAs Datasheet

AC374: Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-Based cSoCs and FPGAs App Note

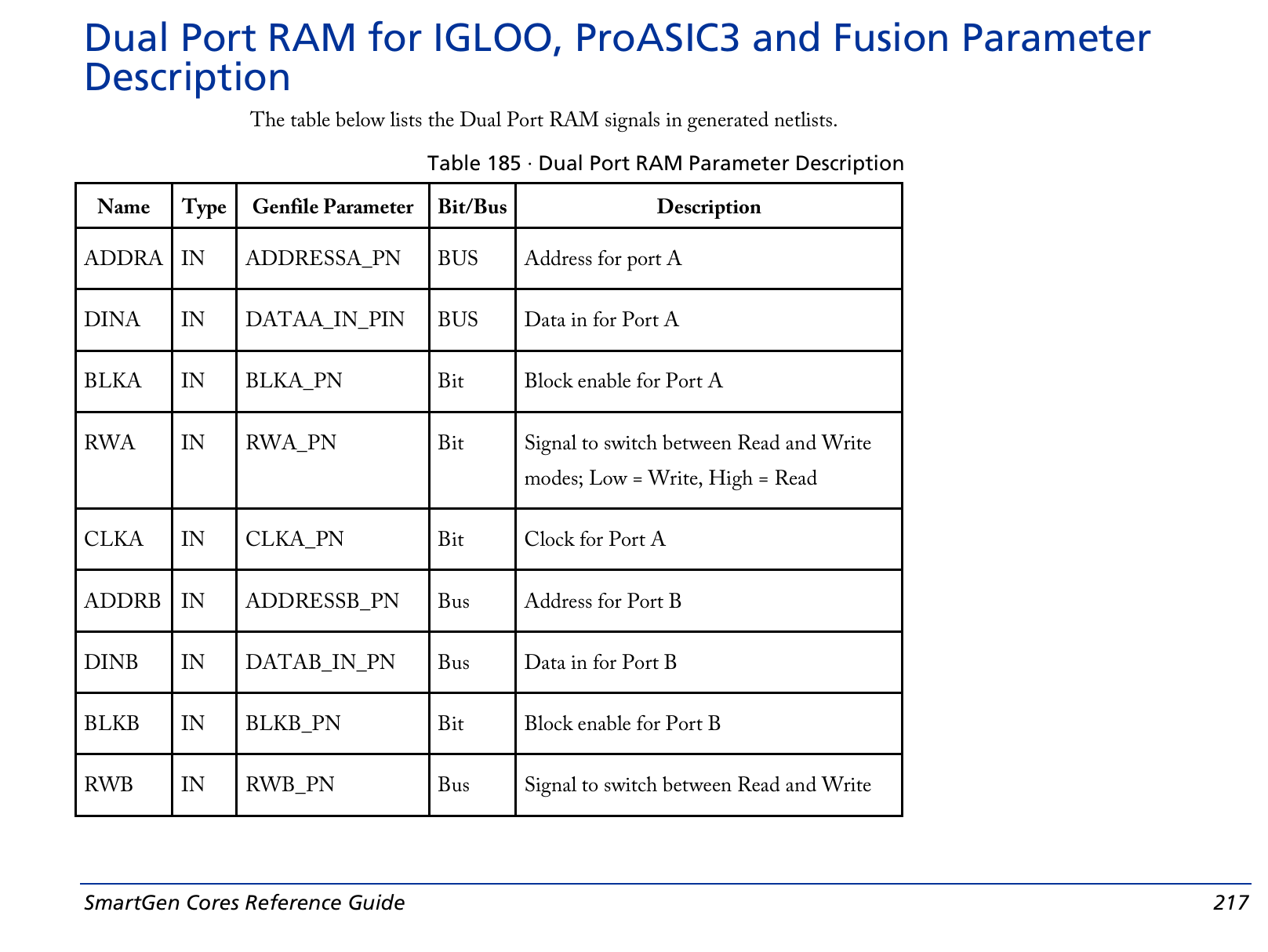

该文档 213 页 , 详细 描述 了 Dual Port RAM 相关参数

SmartGen Cores Reference Guide

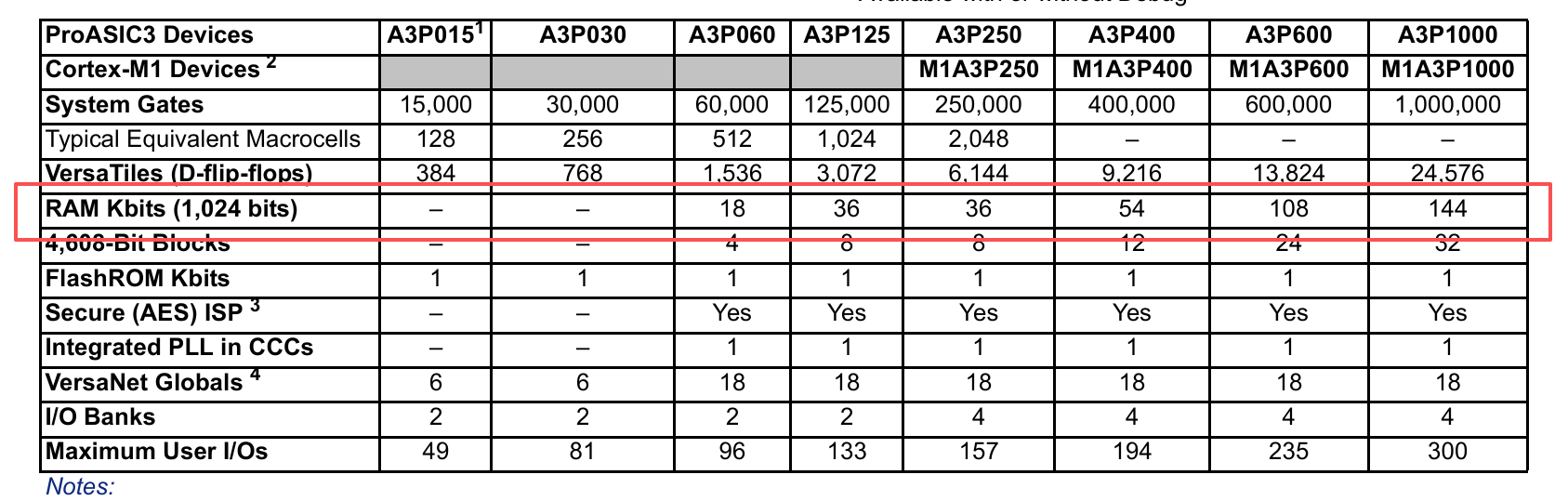

ProASIC3 包含的 RAM 资源数量:

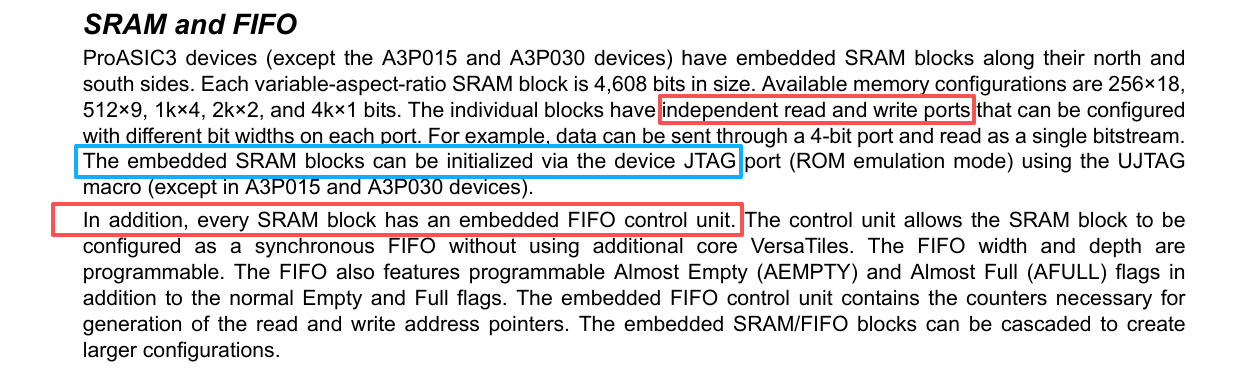

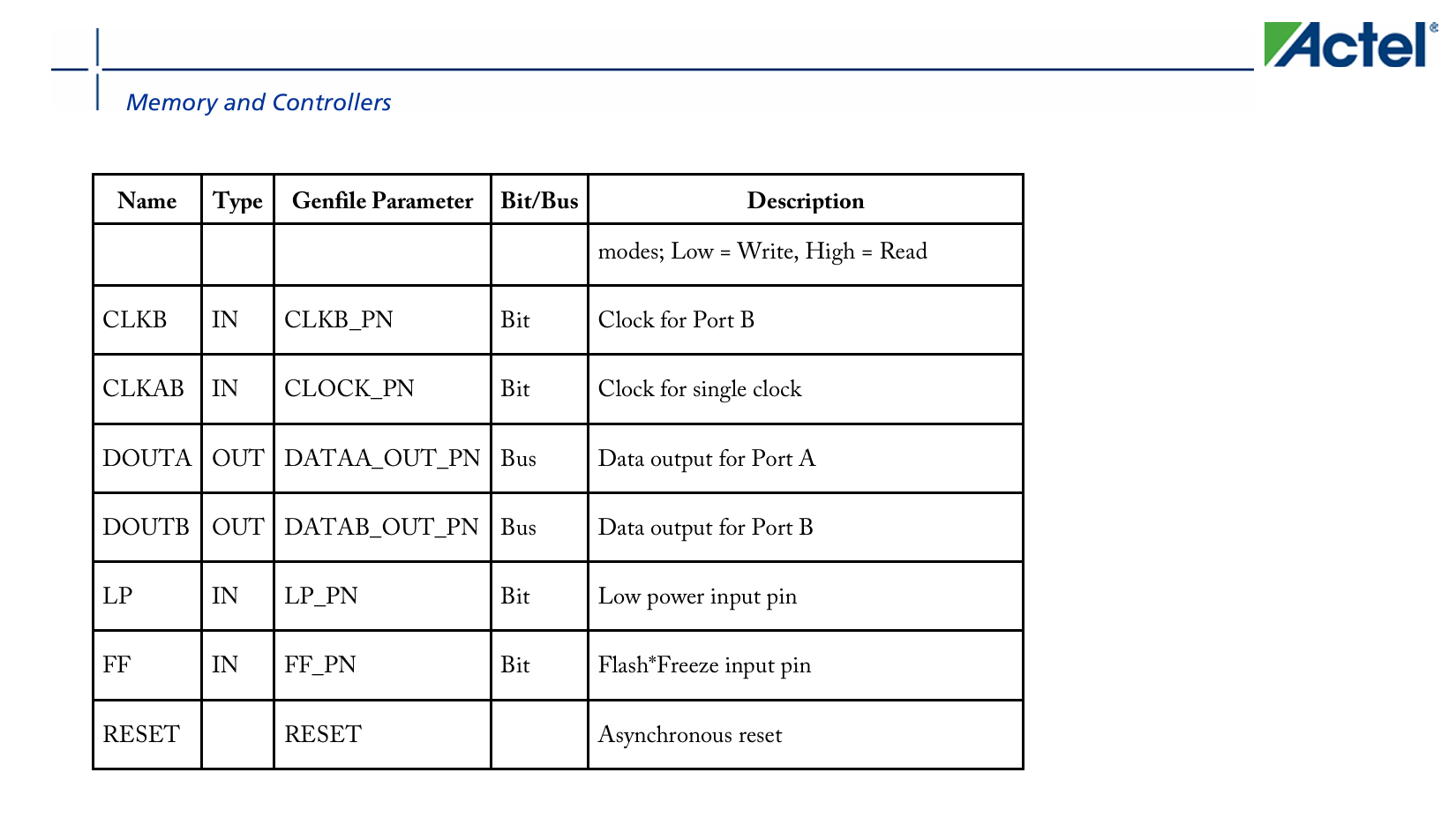

描述:

IP调用方式:Libero 11.8 → catalog → Memory & Controllers → RAM-Dual Port

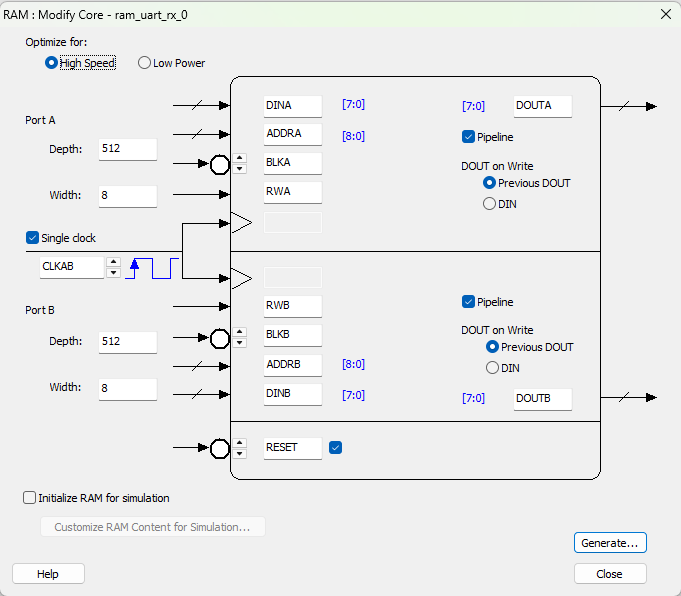

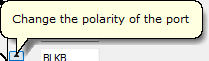

豆包:这是FPGA 开发工具中双端口 RAM 的 IP 配置界面,用于定制双端口 RAM 的参数、接口与工作模式,下面分模块解释各部分功能:

1. 优化目标(Optimize for)

- 可选 High Speed(当前选中) 或 Low Power:

这里选择 “高速模式”,意味着 RAM 的硬件实现会优先保证读写速度,而非功耗优化。

2. 端口配置(Port A & Port B)

- Depth(深度):均设为

512,表示 RAM 的存储单元数量为 512 个; - Width(位宽):均设为

8,表示每个存储单元的位数为 8 位;→ 整个 RAM 的总容量为512×8 = 4096bit = 512字节。 - Single clock(单时钟):已勾选,且时钟选择为

CLKAB,说明 Port A 和 Port B 共用同一个时钟信号(双端口同步工作);若取消勾选,则两个端口可使用独立时钟(异步双端口)。

3. 内部信号与工作模式(右侧模块区)

- 信号位宽匹配:

DINA/DINB(写数据):位宽[7:0],对应 Port 的 Width=8;ADDRA/ADDRB(地址):位宽[8:0],因为2^9=512,刚好覆盖 Depth=512 的地址范围;DOUTA/DOUTB(读数据):位宽[7:0],与写数据位宽一致。

- Pipeline(流水线):已勾选,说明 RAM 的读操作采用流水线模式(读输出会有 1 个时钟周期的延迟,用于提升工作频率)。

- DOUT on Write(写操作时的读输出):

重点:选中

Previous DOUT,表示 “写操作时,读输出保持之前的值”;若选DIN,则写操作时读输出会直接显示当前写入的数据(即 “写直通” 模式)。

4. 全局与仿真配置

- RESET:已勾选,说明该 RAM 支持复位功能,可通过复位信号初始化 RAM 状态。

- 仿真初始化:

Initialize RAM for simulation未勾选,若勾选可通过Customize RAM Content for Simulation...按钮设置仿真时的 RAM 初始数据。

问题一:→O 代表什么意思? 取反器? 鼠标 放在 圆圈后面的 上下箭头上会显示“ Change the polarity of the port”

猜测是 带 O 表示 低电平有效, 需要验证 !在 AC374 文档中有一句 Active low block enables for each port, 验证了 带O 表示 低电平有效!!!

问题二: DOUT on Wirte 字面意思 写操作时输出,可选择有两种方式?答案 在上面, 橙色开头!

问题三: BLKA 是什么意思? 应该是选择 A端口 是否使能!

问题四: RWA, 低电平 写使能, 高电平 读取。

在 AC374 文档中Active low block enables for each port , 低电平 使能对应端口!

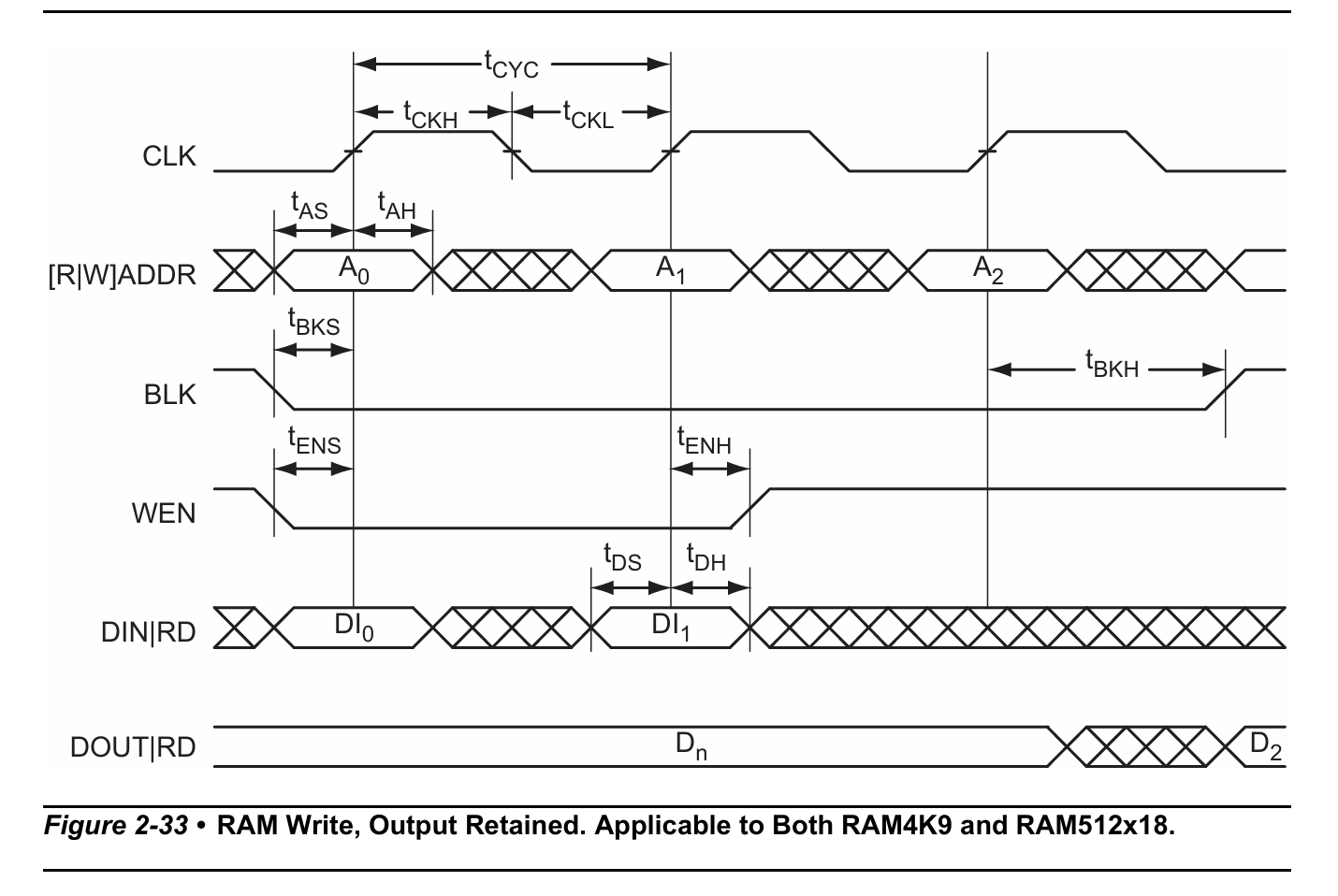

写操作时序:DS0097

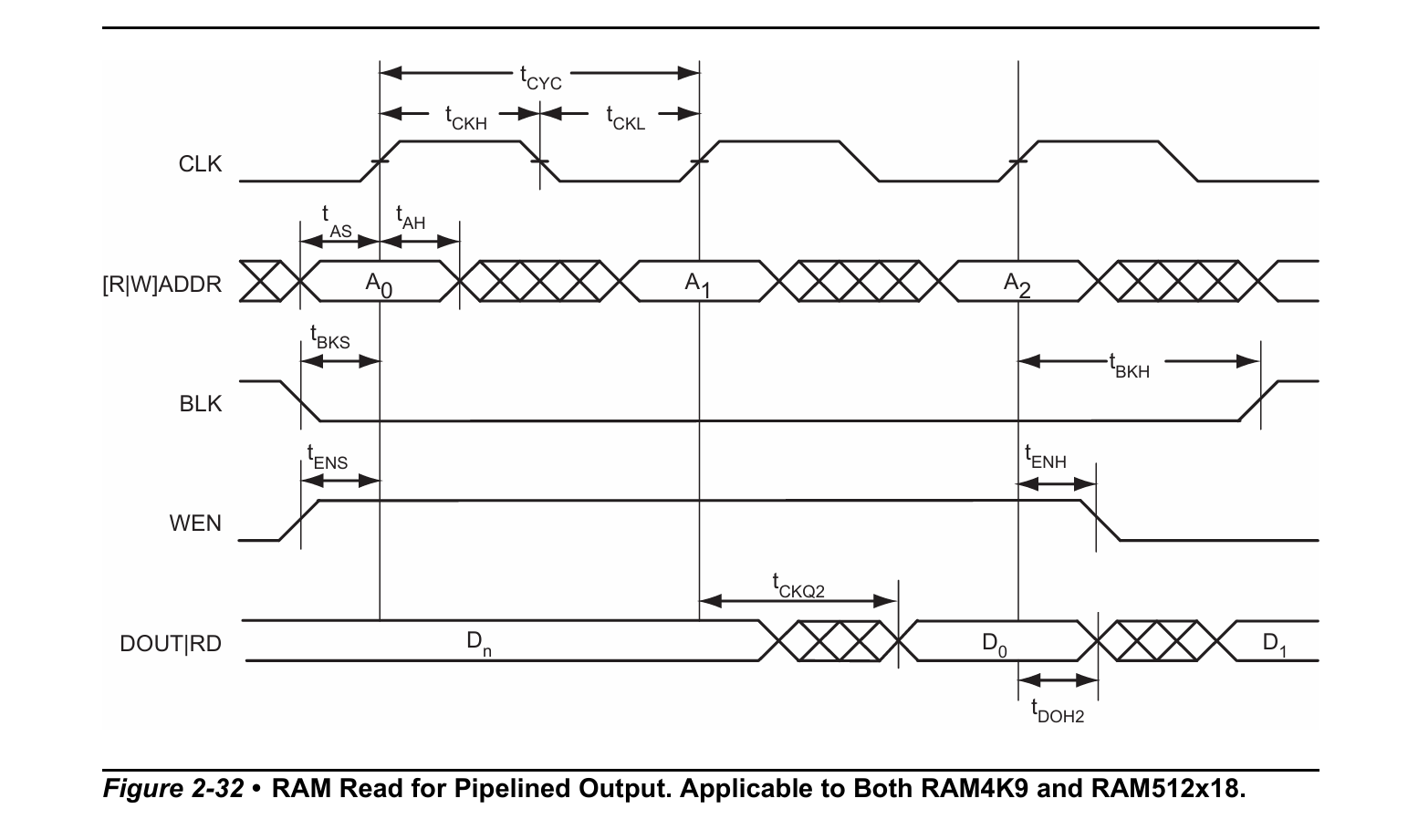

读操作时序( Previous DOUT ):DS0097

重点: 读取 时 数据输出要 ‘延迟2个’ clk 周期! 看图是延迟一个时钟周期,实际测试 要延迟2个时钟周期!

按照时序 用 RAM 做缓存, 实现串口数据 回环 , 结果 最后 一个数据 ,跑到 第一个 去了, 不知道 是 写 的有问题 ,还是读取的 有问题?

[11:37:26.692]发→◇EC 91 00 02 00 01 □

[11:37:26.694]收←◆01 EC 91 00 02 00

问题解决 : 读使能,地址给出后,要延迟 两个 时钟周期, 数据才正确!

[11:50:13.075]发→◇EC 91 00 02 00 01 □

[11:50:13.079]收←◆EC 91 00 02 00 01

结论 : 读写 RAM 过程 都需要 三个主时钟周期; 2026年1月12日 17点18分

2026年1月22日 11点17分 后面发现 ,这里 不稳定 是由于 40Mhz 时钟驱动来自 引脚, 驱动能力不足, 需要 使用 PLL 输出的 时钟 问题解决

浙公网安备 33010602011771号

浙公网安备 33010602011771号