libero ProASIC3 A3P250 CCC PLL 时钟配置

芯片手册

DS0097: ProASIC3 Flash Family FPGAs Datasheet

资源如下:

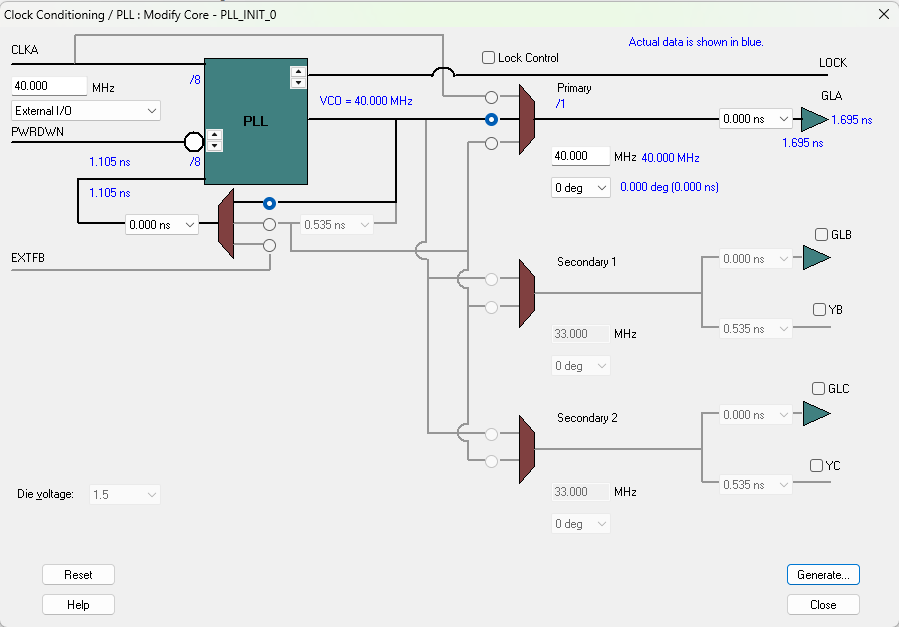

Clock Conditioning Circuit (CCC) and PLL

• Six CCC Blocks, One with an Integrated PLL

• Configurable Phase-Shift, Multiply/Divide, Delay Capabilities and External Feedback

• Wide Input Frequency Range (1.5 MHz to 350 MHz)

SmartGen Cores Reference Guide 文档 124 页

使用内置上电复位电路:Application Note AC380

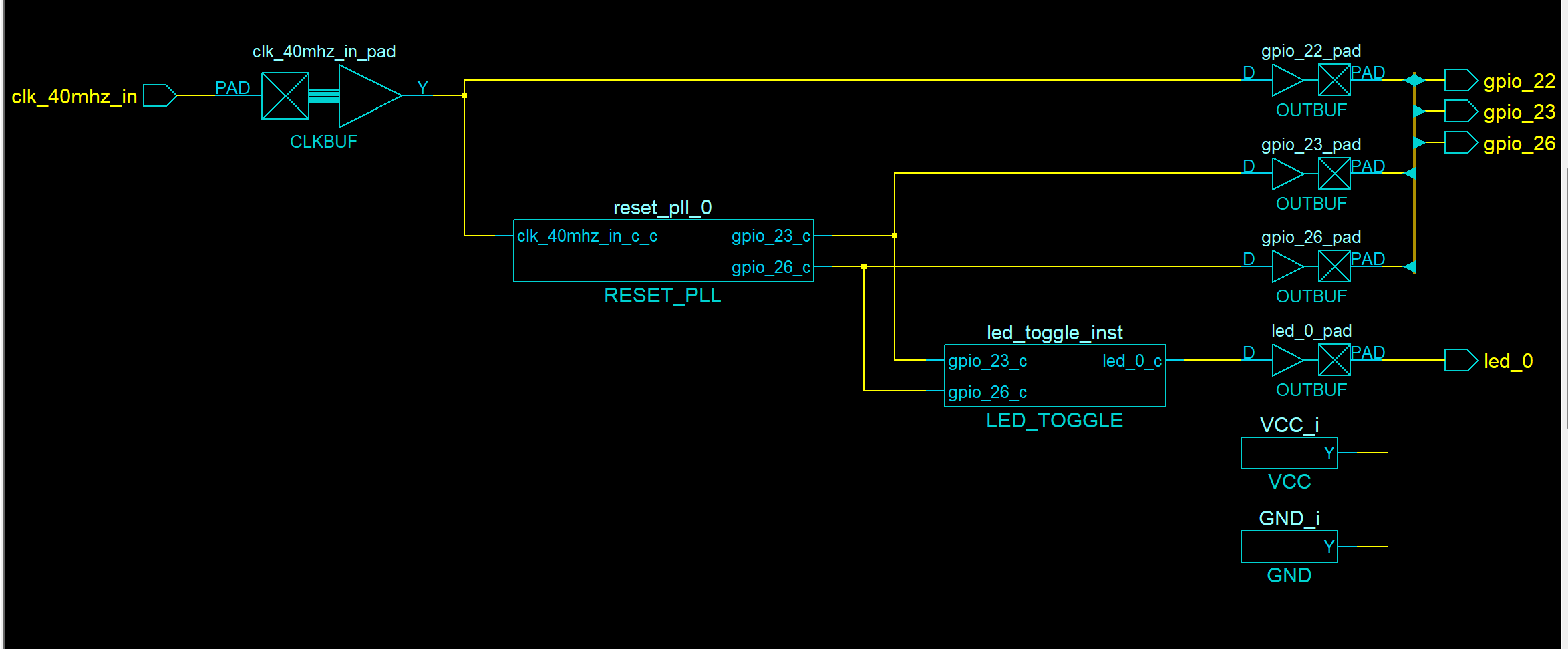

PLL 框图

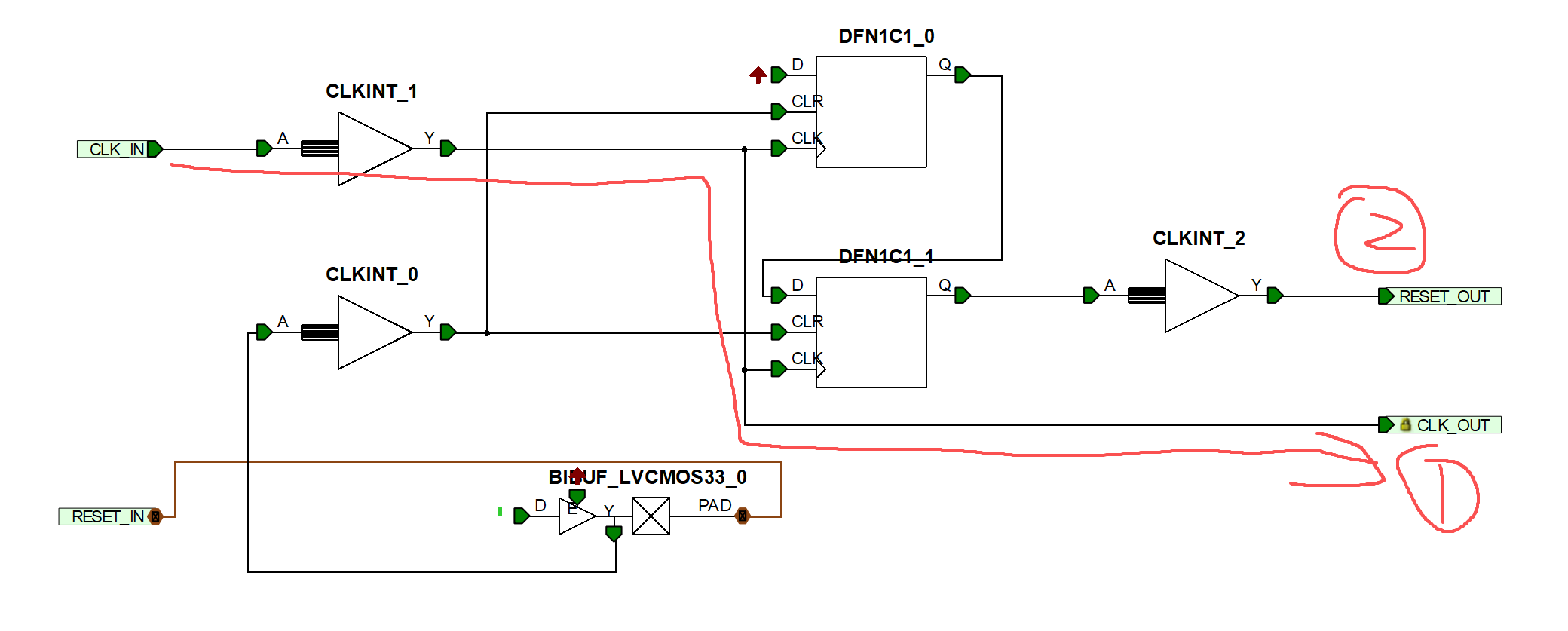

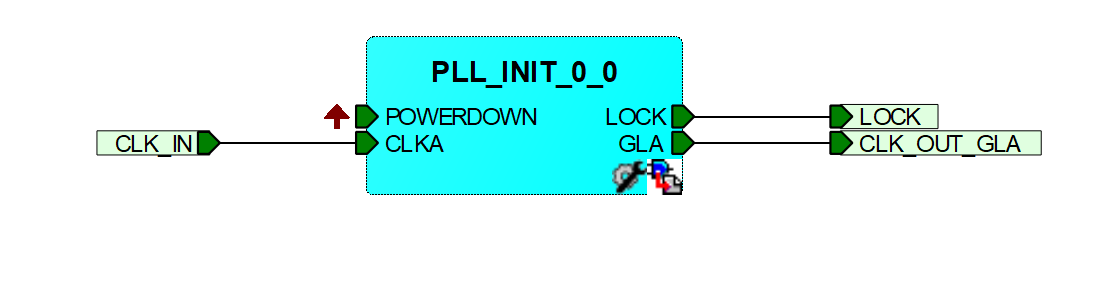

// top.v module top ( input clk_40mhz_in, // 40 MHz input GPIO->62 GCA1/IO50PDB1 inout rst_n_in, // reset input GPIO->64 // 观察引脚 output gpio_22, output gpio_23, output gpio_26, output gpio_27, // led_0 引脚 output led_0 // LED0 output GPIO->13, 低电平点亮 ); // 观察信号 assign gpio_22 = clk_40mhz; assign gpio_23 = rst_n; // 经过 CLKINT 强化驱动能输出的时钟信号 wire clk_40mhz; // 上电 reset 信号 例化 RESET reset_i( // Inputs .CLK_IN(clk_40mhz_in), // Outputs .RESET_OUT(rst_n), .CLK_40MHZ(clk_40mhz), // Inouts .RESET_IN(rst_n_in) ); // PLL_INIT PLL_INIT pll_init_i( // Inputs .CLK_IN(clk_40mhz_in), // Outputs .CLK_OUT_GLA(gpio_26), .LOCK(gpio_27) );

分析 :

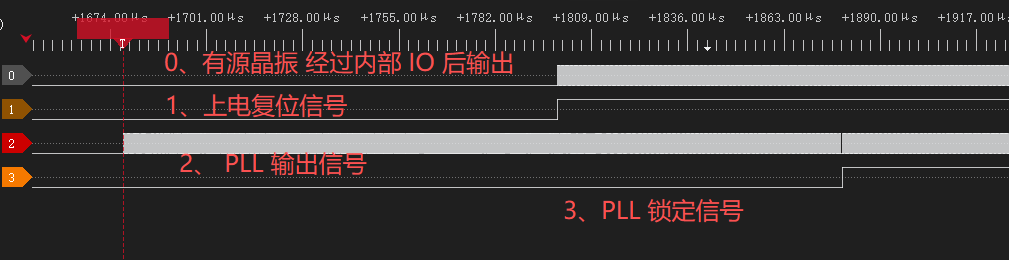

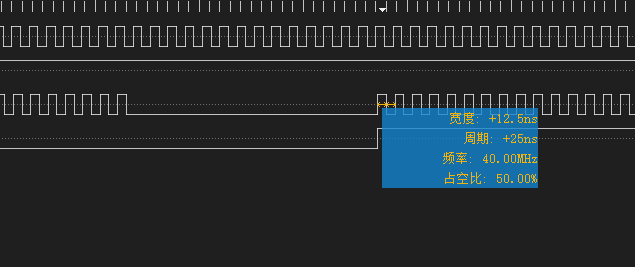

1、 PLL 模块 上电就有 时钟 输出 , 早于 有源晶振 ;

2、有源晶振 输出后, 80us 后 PLL lock 信号 拉高 , 即 锁定 ;

因此 可以 利用 PLL 的 lock 信号 作为 上电复位信号 , 但是 lock 不知 是否稳定, 因此 lock 信号 拉高后, 计时 1ms 后 rst_n 拉低 !

浙公网安备 33010602011771号

浙公网安备 33010602011771号