基于EPCLYPSE的DDS控制器(一)

简介

本篇介绍一下笔者最近用ECLYPSE Z7搭建的一个dds控制器,用于产生不同的信号,可以实现幅度可调,频率可调,相位可调,还有波形选择,有正弦波,三角波,锯齿波还有方波可以任君选择,然后通过串口,与电脑端进行交互,用电脑端控制ECLYPSE Z7产生不同的信号,方便调试。

软硬件平台

操作系统:windows11

软件平台:vivado2021.1 开发套件

硬件平台:Digilent Eclypse-Z7 Zmod开发套件

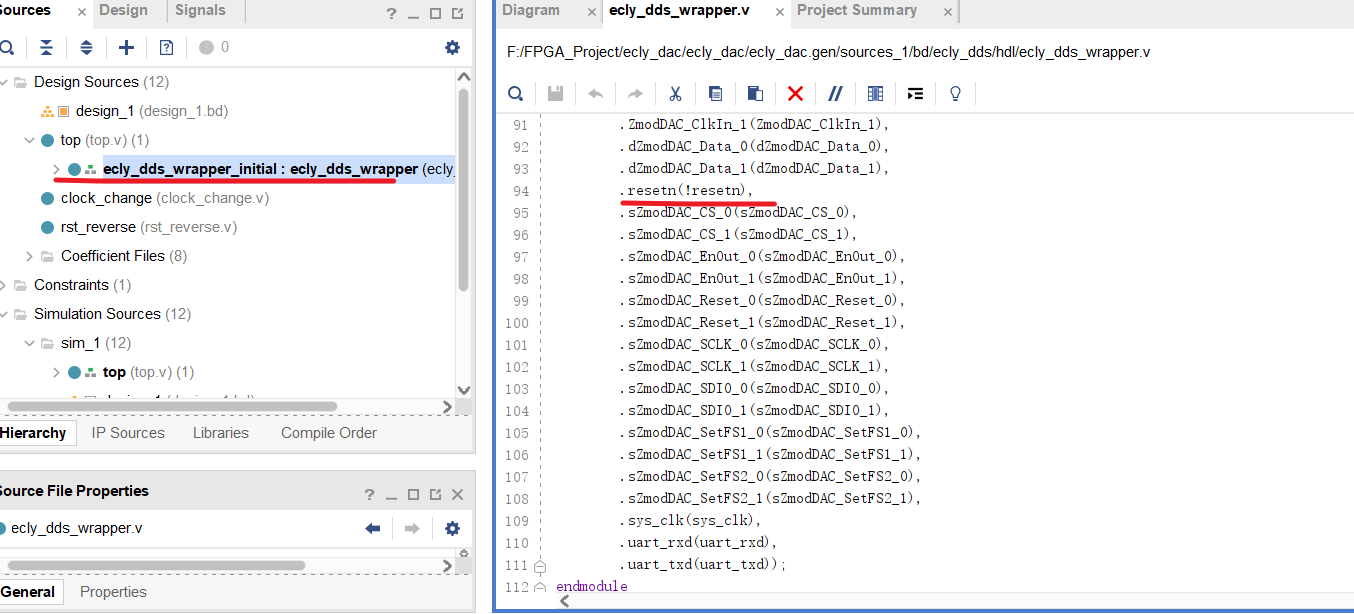

vivado 工程搭建

①直接拉取笔者的三个ip

②新建工程

唯一注意的就是板子芯片不要选错就好了

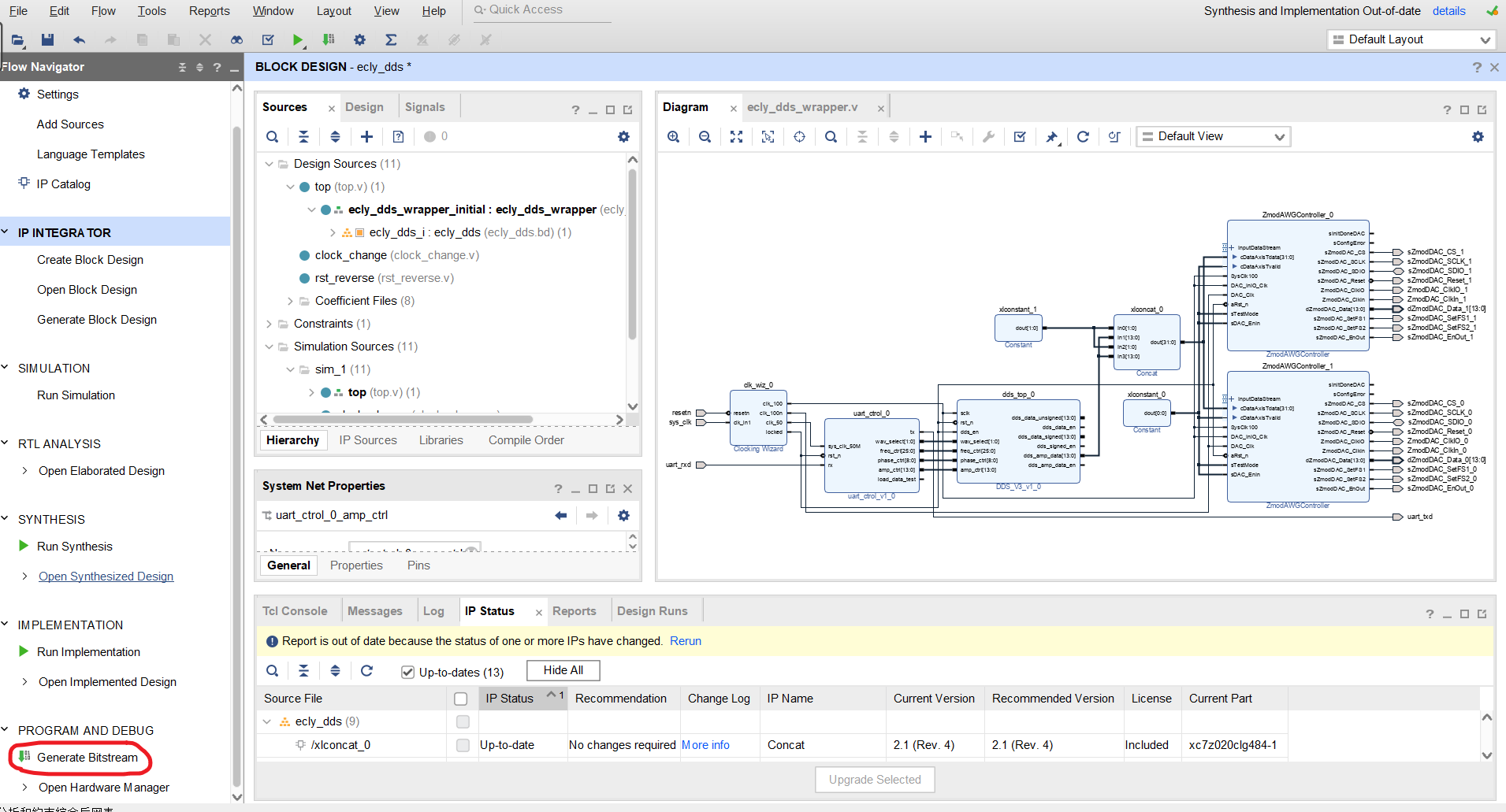

③工程构建

主语路径不能有中文,这三个ip就是笔者链接的ip

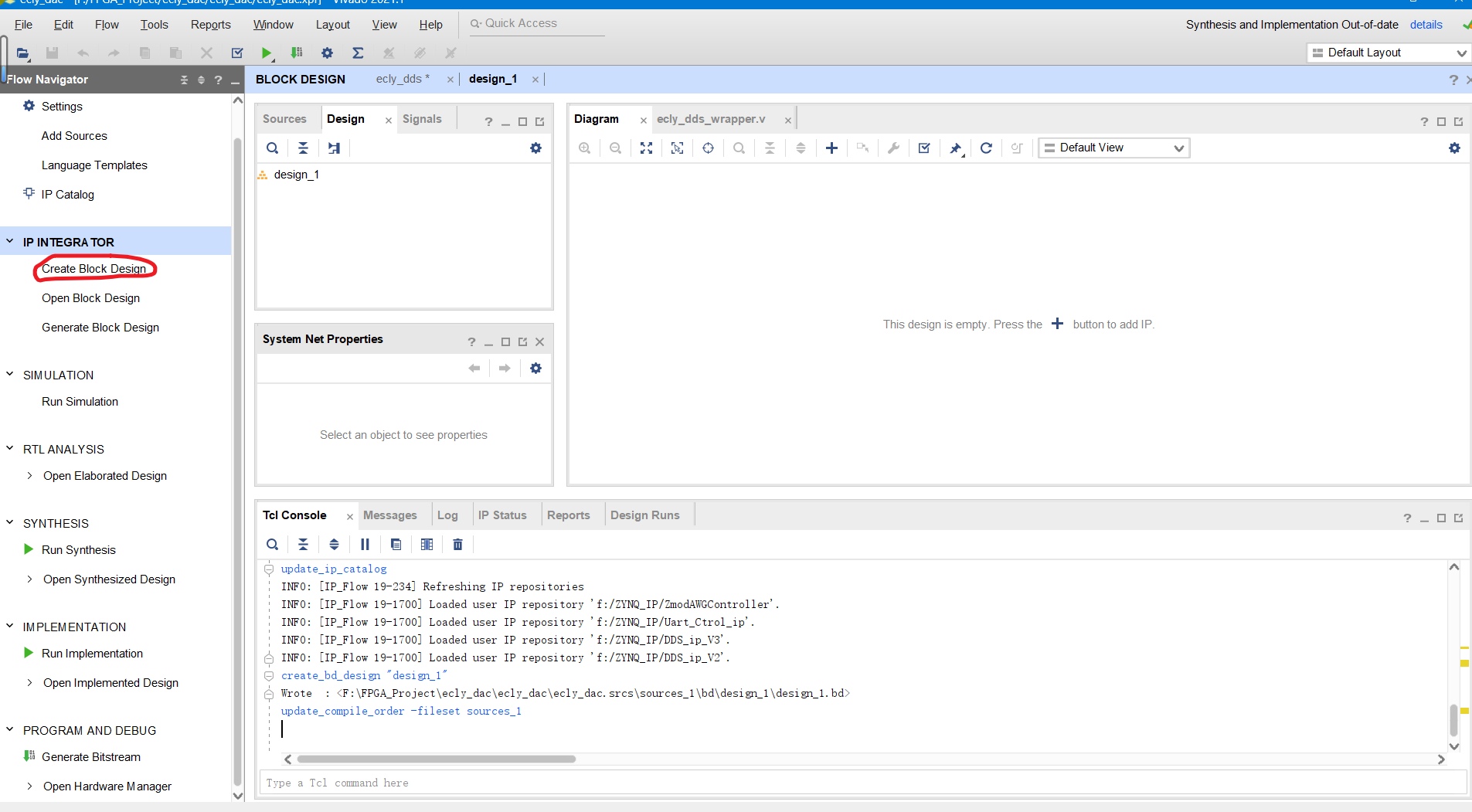

在设置中导入三个下载好的ip,然后电机“block design”

然后就得到了以上这个界面

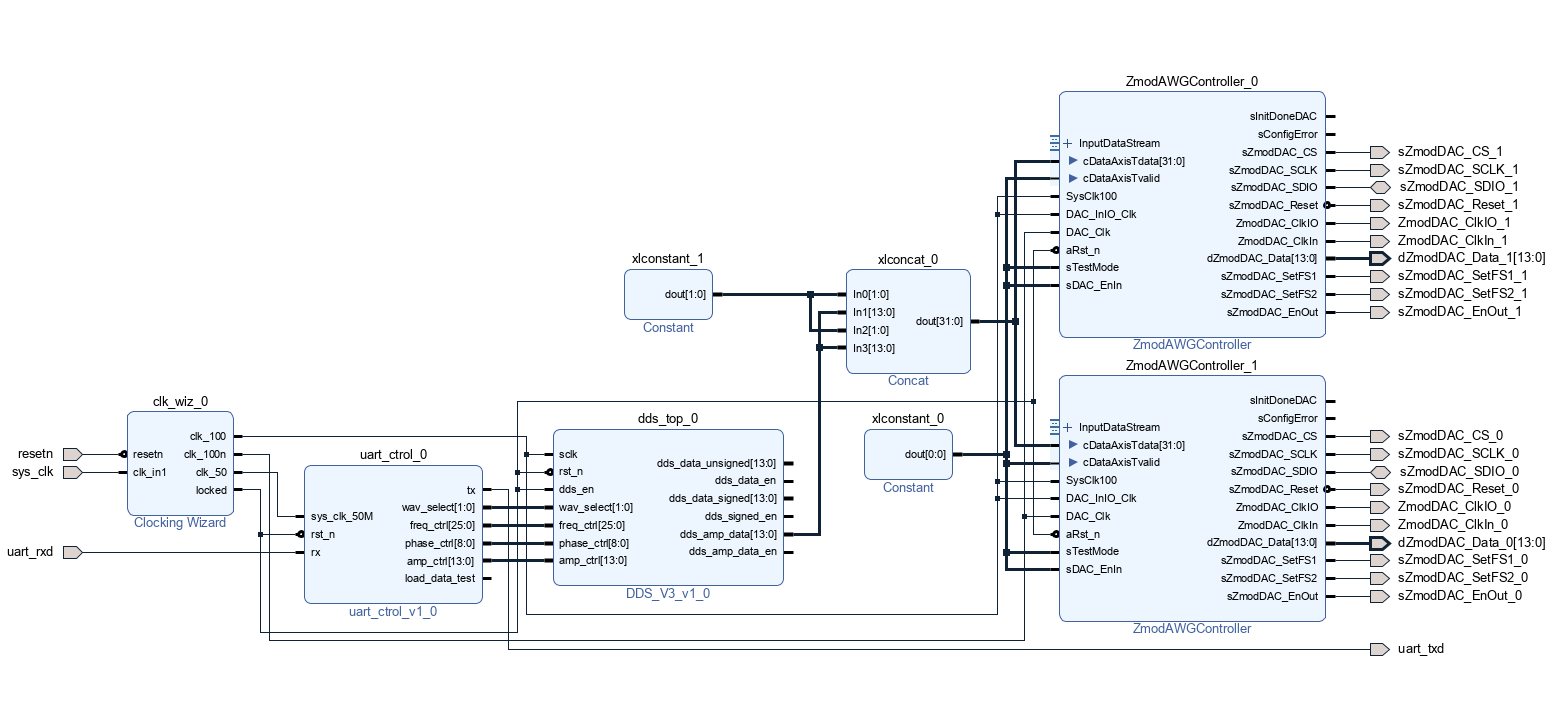

最后根据上面的示意图添加对应的ip,得到工程图

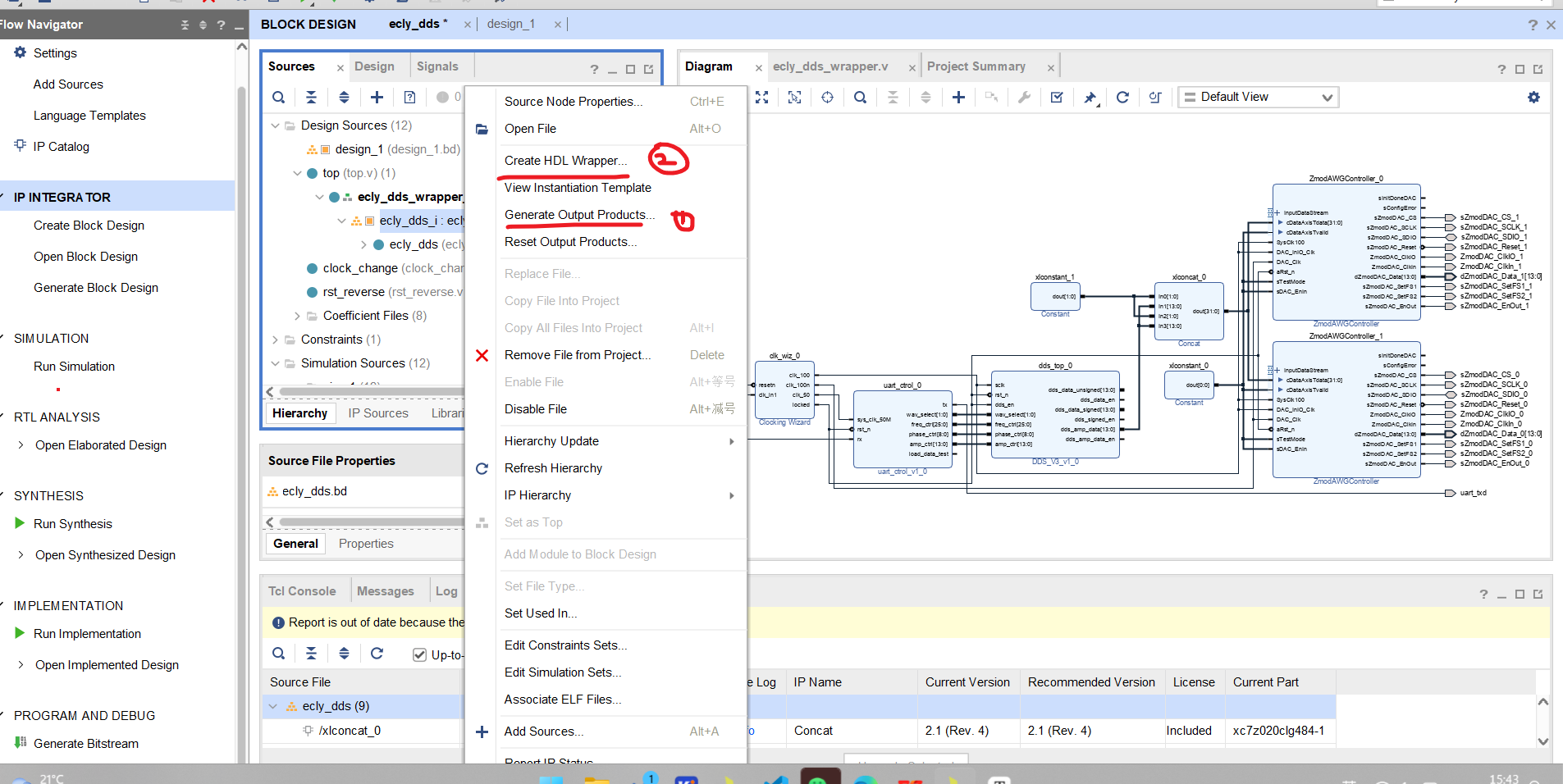

然后生成顶层文件,在做这一步之前先看一下注意事项 如果内部修改了,得重新生成顶层文件

②注意事项

③分配好管脚

若使用官方的板子,则用笔者的xdc文件就可以直接使用,否则需要对应自己板卡做对应引脚的修改,以下是笔者的管脚约束

## 125MHz Clock

set_property -dict { PACKAGE_PIN D18 IOSTANDARD LVCMOS33 } [get_ports { sys_clk }]; #IO_L12P_T1_MRCC Sch=sysclk

create_clock -add -name sys_clk_pin -period 8.00 -waveform {0 4} [get_ports { sys_clk }];

## Buttons_rst

set_property -dict { PACKAGE_PIN C17 IOSTANDARD LVCMOS33 } [get_ports { resetn}];

## USART

set_property -dict {PACKAGE_PIN H17 IOSTANDARD LVCMOS33} [get_ports uart_rxd]

set_property -dict {PACKAGE_PIN H18 IOSTANDARD LVCMOS33} [get_ports uart_txd]

## DAC

set_property -dict {PACKAGE_PIN W16 IOSTANDARD LVCMOS18} [get_ports ZmodDAC_ClkIn_0]

set_property -dict {PACKAGE_PIN W17 IOSTANDARD LVCMOS18} [get_ports ZmodDAC_ClkIO_0]

## DAC SPI

set_property -dict {PACKAGE_PIN Y14 IOSTANDARD LVCMOS18} [get_ports sZmodDAC_SDIO_0]

set_property DRIVE 4 [get_ports sZmodDAC_SDIO_0]

set_property -dict {PACKAGE_PIN AA14 IOSTANDARD LVCMOS18} [get_ports sZmodDAC_CS_0]

set_property DRIVE 4 [get_ports sZmodDAC_CS_0]

set_property -dict {PACKAGE_PIN AA13 IOSTANDARD LVCMOS18} [get_ports sZmodDAC_SCLK_0]

set_property DRIVE 4 [get_ports sZmodDAC_SCLK_0]

set_property -dict {PACKAGE_PIN W15 IOSTANDARD LVCMOS18} [get_ports sZmodDAC_SetFS1_0]

set_property -dict {PACKAGE_PIN Y15 IOSTANDARD LVCMOS18} [get_ports sZmodDAC_SetFS2_0]

set_property -dict {PACKAGE_PIN Y13 IOSTANDARD LVCMOS18} [get_ports sZmodDAC_Reset_0]

set_property -dict {PACKAGE_PIN AA22 IOSTANDARD LVCMOS18} [get_ports sZmodDAC_EnOut_0]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[13]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[12]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[11]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[10]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[9]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[8]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[7]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[6]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[5]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[4]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[3]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[2]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[1]}]

set_property IOSTANDARD LVCMOS18 [get_ports {dZmodDAC_Data_0[0]}]

set_property PACKAGE_PIN V13 [get_ports {dZmodDAC_Data_0[13]}]

set_property PACKAGE_PIN W13 [get_ports {dZmodDAC_Data_0[12]}]

set_property PACKAGE_PIN AB14 [get_ports {dZmodDAC_Data_0[11]}]

set_property PACKAGE_PIN AB15 [get_ports {dZmodDAC_Data_0[10]}]

set_property PACKAGE_PIN V14 [get_ports {dZmodDAC_Data_0[9]}]

set_property PACKAGE_PIN V15 [get_ports {dZmodDAC_Data_0[8]}]

set_property PACKAGE_PIN Y20 [get_ports {dZmodDAC_Data_0[7]}]

set_property PACKAGE_PIN Y21 [get_ports {dZmodDAC_Data_0[6]}]

set_property PACKAGE_PIN AA19 [get_ports {dZmodDAC_Data_0[5]}]

set_property PACKAGE_PIN AA18 [get_ports {dZmodDAC_Data_0[4]}]

set_property PACKAGE_PIN AB20 [get_ports {dZmodDAC_Data_0[3]}]

set_property PACKAGE_PIN AB22 [get_ports {dZmodDAC_Data_0[2]}]

set_property PACKAGE_PIN Y18 [get_ports {dZmodDAC_Data_0[1]}]

set_property PACKAGE_PIN Y19 [get_ports {dZmodDAC_Data_0[0]}]

④综合上板

在上板综合之前,一定要注意,这个板子的内部reset引脚是一直拉低的,若设计的复位低电平复位的,那么直接接入就会一直拉低,导致整个板子不工作,所以得取反

然后就可以愉快的生成比特流文件了

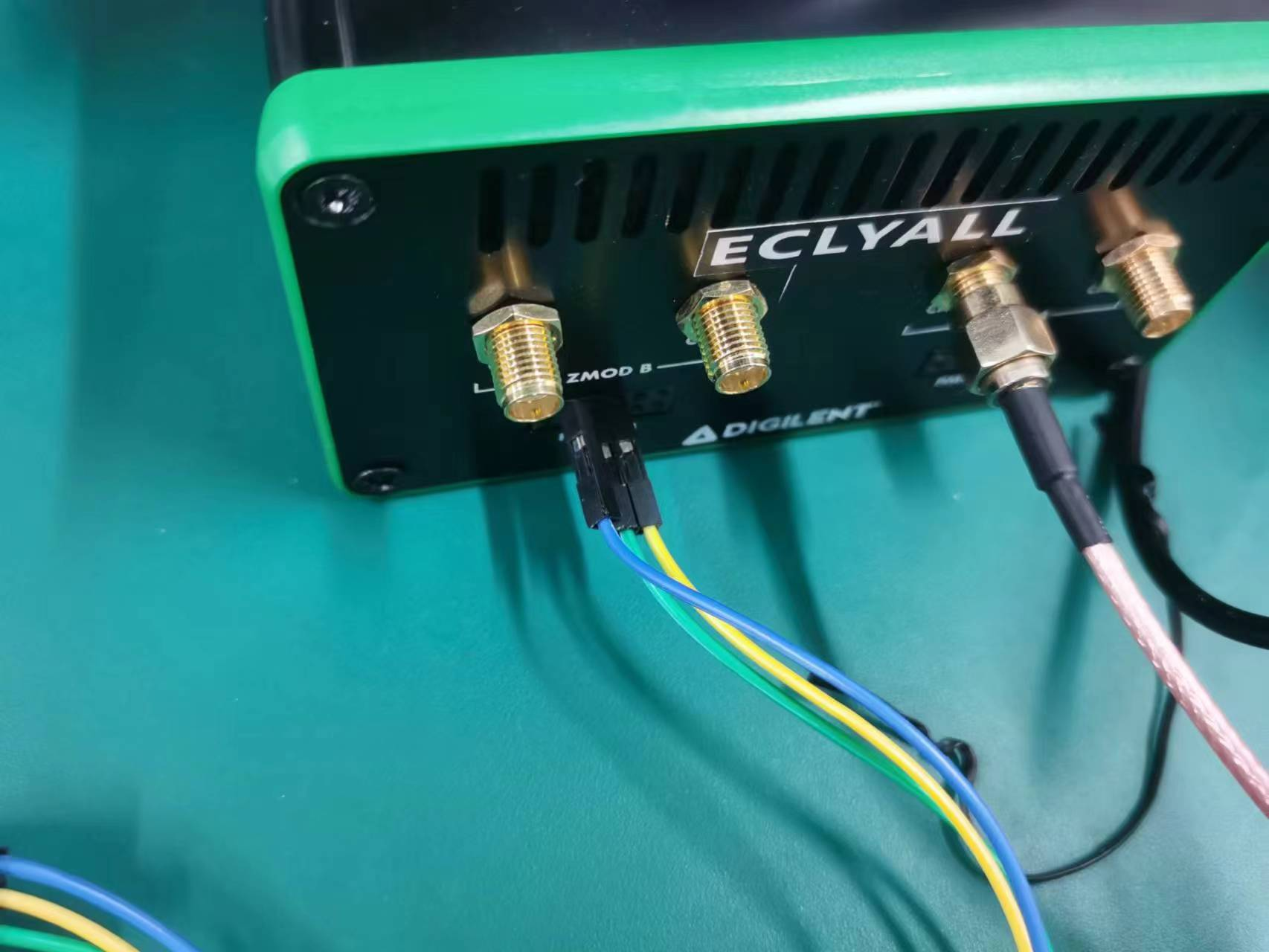

⑤实物接线

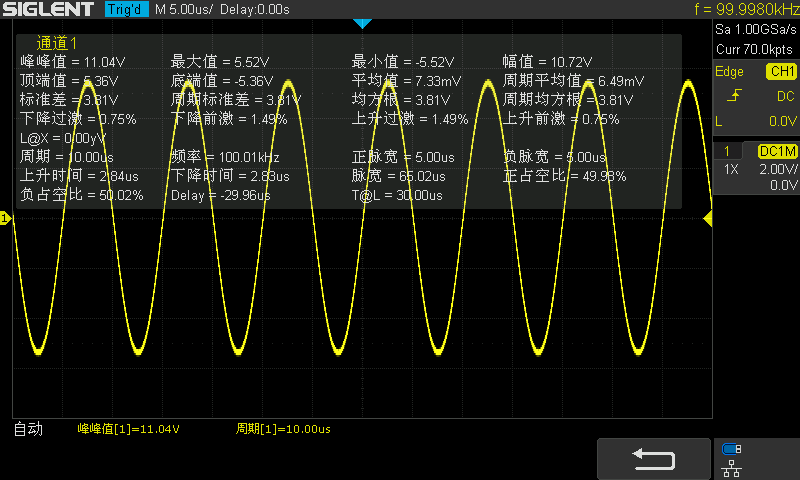

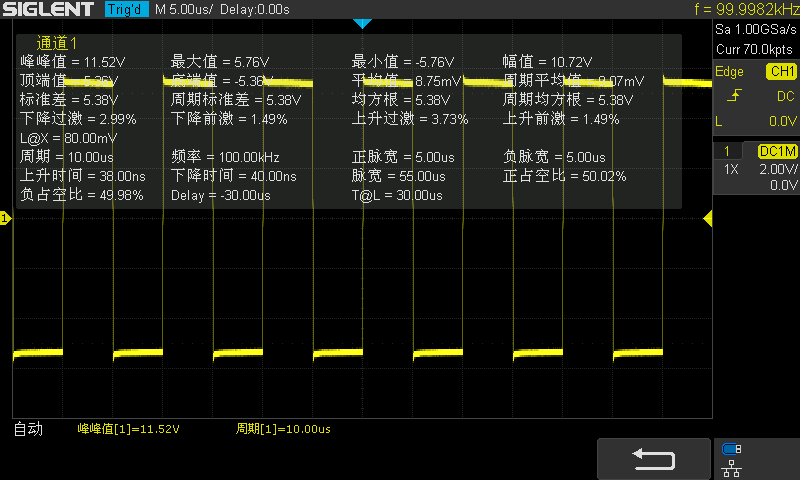

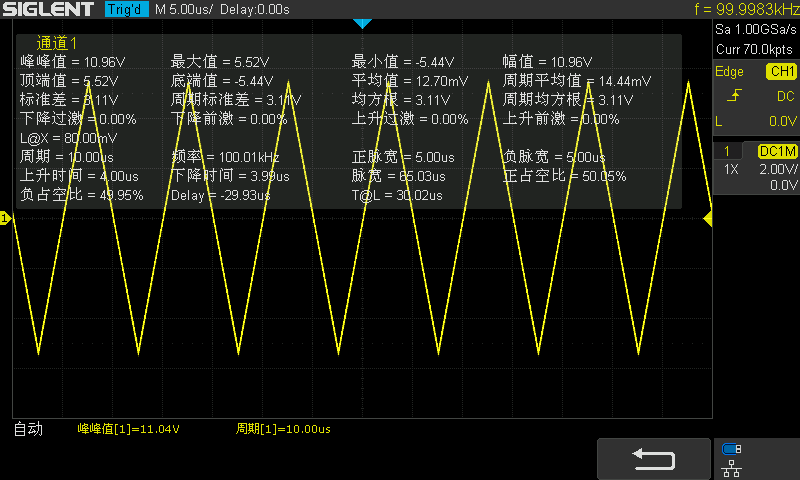

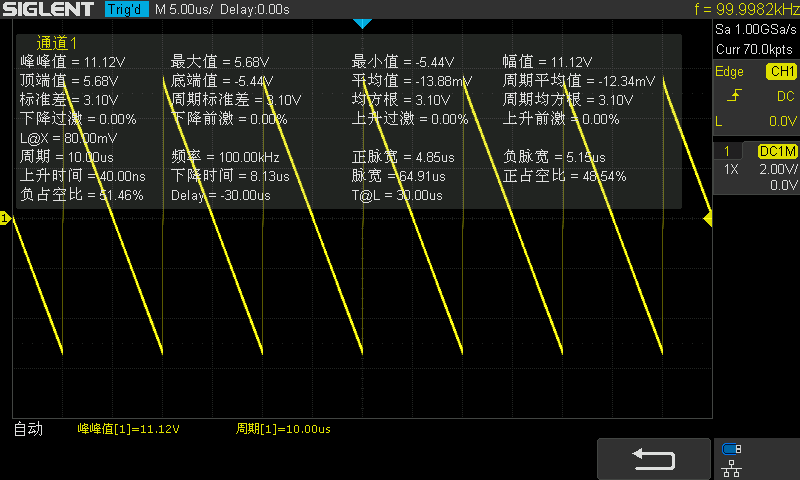

⑥测试输出

上位机软件

这个app控制器,需要matlab2021A的runningtime 所以可以自行下载一个,然后安装这个软件,也可以用matlab打开笔者的工程文件,也是一样的,看哪个方便即可

浙公网安备 33010602011771号

浙公网安备 33010602011771号