基于EPCLYPS的DDS控制器(二)

关于ZmodAWGController

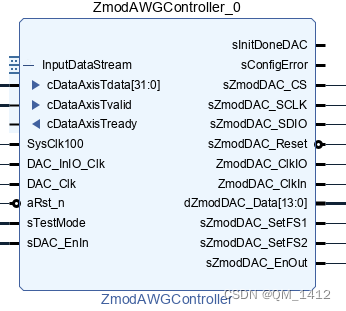

ZmodAWGController 介绍

-

双击IP核,进入的第一个界面会有Ch1 Gain Static Configuration的选项修改为 “0”-->"1",其余不用修改

-

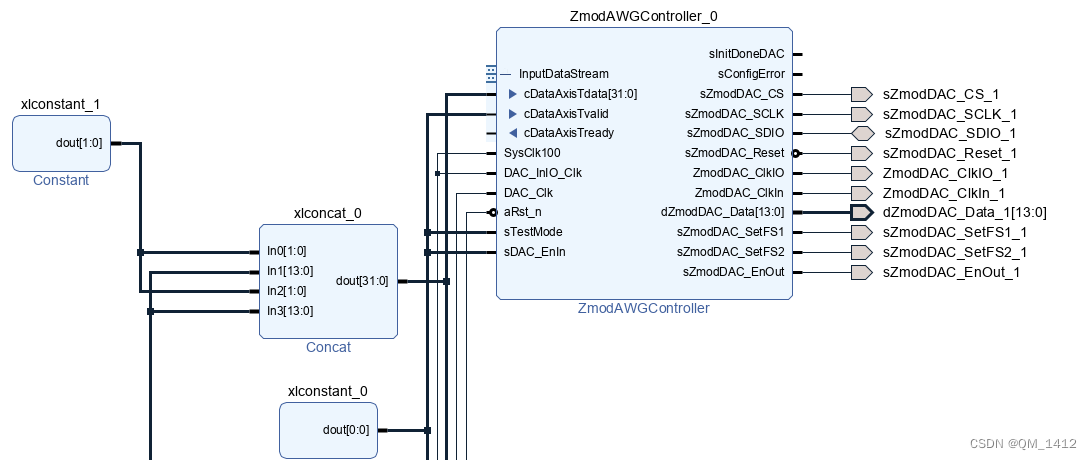

其中右边的端口是连接SYZYGY Ports接口(若不用DAC,则sInitDoneDAC和sConfigError可以不用连接)

-

关于左边端口

SysClk100 和 DAC_InIO_Clk 需要连接100M的时钟

DAC_Clk需要连接100M的时钟,但是需要相位相差90

sTestMode和sDAC_Enln直接置"1"即可

-

关于InputDataStream

cDataAxisTdata[31:0] 和 cDataAxisTvalid连接前端来的数据

-

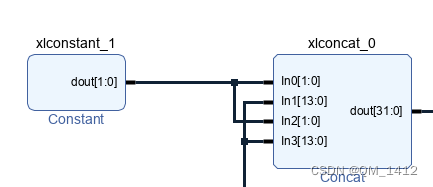

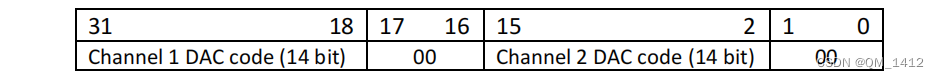

关于cDataAxisTdata[31:0]

输入的是31位的数据,但是dac自身是14位的,官方为了传输快速,用了32位数,双通路传输,所以自己做的时候,需要做一点拼接操作

AWG IP参考连接

关于DDS ip控制

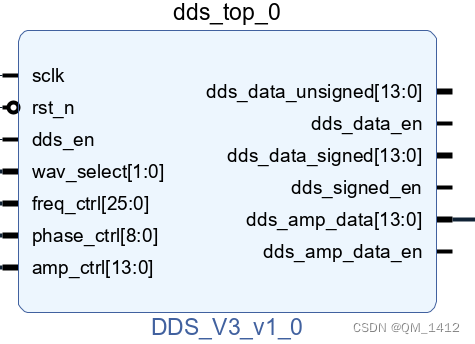

dds ip 介绍

-

右边端口

dds_data_unsigned:无符号数据输出

dds_data_en: 数据输出使能

dds_data_signed:有符号数据输出

dds_signed_en: 有数据输出使能

dds_amp_data:幅度控制有符号数据输出

dds_amp_data_en: 可以幅度控制有数据输出使能

-

左边端口

dds_en:dds使能引脚

wav_select:波形选择(0:正弦,1:三角波,2:锯齿波,3:方波)

freq_ctrl:频率控制 (只需输入想要的频率即可,比如400KHz,就输入400000)

phase_ctrl:相位控制(只需输入想要的相位即可,比如45°,就输入45)

amp_ctrl:幅度控制

dds ip 的一些注意事项

- 幅度控制这个需要注意一下,需要转换成幅度控制字,比如想输出幅值为3V的信号,则输入(3/5)*2^13

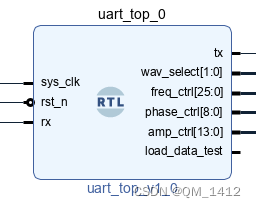

关于串口接收控制

串口ip的注意事项

- 本模块用的时钟是 50M的时钟,不然会有问题,注意!!!!!!!!

浙公网安备 33010602011771号

浙公网安备 33010602011771号