摘要:

阅读全文

posted @ 2025-05-12 20:04

颜小雀

阅读(30)

评论(0)

推荐(0)

摘要:

/* Exception Syndrome register bits and bobs */ #define ESR_EC_SHIFT U(26) #define ESR_EC_MASK U(0x3f) #define ESR_EC_LENGTH U(6) #define ESR_ISS_SHIF 阅读全文

posted @ 2025-05-12 16:46

颜小雀

阅读(101)

评论(0)

推荐(0)

摘要:

在 ARM 架构中,寄存器命名和使用根据架构模式(32位或64位)有所不同。对于 ARM 32-bit 模式(AArch32) 和 ARM 64-bit 模式(AArch64),寄存器的命名规则以及它们的功能有一些区别。 AArch32(ARM 32-bit) 在 AArch32 模式下,通用寄存器 阅读全文

posted @ 2025-05-12 13:49

颜小雀

阅读(154)

评论(0)

推荐(0)

摘要:

在 ARM 架构中,无论是 32 位还是 64 位模式下,都有不同的处理器模式和相应的寄存器资源。这些模式决定了当前执行环境的特权级别以及可用的寄存器集合。以下是 ARM 在 64 位(AArch64)和 32 位(AArch32)架构下的不同模式及其对应的寄存器资源概述。 AArch64 (ARM 阅读全文

posted @ 2025-05-12 11:12

颜小雀

阅读(275)

评论(0)

推荐(0)

摘要:

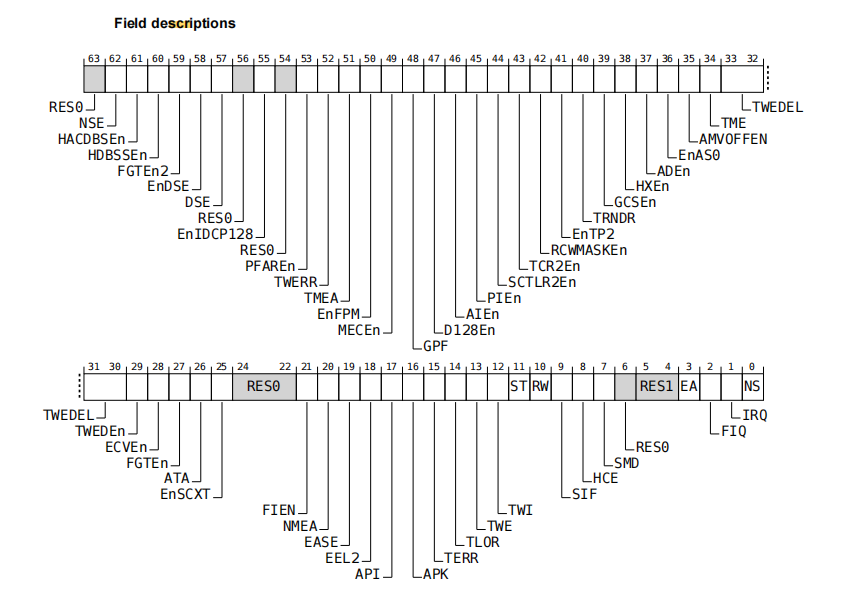

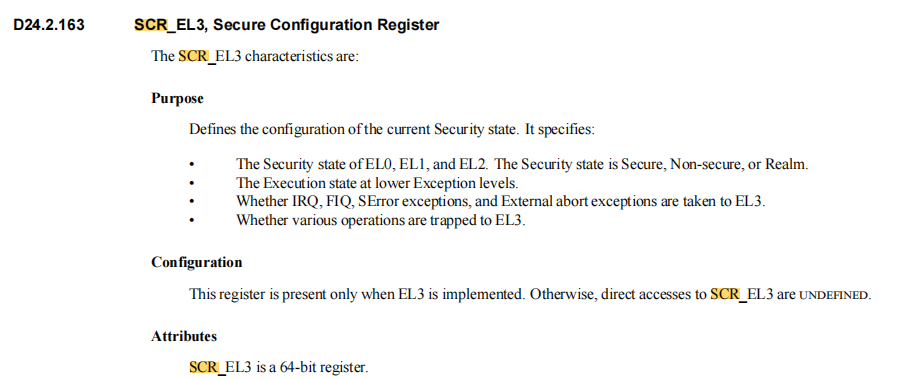

在 OP-TEE 适配 ARMv7 的 SMC 代码中,当处理来自 Non-Secure World(非安全世界) 的请求时,进入 smc_from_nsec 时需要将 SCR(Secure Configuration Register) 的 NS(bit 0) 和 FIQ(bit 2) 位设置为 阅读全文

posted @ 2025-05-12 10:55

颜小雀

阅读(140)

评论(0)

推荐(0)

浙公网安备 33010602011771号

浙公网安备 33010602011771号