ARMv7 SMC OPTEE 切换中的SCR寄存器的NS,FIQ,EA bit状态

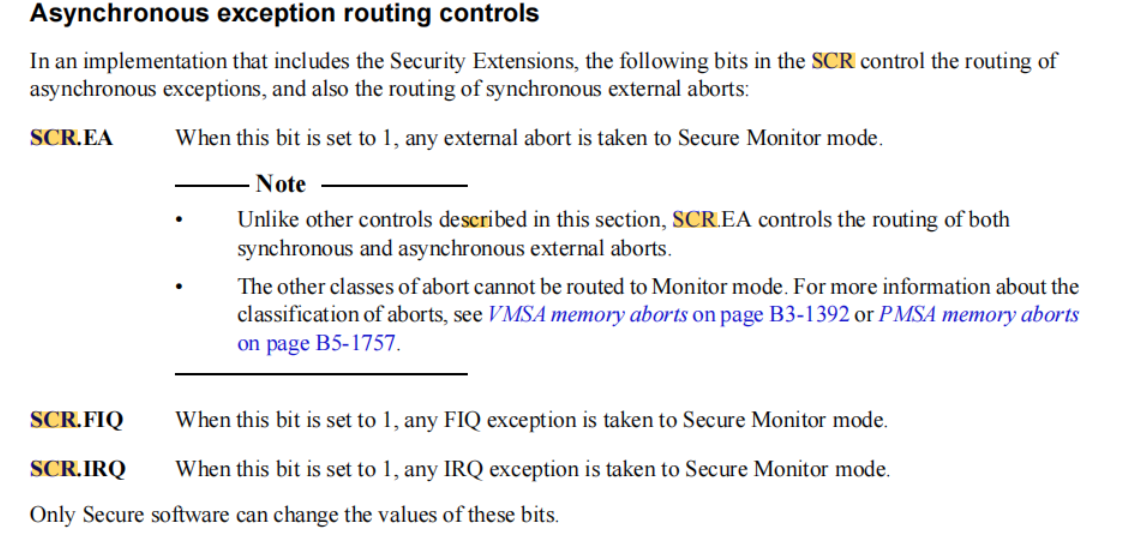

在 OP-TEE 适配 ARMv7 的 SMC 代码中,当处理来自 Non-Secure World(非安全世界) 的请求时,进入 smc_from_nsec 时需要将 SCR(Secure Configuration Register) 的 NS(bit 0) 和 FIQ(bit 2) 位设置为 0,这是为了确保以下关键安全性和稳定性需求:

1. 确保处理器处于 Secure 状态

- NS 位(bit 0):

- NS = 1:处理器处于 Non-Secure 状态。

- NS = 0:处理器处于 Secure 状态。

- 目的:

在处理 SMC 请求时,必须确保处理器处于 Secure 状态,以防止非安全代码访问安全资源或破坏安全上下文。- 为什么设置 NS=0:

当 Non-Secure 代码调用 SMC 指令时,处理器会切换到 Monitor 模式(由 SCR 控制)。ATF(ARM Trusted Firmware)在处理完上下文切换后,会调用 OP-TEE 的smc_from_nsec。此时,若不将 NS 位设置为 0,处理器可能仍处于 Non-Secure 状态,导致安全逻辑失效(如 TA 无法正确运行)。

- 为什么设置 NS=0:

2. 禁用 FIQ 中断进入 Monitor 模式

- FIQ 位(bit 2):

- FIQ = 1:FIQ 异常触发时,处理器进入 Monitor 模式(而非 FIQ 模式)。

- FIQ = 0:FIQ 异常触发时,处理器进入 FIQ 模式(Non-Secure 状态)。

- 目的:

在处理 SMC 请求时,需 暂时屏蔽 FIQ 中断进入 Monitor 模式,以避免中断处理与当前的安全操作冲突。- 为什么设置 FIQ=0:

如果 FIQ 位保持为 1,当 Secure 世界处理 SMC 请求时,若发生 FIQ 中断,处理器会再次进入 Monitor 模式,导致复杂的上下文切换和潜在的竞态条件。通过设置 FIQ=0,FIQ 中断会直接进入 FIQ 模式(Non-Secure 状态),从而避免干扰 Secure 世界的执行流程。

- 为什么设置 FIQ=0:

3. 遵循 ARM 架构的安全协议

-

ARM TrustZone 要求:

在进入 Secure 状态处理 SMC 请求时,必须确保以下配置:- NS=0:明确标识当前处于 Secure 状态。

- FIQ=0:禁用 FIQ 中断进入 Monitor 模式。

- EA=1(bit 3):启用外部中止(External Abort)进入 Monitor 模式(通常保留为 1)。

示例配置:

SCR &= ~(1 << 0); // NS=0 (Secure 状态) SCR &= ~(1 << 2); // FIQ=0 (FIQ 中断进入 FIQ 模式)

4. 防止中断嵌套和上下文切换的开销

- 上下文切换的代价:

- 若 FIQ 位未设置为 0,Secure 世界处理 SMC 请求时可能发生 FIQ 中断,触发 Monitor 模式切换。

- 后果:

- 增加上下文保存/恢复的开销。

- 可能导致中断嵌套(Nested Interrupts),破坏 SMC 请求的原子性。

- 解决方案:

通过设置 FIQ=0,确保 FIQ 中断不会中断 Secure 世界的执行流程,从而避免嵌套和性能损耗。

5. 实际代码中的体现

在 OP-TEE 的 smc_from_nsec 中,SCR 的修改通常通过汇编指令实现。例如:

// 保存当前 SCR 值

mrc p15, 0, r0, c1, c1, 0 // 读取 SCR 到 r0

// 设置 NS=0, FIQ=0

bic r0, r0, #1 << 0 // 清除 NS 位

bic r0, r0, #1 << 2 // 清除 FIQ 位

// 写回修改后的 SCR

mcr p15, 0, r0, c1, c1, 0 // 将 SCR 写回

6. 总结

| 寄存器位 | 设置值 | 目的 |

|---|---|---|

| NS (bit 0) | 0 |

确保处理器处于 Secure 状态,防止非安全代码干扰安全逻辑。 |

| FIQ (bit 2) | 0 |

禁用 FIQ 中断进入 Monitor 模式,避免上下文切换和中断嵌套,提高稳定性。 |

5. 总结

通过将 SCR 寄存器中的 FIQ 位设置为 0,可以确保在 Secure World 处理 SMC 请求期间,任何触发的 FIQ 中断都不会导致处理器切换到 Monitor 模式。这样做的好处包括减少不必要的上下文切换、保持执行流程的原子性以及简化中断处理逻辑,从而提高系统的稳定性和性能。

1. SCR 寄存器简介

- SCR(Secure Configuration Register):这是一个关键寄存器,用于控制从 Non-Secure 状态到 Secure 状态的转换规则。

- 重要位说明:

- NS(bit 0):决定处理器是否处于 Non-Secure 状态。

0表示 Secure 状态,1表示 Non-Secure 状态。 - FIQ(bit 2):控制 FIQ(Fast Interrupt Request)中断的行为。如果设置为

1,则 FIQ 中断将导致进入 Monitor 模式;若设置为0,则 FIQ 中断会在当前的安全状态下处理。

- NS(bit 0):决定处理器是否处于 Non-Secure 状态。

2. 设置 FIQ=0 的作用

(1) 当 FIQ = 1

- 行为:

如果 SCR 寄存器中的 FIQ 位被设置为1,那么任何触发的 FIQ 中断都会使处理器跳转到 Monitor 模式(即 Secure Monitor)。这是因为 Monitor 模式是 ARM TrustZone 架构中用于在 Secure 和 Non-Secure 状态之间切换的特权模式。 - 影响:

- 上下文切换开销:每次 FIQ 中断发生时,处理器都需要保存当前状态并切换到 Secure Monitor,这增加了额外的上下文切换开销。

- 潜在的竞争条件:频繁的上下文切换可能导致竞争条件,尤其是在处理敏感的 Secure 代码时,如 Trusted Applications (TAs)。

(2) 当 FIQ = 0

- 行为:

如果将 SCR 寄存器中的 FIQ 位设置为0,那么任何触发的 FIQ 中断将在当前的安全状态下处理。也就是说,在 Secure 状态下发生的 FIQ 中断会直接进入 FIQ 模式,而不是 Monitor 模式。 - 好处:

- 减少上下文切换:通过避免不必要的 Monitor 模式切换,减少了上下文保存和恢复的开销,提高了性能。

- 保持执行流程的原子性:确保在 Secure 状态下的操作不会被中断干扰,这对于需要高安全性的操作(如加密、认证等)非常重要。

- 避免中断嵌套:防止由于 FIQ 中断导致的复杂中断嵌套问题,简化了中断处理逻辑。

3. 实际场景中的应用

假设我们正在处理一个来自 Normal World 的 SMC 请求,该请求需要由 OP-TEE 在 Secure World 中执行某些操作。在这个过程中:

- 初始状态:处理器可能在处理 Normal World 的任务。

- SMC 请求触发:Normal World 发出 SMC 请求,处理器切换到 Secure World。

- 进入

smc_from_nsec:在此函数中,我们需要确保所有配置都符合 Secure World 的要求。因此,我们将 SCR 寄存器中的 FIQ 位设置为0,以保证任何后续的 FIQ 中断不会导致不必要的 Monitor 模式切换。 - 执行 Secure 操作:在 Secure World 中执行必要的操作(如调用 Trusted Application),不受 Non-Secure 中断的影响。

- 返回 Normal World:完成 Secure 操作后,恢复先前的上下文,并返回到 Normal World 继续执行。

4. 示例代码

以下是一个简化的汇编代码片段,展示了如何在 smc_from_nsec 函数中修改 SCR 寄存器:

// 读取当前 SCR 值

mrc p15, 0, r0, c1, c1, 0

// 清除 FIQ 位(设置 FIQ=0)

bic r0, r0, #(1 << 2)

// 写回修改后的 SCR

mcr p15, 0, r0, c1, c1, 0

这段代码首先读取当前的 SCR 值,然后通过 bic 指令清除 FIQ 位(即将其设置为 0),最后将修改后的值写回到 SCR 寄存器。

在 ARM 架构中,特别是涉及到 TrustZone 安全扩展时,SCR(Secure Configuration Register) 寄存器用于配置安全状态和中断处理行为。其中,EA(External Abort)位(bit 3) 的设置对于确保系统的安全性与稳定性至关重要。以下是关于为什么通常会将 EA 位设置为 1(即启用外部中止进入 Monitor 模式)的详细解释:

1. SCR 寄存器中的 EA 位

- 位置:位于 SCR 寄存器的第 3 位。

- 作用:

- 当 EA 位设置为

1时,任何外部中止(如访问未映射内存或执行数据中止)都会导致处理器进入 Monitor 模式。 - 如果 EA 位设置为

0,则外部中止将在当前的安全状态下处理。

- 当 EA 位设置为

2. 外部中止(External Abort)简介

- 定义:外部中止指的是由于外部设备或内存系统的问题导致的异常情况,例如尝试访问一个不存在或不可访问的地址。

- 影响:

- 可能破坏当前正在执行的任务,无论是 Secure World 还是 Non-Secure World。

- 需要特别注意的是,当外部中止发生在 Secure World 中时,它可能泄露安全信息或导致安全漏洞。

3. 设置 EA=1 的原因

(1) 确保安全性的完整性和隔离性

- 防止安全信息泄露:如果外部中止发生在 Secure World 而不进入 Monitor 模式,则可能导致异常处理程序在 Secure World 内运行。这增加了安全信息被泄露的风险,因为异常处理代码可能没有充分考虑安全性。

- 保持隔离性:通过使外部中止强制进入 Monitor 模式,可以确保所有外部中止都由安全监控代码处理,从而维持了 Secure World 和 Non-Secure World 之间的严格隔离。

(2) 统一的异常处理策略

- 简化异常处理逻辑:通过统一将外部中止导向 Monitor 模式,可以使异常处理更加一致和简单。Monitor 模式可以提供一种机制来决定如何处理这些异常,包括是否将其转发到相应的世界(Secure 或 Non-Secure),或者采取其他适当的措施。

- 灵活性增强:Monitor 模式可以根据具体情况灵活地响应外部中止。例如,它可以检查异常的原因,并根据需要决定是终止当前操作、修复问题还是报告错误。

(3) 提高系统的健壮性

- 避免潜在的系统崩溃:如果没有适当的处理,外部中止可能会导致系统不稳定或崩溃。通过让 Monitor 模式处理这些异常,可以增加额外的一层保护,确保即使发生外部中止,系统也能以受控的方式响应。

- 支持错误恢复机制:Monitor 模式可以实现更复杂的错误恢复机制,比如重启受影响的部分而不影响整个系统的运行。

4. 示例场景

假设有一个嵌入式系统使用 OP-TEE 实现安全功能,该系统同时运行着 Normal World 和 Secure World 应用。如果 Normal World 中的应用程序尝试访问无效的内存地址,触发了一个外部中止:

-

EA=1(默认设置):此外部中止会导致处理器切换到 Monitor 模式,在这里可以评估异常的性质并决定如何处理。例如,可以选择忽略该异常(如果是预期的行为),或将控制权转移回 Non-Secure World 让其处理异常,或者采取其他适当的行动。

-

EA=0:在这种情况下,外部中止会在 Non-Secure World 中直接处理。虽然这可能适用于某些特定的情况,但它也可能带来安全隐患,尤其是当异常处理程序不够健壮时。

5. 示例代码

以下是一个简化的汇编代码片段,展示了如何在初始化或进入 Secure World 时配置 SCR 寄存器,包括设置 EA 位:

// 读取当前 SCR 值

mrc p15, 0, r0, c1, c1, 0

// 设置 EA=1 (启用外部中止进入 Monitor 模式)

orr r0, r0, #(1 << 3)

// 写回修改后的 SCR

mcr p15, 0, r0, c1, c1, 0

这段代码首先读取当前的 SCR 值,然后通过 orr 指令设置 EA 位(即将其设置为 1),最后将修改后的值写回到 SCR 寄存器。

6. 总结

将 SCR 寄存器中的 EA 位设置为 1 是为了确保所有外部中止都能进入 Monitor 模式,这有助于维护系统的安全性、简化异常处理逻辑以及提高整体的健壮性。通过这种方式,ARM TrustZone 架构能够更好地管理跨 Secure 和 Non-Secure Worlds 的异常处理流程,确保在遇到外部中止等异常情况时,系统仍能稳定且安全地运行。

浙公网安备 33010602011771号

浙公网安备 33010602011771号