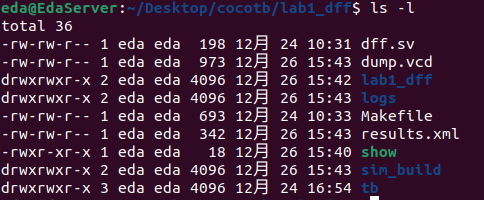

cocotb lab1 DFF

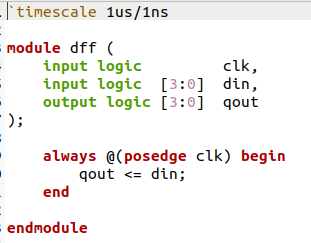

dff.v

`timescale 1us/1ns

module dff (

input logic clk,

input logic [3:0] din,

output logic [3:0] qout

);

always @(posedge clk) begin

qout <= din;

end

endmodule

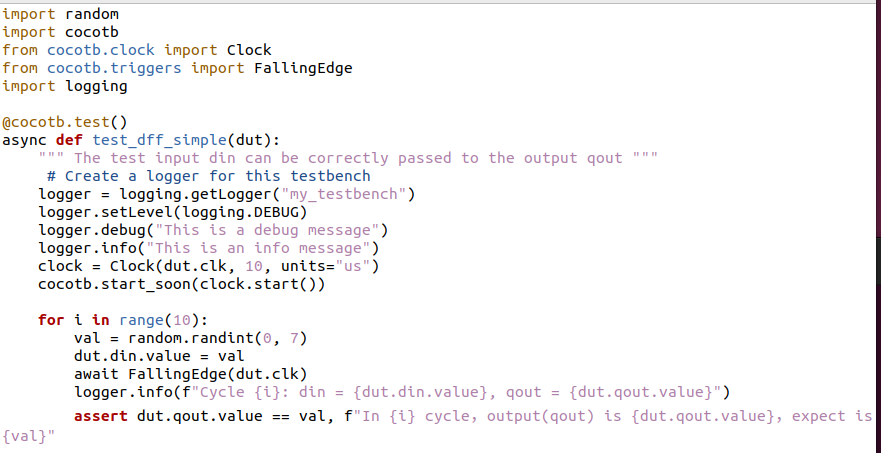

tb/test.py

import random

import cocotb

from cocotb.clock import Clock

from cocotb.triggers import FallingEdge

import logging

@cocotb.test()

async def test_dff_simple(dut):

""" The test input din can be correctly passed to the output qout """

# Create a logger for this testbench

logger = logging.getLogger("my_testbench")

logger.setLevel(logging.DEBUG)

logger.debug("This is a debug message")

logger.info("This is an info message")

clock = Clock(dut.clk, 10, units="us")

cocotb.start_soon(clock.start())

for i in range(10):

val = random.randint(0, 7)

dut.din.value = val

await FallingEdge(dut.clk)

logger.info(f"Cycle {i}: din = {dut.din.value}, qout = {dut.qout.value}")

assert dut.qout.value == val, f"In {i} cycle,output(qout) is {dut.qout.value},expect is {val}"

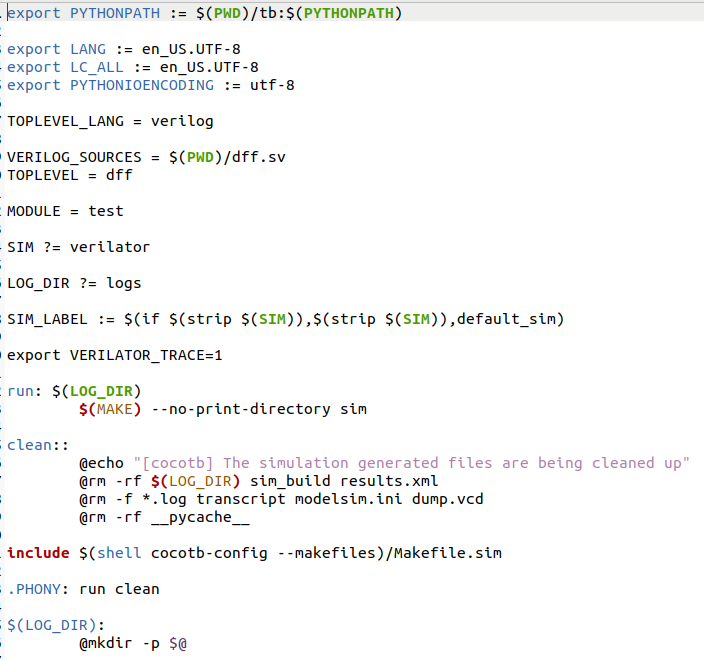

Makefile

export PYTHONPATH := $(PWD)/tb:$(PYTHONPATH)

export LANG := en_US.UTF-8

export LC_ALL := en_US.UTF-8

export PYTHONIOENCODING := utf-8

TOPLEVEL_LANG = verilog

VERILOG_SOURCES = $(PWD)/dff.sv

TOPLEVEL = dff

MODULE = test

SIM ?= verilator

LOG_DIR ?= logs

SIM_LABEL := $(if $(strip $(SIM)),$(strip $(SIM)),default_sim)

export VERILATOR_TRACE=1

run: $(LOG_DIR)

$(MAKE) --no-print-directory sim

clean::

@echo "[cocotb] The simulation generated files are being cleaned up"

@rm -rf $(LOG_DIR) sim_build results.xml

@rm -f *.log transcript modelsim.ini dump.vcd

@rm -rf __pycache__

include $(shell cocotb-config --makefiles)/Makefile.sim

.PHONY: run clean

$(LOG_DIR):

@mkdir -p $@

-----------

make

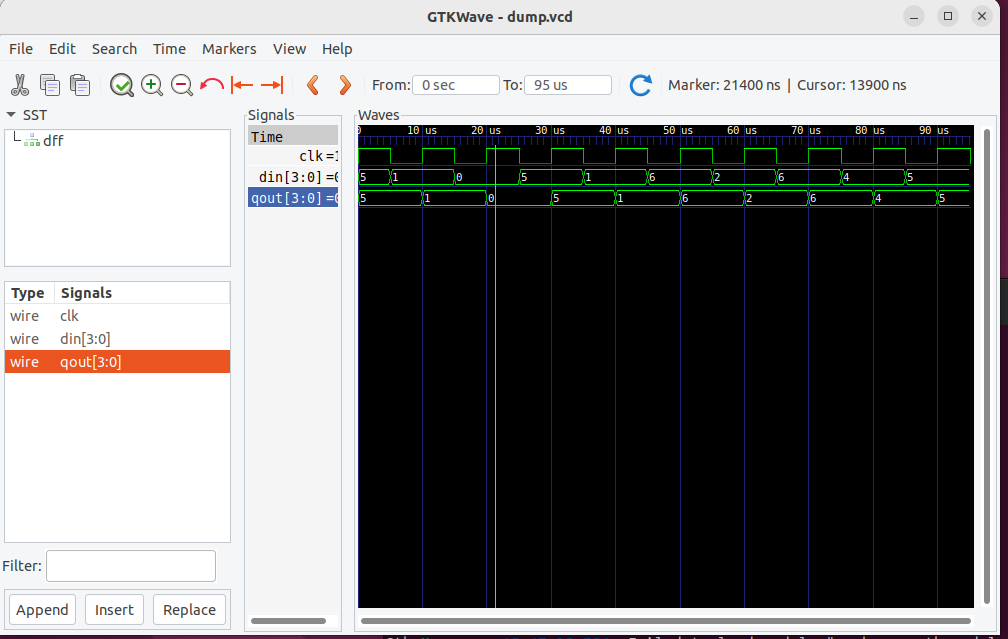

gtkwave dump.vcd

浙公网安备 33010602011771号

浙公网安备 33010602011771号