Majority [məˈdʒɔːrəti] 大多数,多数票

多数表决器的设计

有三位同学参加投票表决,每人手里有一个按键,两人以上同意(按键按下)则通过(指示灯亮),否则不通过(指示灯不亮),试使用搭建电路,完成多数表决功能。

//------------------------------------ // 多数表决器 //------------------------------------

module Majority(a, b, c, out) ;

/*这个模块定义了一个多数表决电路。它接收三个输入(a、b、c)和一个输出(out)。输出值由输入的AND操作和OR操作的结果确定。*/

input a, b, c ;

output out ;

assign out = (a & b)|(a & c)|(b & c) ;

/*在模块中,assign语句将AND和OR操作的结果分配给输出变量。如果任何一个输入为1,则相应的输出位将为1。如果所有三个输入都为0,则输出位也将为0。*/

endmodule

/* 总体而言,这个模块可以用于实现数字电路中的简单多数表决算法。 */

module Majority_TB; // 声明模块名为Majority

reg [2:0] count; // 定义一个3位计数器,用于记录输入信号中1的个数

wire out; // 定义一个输出信号,用于表示多数表决器的输出结果

// 实例化多数表决器

Majority m(count[0], count[1], count[2], out);

// 生成3输入变量的8个输入取值

initial

begin

count = 3'b000; // 将计数器初始化为000

repeat (8) begin // 循环8次

#100; // 等待100个时钟周期

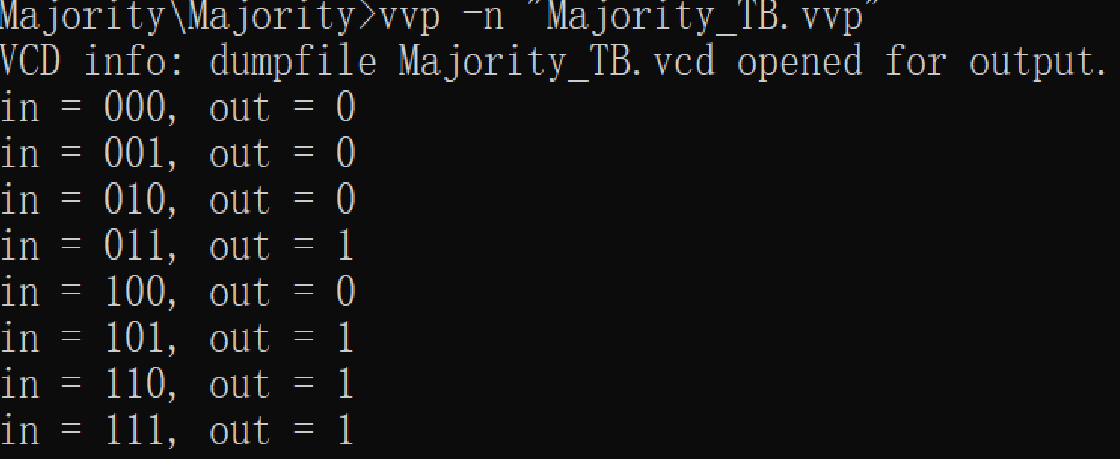

$display("in = %b, out = %b", count, out); // 显示当前输入和输出状态

count = count + 3'b001; // 将计数器加1

end

end

initial begin

$dumpfile("Majority_TB.vcd"); //

$dumpvars; //无参数,表示设计中的所有信号都将被记录

$dumpvars(0,Majority_TB);

end

endmodule

geda.bat

set iverilog_path=C:\iverilog\bin;

set gtkwave_path=C:\iverilog\gtkwave\bin;

set path=%iverilog_path%%gtkwave_path%%path%

set source_module=%1

set testbentch_module=%1_TB

iverilog -o "%testbentch_module%.vvp" -y ./lib/*.v %testbentch_module%.v %source_module%.v

vvp -n "%testbentch_module%.vvp"

set gtkw_file="%testbentch_module%.gtkw"

if exist %gtkw_file% (gtkwave %gtkw_file%) else (gtkwave "%testbentch_module%.vcd")

pause

浙公网安备 33010602011771号

浙公网安备 33010602011771号