2024-03-13日记录:

博客上是我的初稿随手记,后期 贪吃蛇完整教程(手把手)整理如下:

贪吃蛇九:蛇身控制 https://mp.weixin.qq.com/s/4qgOI4xP1nzufEQLQpFUHA

贪吃蛇八:状态机设计 https://mp.weixin.qq.com/s/CvHQbjO3KZDDgxz_ohPW1A

贪吃蛇七:食物(苹果)的产生 https://mp.weixin.qq.com/s/96v8wyQItoolwcWGkFa7hw

贪吃蛇六:VGA 驱动模块图片显示 https://mp.weixin.qq.com/s/HEQYovUSbaiEDgDyCWD14g

贪吃蛇五:VGA 驱动模块字符显示 https://mp.weixin.qq.com/s/8Boc8PhwX4bqQRbTTwQuaA

贪吃蛇四:VGA 驱动模块色块显示 https://mp.weixin.qq.com/s/qEuAx5d1kHWJgiNNiaobKg

贪吃蛇三:计分模块 https://mp.weixin.qq.com/s/xIe5XdHqoc2vF4A5eH2snA

贪吃蛇二:数码管驱动模块 https://mp.weixin.qq.com/s/4p4HkPJ53kQS4s2-575plQ

贪吃蛇一:https://mp.weixin.qq.com/s/NNGnLUz3ZsDcCyDHNeRuKQ(包含源代码工程)

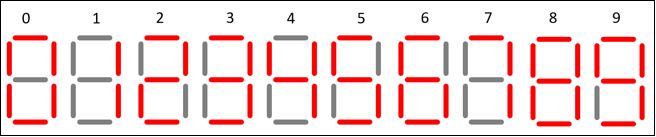

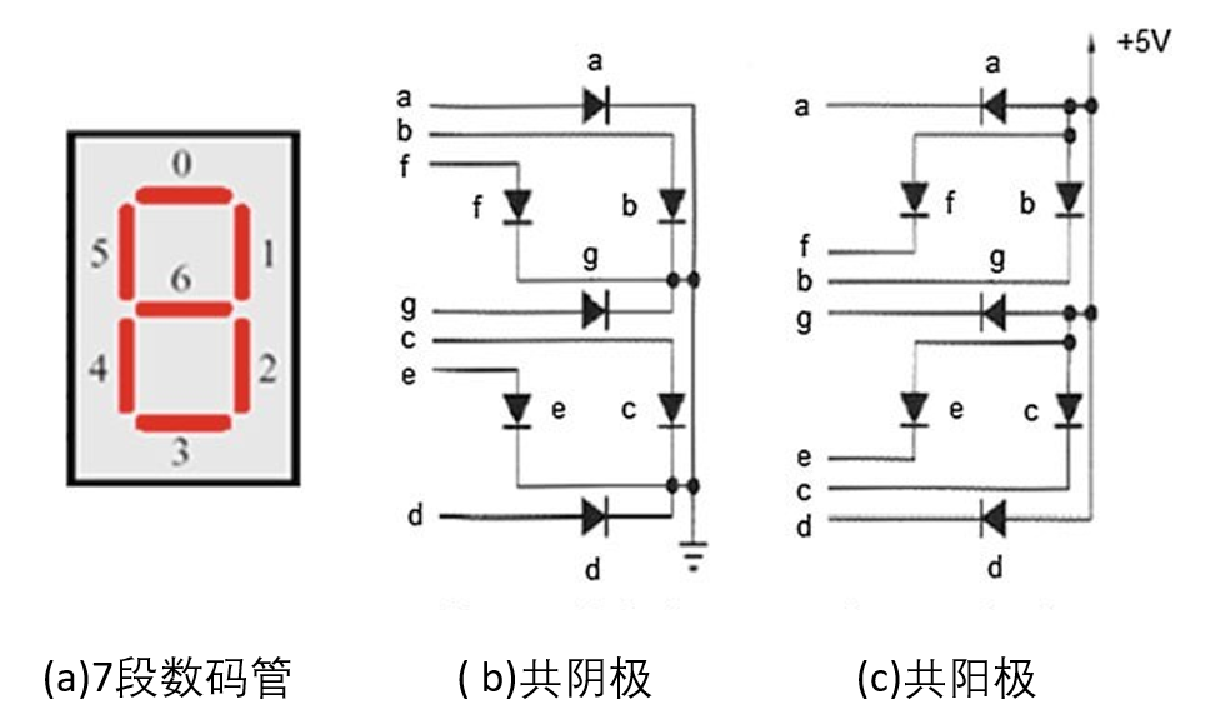

在数字电路中,7段数码管是一个应用非常广泛的显示器件,它有7个可独立点亮的线段(LED灯) 用户可以通过控制点亮7个线段中某些线段来拼成10个数字和某些字母,从而完成显示任务。

目前有两种类型的7段数码管显示器件:共阴极数码管和共阳极数码管。

共阴极数码管是7个LED的阴极端一起接地,每个阳极端单独连接到控制端(比如接到FPGA的GPIO pin)。共阴极数码管器件是高电平有效。

共阳极数码管是7个LED的阳极端一起连接VCC,每个阴极端单独接控制端(比如接到FPGA的GPIO pin)。 共阳极数码管器件是低电平有效。

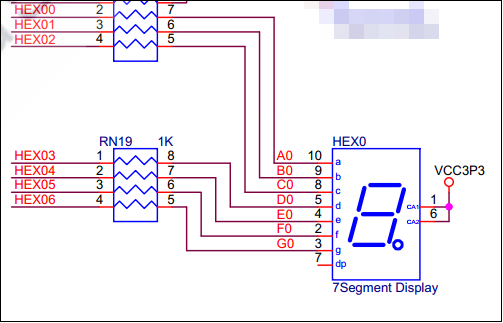

DE10-Standard开发板(DE1-SOC、DE2-115)上面的数码管是共阳极数码管,所以是低电平点亮。

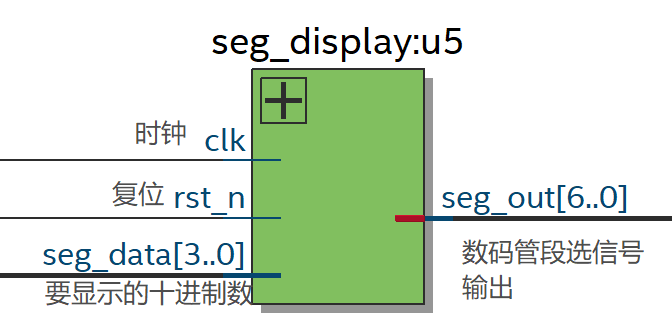

数码管显示控制模块seg_display.v的信号描述如下:

| 信号 | 描述 |

| clk | 时钟 |

| rst_n | 复位 |

| seg_data | 要显示的数 |

| seg_out | 数码管段选信号 |

数码管显示控制模块seg_display.v的完整代码如下:

module seg_display( input clk, //系统时钟 input rst_n, //系统复位 input [3:0] seg_data, //数码管要显示的数值 output reg[6:0] seg_out //数码管段选信号 ); always @(seg_data) begin case(seg_data) 4'b0001: seg_out= 7'b1111001; //数码管显示数字1 4'b0010: seg_out= 7'b0100100; //数码管显示数字2 4'b0011: seg_out= 7'b0110000; //数码管显示数字3 4'b0100: seg_out= 7'b0011001; //数码管显示数字4 4'b0101: seg_out= 7'b0010010; //数码管显示数字5 4'b0110: seg_out= 7'b0000010; //数码管显示数字6 4'b0111: seg_out= 7'b1111000; //数码管显示数字7 4'b1000: seg_out= 7'b0000000; //数码管显示数字8 4'b1001: seg_out= 7'b0011000; //数码管显示数字9 4'b0000: seg_out= 7'b1000000; //数码管显示数字0 endcase end endmodule

友晶科技FPGA开发板实现贪吃蛇游戏(九)——蛇身控制 DE10-STANDARD、DE1-SOC、DE2-115 - Doreen的FPGA自留地 - 博客园 (cnblogs.com)

友晶科技FPGA开发板实现贪吃蛇游戏(八)——游戏控制之状态机设计 DE10-STANDARD、DE1-SOC、DE2-115 - Doreen的FPGA自留地 - 博客园 (cnblogs.com)

友晶科技FPGA开发板实现贪吃蛇游戏(七)食物(苹果)的产生 DE10-STANDARD、DE1-SOC、DE2-115 - Doreen的FPGA自留地 - 博客园 (cnblogs.com)

友晶科技FPGA开发板实现贪吃蛇游戏(六)VGA 驱动模块色块显示 DE10-STANDARD、DE1-SOC、DE2-115 - Doreen的FPGA自留地 - 博客园 (cnblogs.com)

友晶科技FPGA开发板实现贪吃蛇游戏(五)VGA 驱动模块字符显示 DE10-STANDARD、DE1-SOC、DE2-115 - Doreen的FPGA自留地 - 博客园 (cnblogs.com)

友晶科技FPGA开发板实现贪吃蛇游戏(四)VGA 驱动模块图片显示 DE10-STANDARD、DE1-SOC、DE2-115 - Doreen的FPGA自留地 - 博客园 (cnblogs.com)

友晶科技FPGA开发板实现贪吃蛇游戏(三)记分模块 DE10-STANDARD、DE1-SOC、DE2-115 - Doreen的FPGA自留地 - 博客园 (cnblogs.com)

友晶科技FPGA开发板实现贪吃蛇游戏(二)数码管驱动模块 DE10-STANDARD、DE1-SOC、DE2-115 - Doreen的FPGA自留地 - 博客园 (cnblogs.com)

友晶科技FPGA开发板实现贪吃蛇游戏(一)——整体描述 DE10-Standard、DE1-SOC、DE2-115 - Doreen的FPGA自留地 - 博客园 (cnblogs.com)

浙公网安备 33010602011771号

浙公网安备 33010602011771号