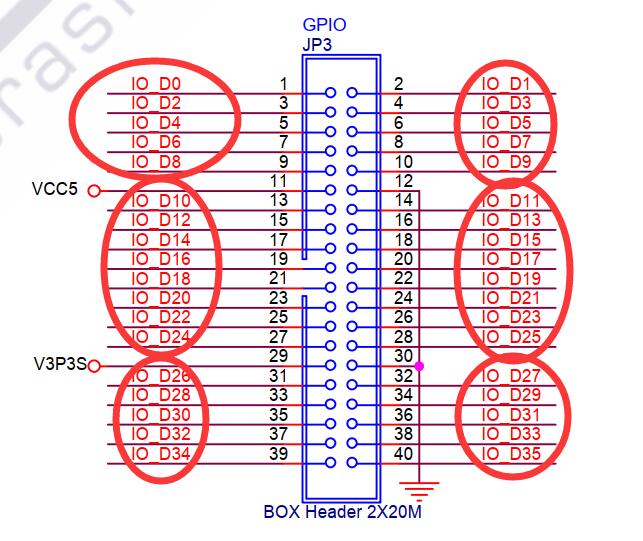

DE2i-150开发板共有120个用户可用的管脚,包括GPIO接口的36个I/O管脚(40 pins 除去VCC和 GND 的pin),HSMC接口的84个管脚(79个I/O管脚和5个专用Clock管脚,这79个I/O管脚其中也包括了HSMC_I2C_SCL和HSMC_I2C_SDA两个IO )。

DE2i-150开发板的HSMC接口可以配置当做GPIO接口用产生标准TTL电平信号,但要注意HSMC接口的I/O Standard是2.5V,而GPIO接口的I/O Standard是3.3V。

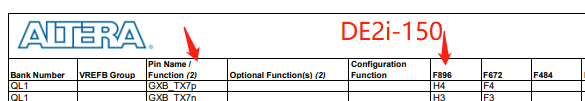

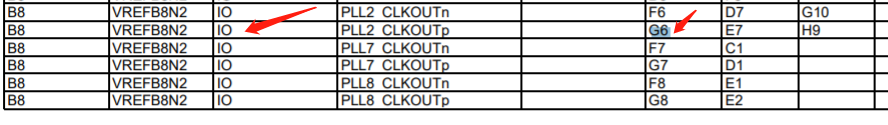

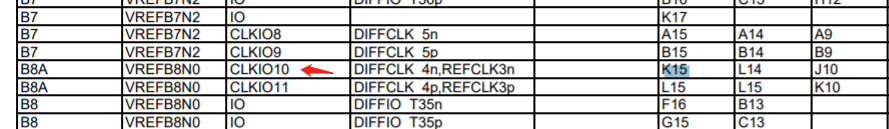

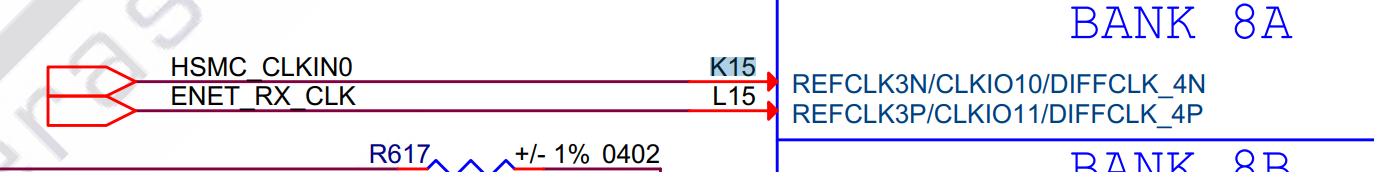

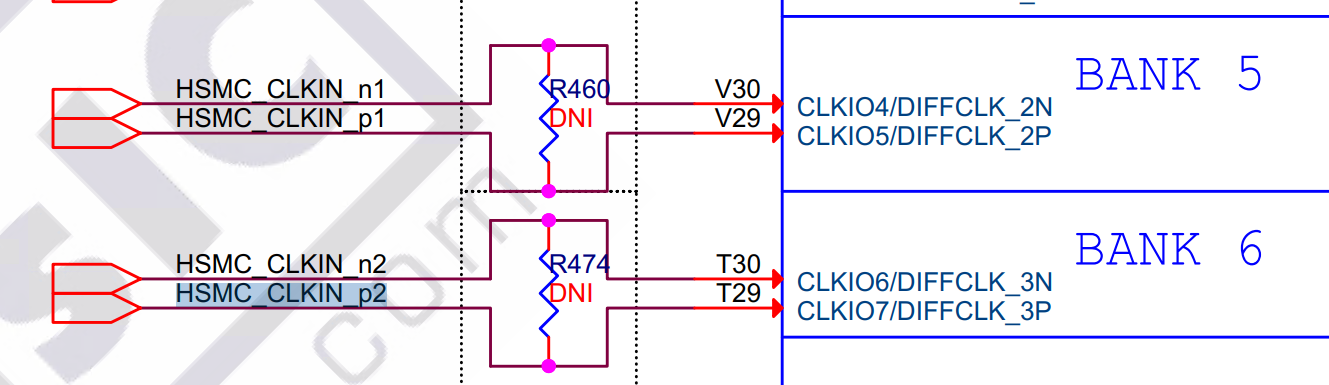

根据Cyclone IV 的引脚连接表(https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/dp/cyclone-iv/pcg-01008.pdf)的描述可知,HSMC接口的5个Clock pin只能是I 或者O , 而EP4CGX150DF31C7的G6 引脚可作为IO。

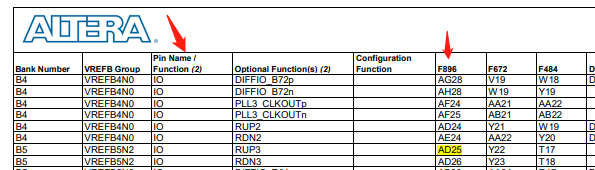

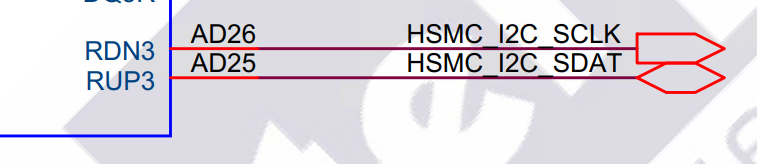

另外,从Cyclone IV 的引脚信息表(https://www.intel.cn/content/dam/www/programmable/us/en/pdfs/literature/dp/cyclone-iv/ep4cgx150.pdf)可知 HSMC_I2C_SCL和HSMC_I2C_SDA两个pin(引脚AD25和AD26 )是IO 引脚,可被用户当作IO 去使用:

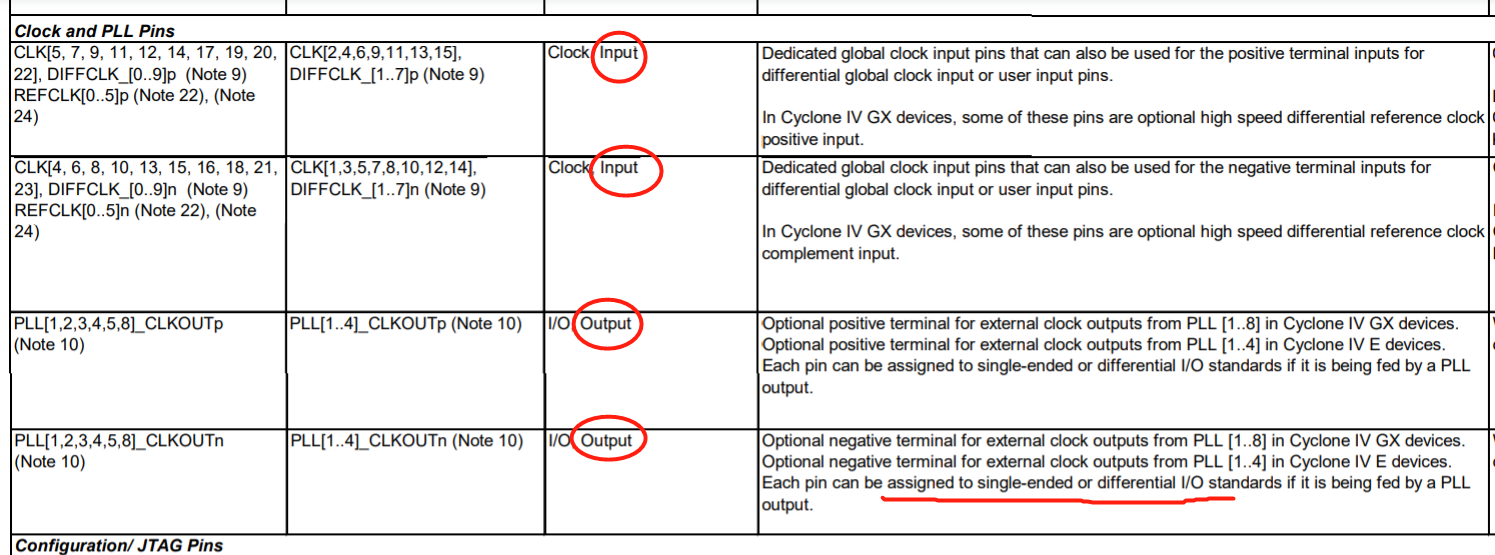

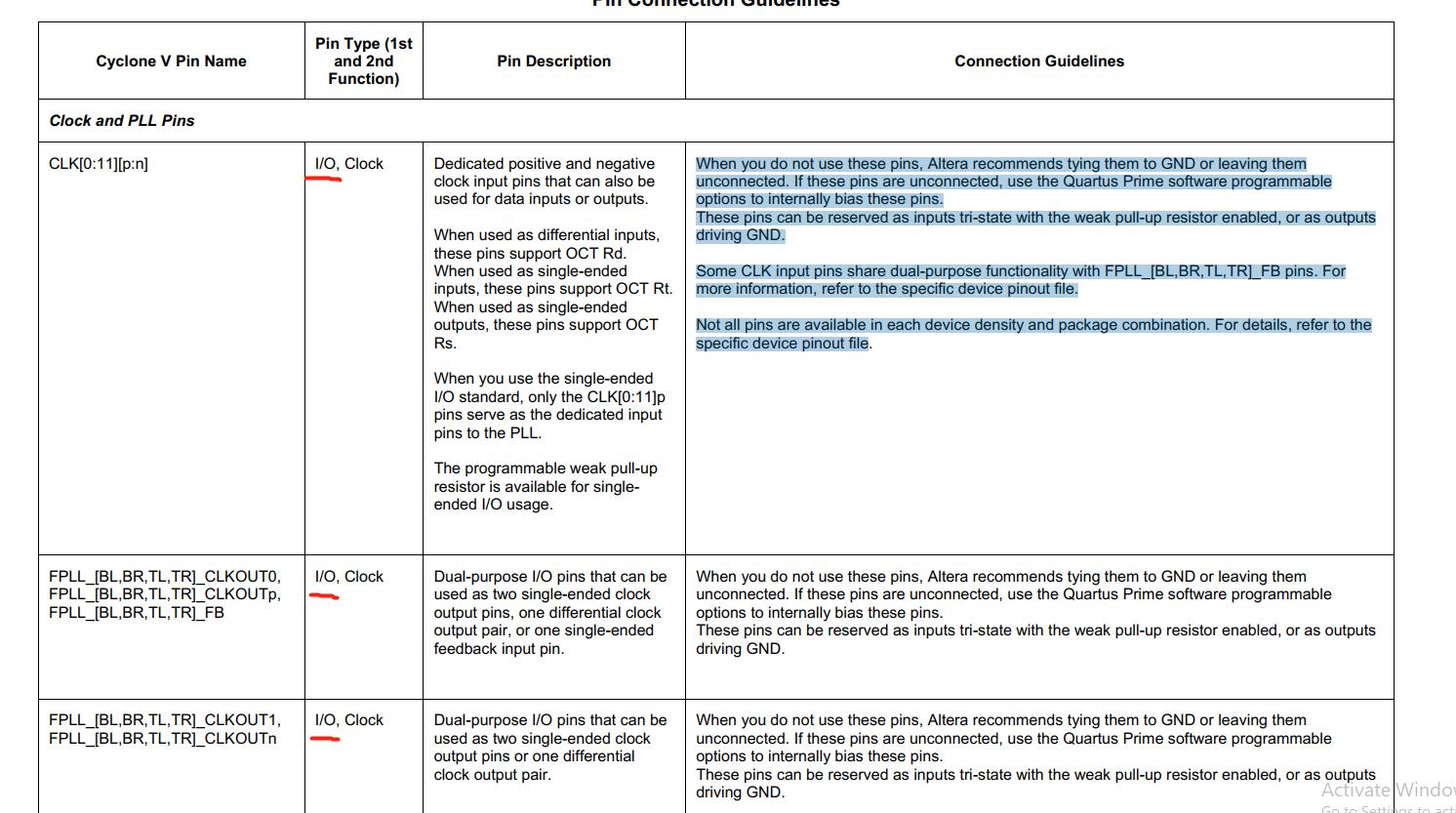

另外值得一提的是,Cyclone V 的clock pin 和Cyclone IV 的时钟有所不同,可以是I 也可配成O ,可作为普通IO 去用, 具体也是参考Cyclone V 的引脚连接表(目前Intel官网好像找不到Cyclone V 的引脚连接表了, 大家可以去参考友晶科技DE10-Nano开发板的资料包 DE10-Nano_v.1.3.2_HWrevC_SystemCD\Datasheet\FPGA\pcg-01014.pdf) :

浙公网安备 33010602011771号

浙公网安备 33010602011771号