寄存器的设计

基本寄存器的设计

基本介绍:

寄存器(Register)的功能是存储二进制代码,它是由具有存储功能的触发器组合起来构成的。一个触发器可以存储1位二进制代码,故存放n位二进制代码的寄存器,需用n个触发器来构成。

基本寄存器(Basic Register)的结构简单,只能并行送入数据,也只能并行输出

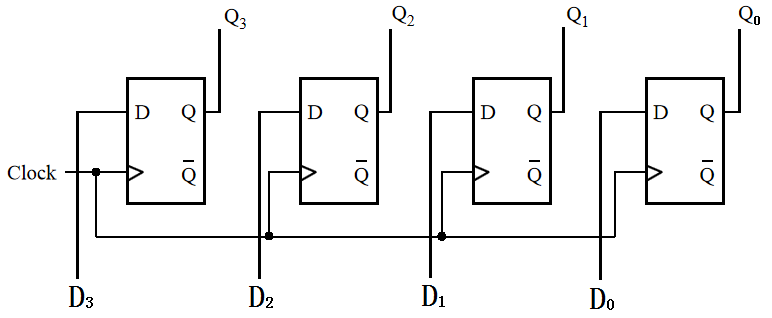

原理图长这样:

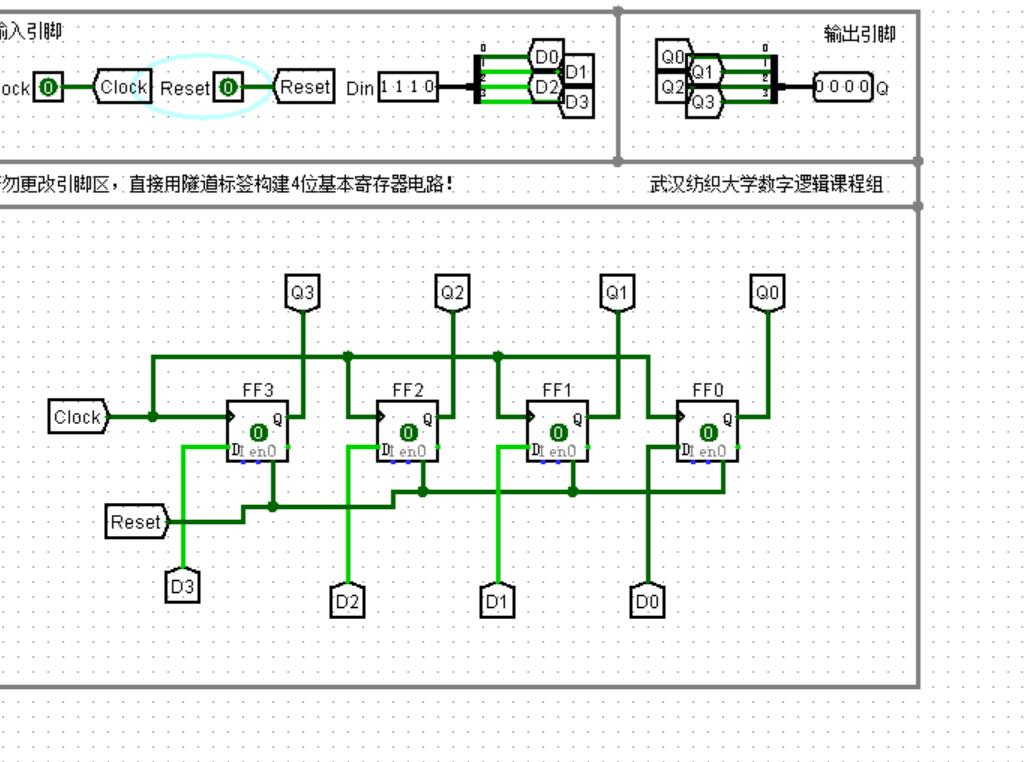

我手动绘制电路图长这样,当然我一开始把复位reset(异步复位端:Reset=1时复位,Q=0)接错了,导致复位就是Q1 , Q2,Q3,Q4 都是1111,后面查了一下才知道是接错了

移位寄存器的设计

简要介绍:数据可以在移位脉冲作用下依次逐位右移或左移

其实这个很简单,就是数据一个个传过去,比如现在是我点进输入1000,他会在下一个脉冲时刻输出1100,,再下一个就是1110,再下一个就是1111。

当然请注意,这里的输入并不是接在一起的,而是上一位的输出接下一位的输入

我自己手搓的图长这样:

循环移位寄存器的设计

其实原理很简单,都听说过队列吧,其实这种原理类似于循环队列,假设玩一个游戏,你的排队顺序是不是从你当前在的位置逐渐向前,然后到了首位玩完游戏之后再回来继续重新排队。

于是跟上面类似,就是用前一个的输出当作你下一个的输入,当然这里需要用多路选择器,因为这里给了你两个输入,一个正常输入引脚,另一个就是前一个输出,所以你需要用多路选择器给他俩一起连上

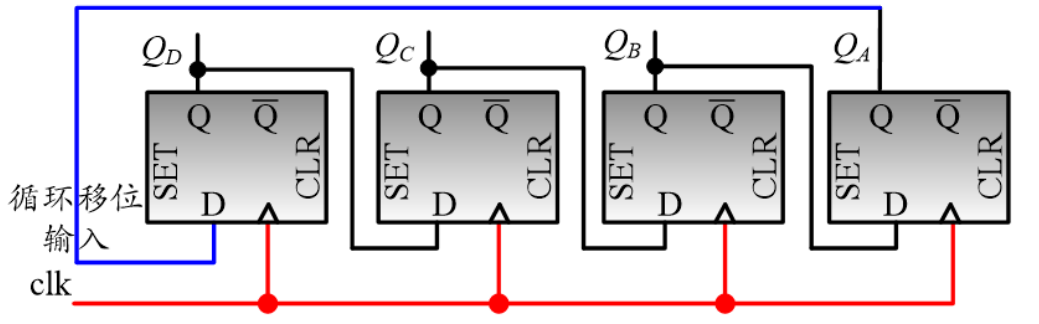

原理图如下:

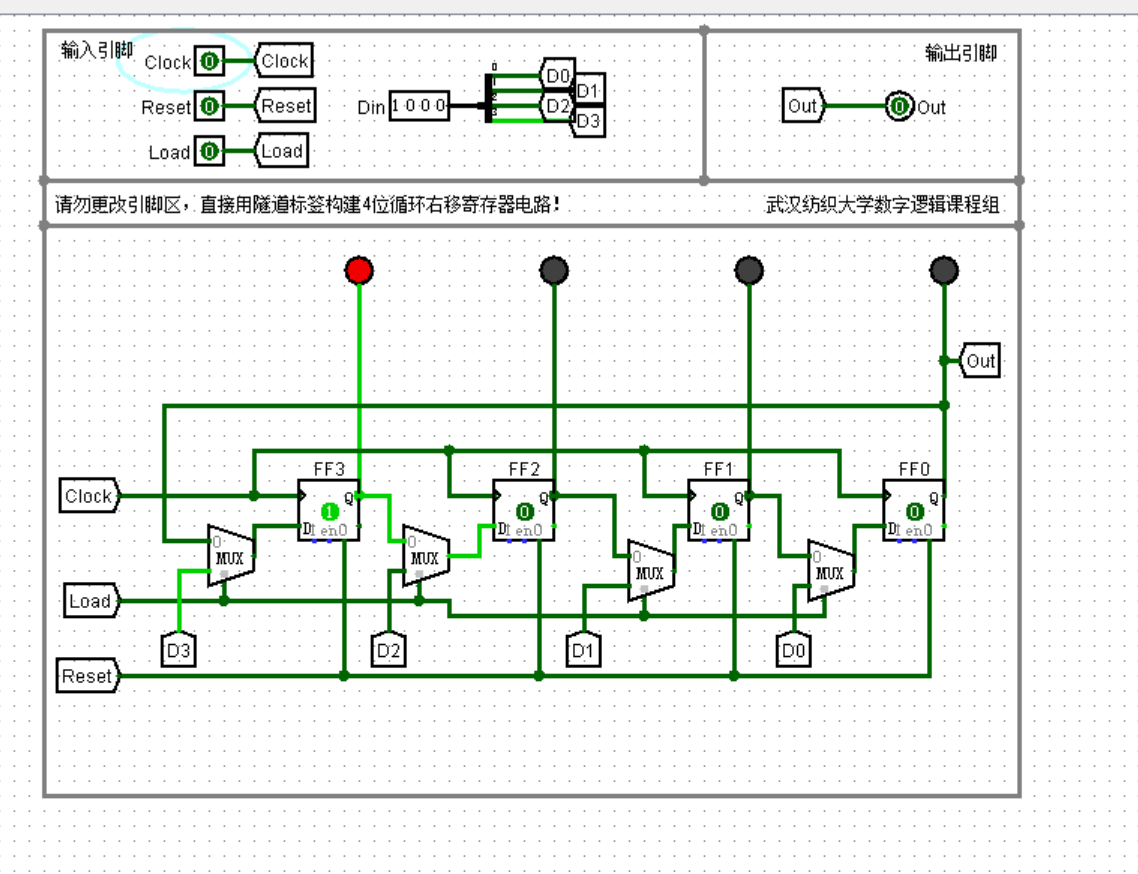

我自己手搓的图如下:

并行存取的移位寄存器的设计

首先让我们来了解一下什么叫并行存取,什么又叫串行存储?

并行存储是指将数据同时存储在多个存储单元中的一种存储方式

串行存储是指将数据逐个存储在多个存储单元中的一种存储方式

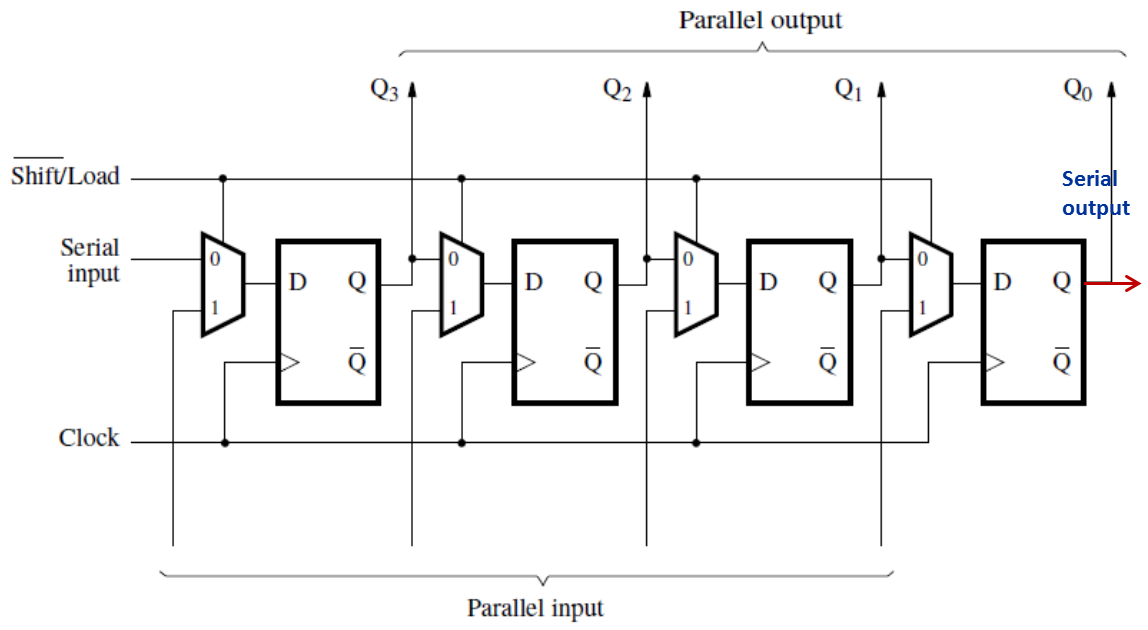

原理图长这样:

其中,~shift/load是选择信号,=1时并行数据同步加载控制,=0时串行数据右移输入控制

此时,触发器的D端有两个数据来源(串行输入和并行输入),用两路选择器即可

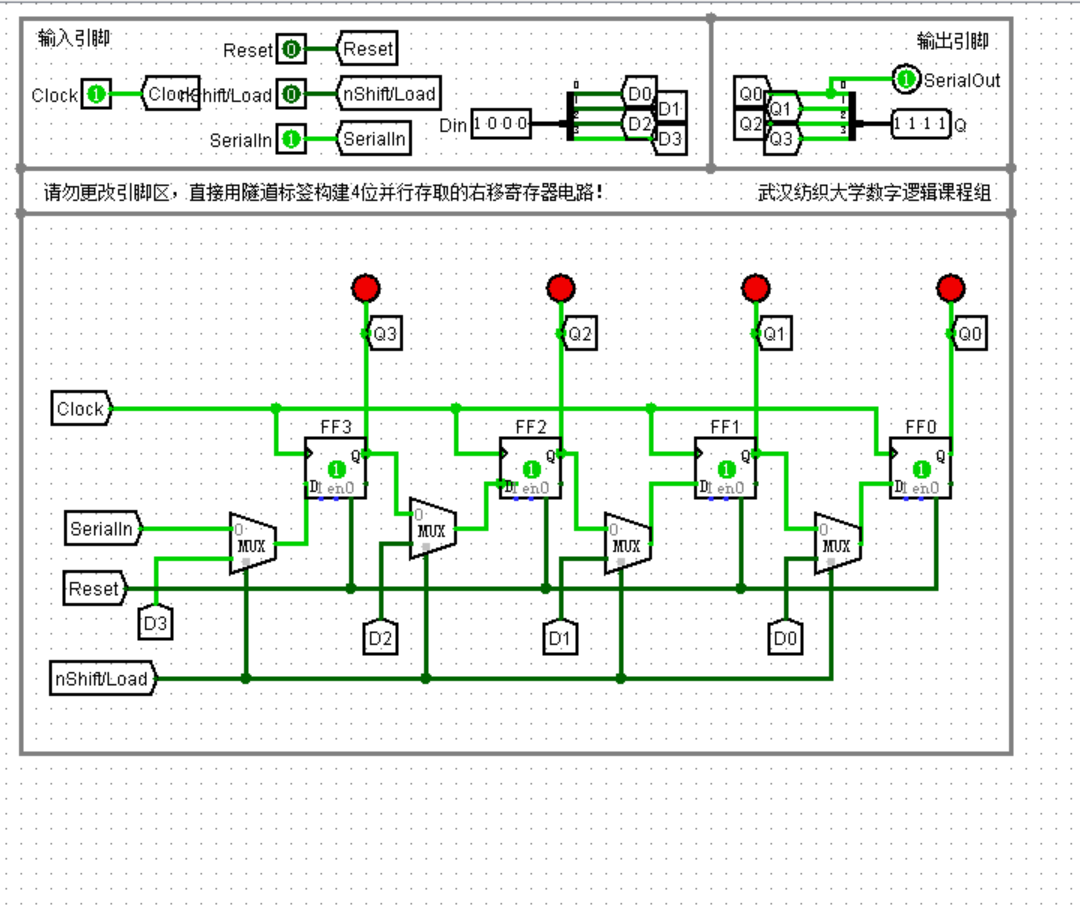

我看着原理图设计出来的电路图

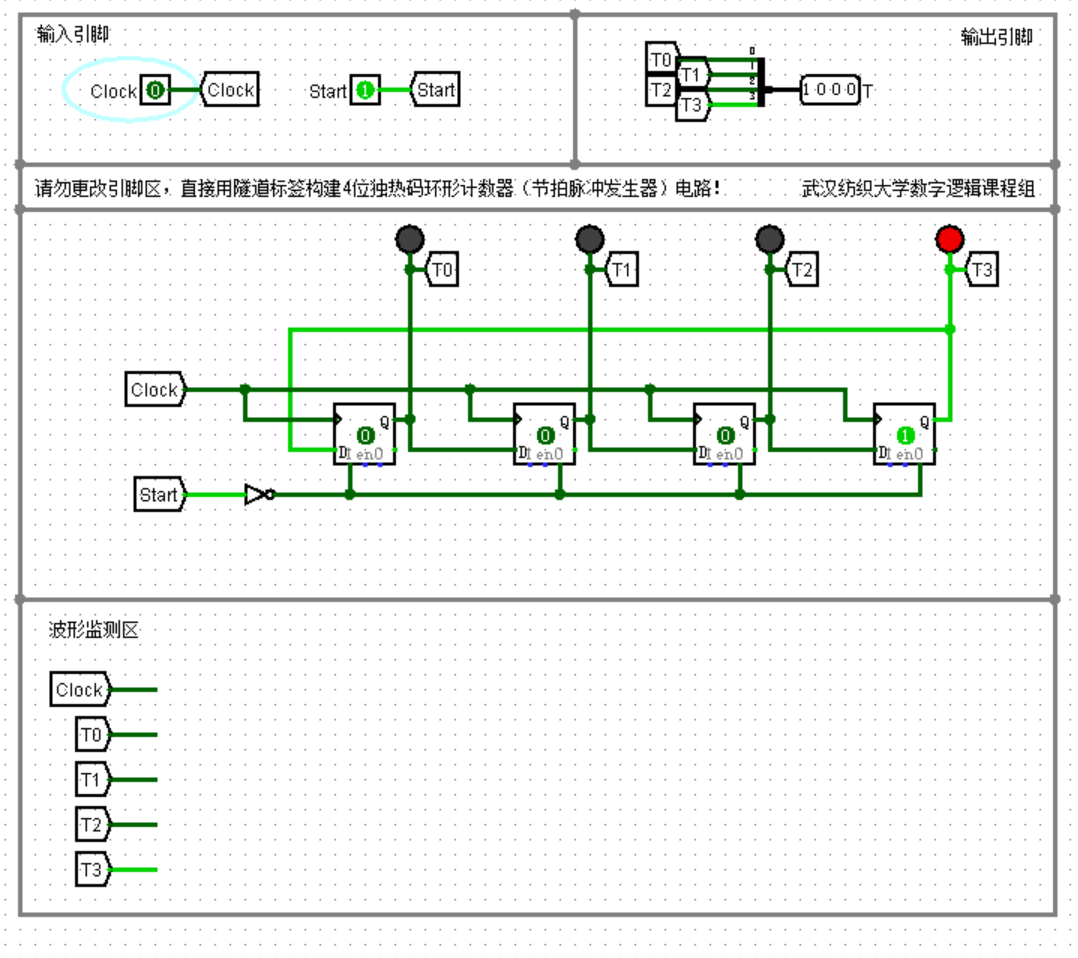

节拍脉冲发生器的设计

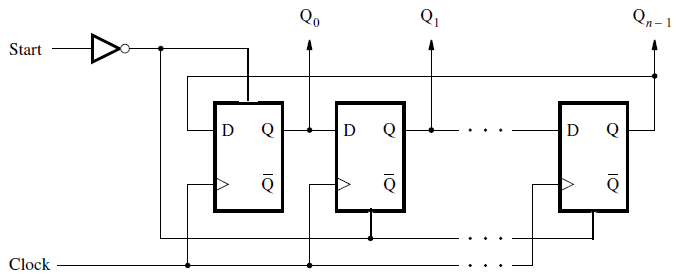

简要概述:节拍脉冲发生器又可称为独热码环形计数器,可以使用循环移位的原理实现,如下图所示。所谓独热码(one-hot code)直观来说就是有多少个状态就有多少比特,而且只有一个比特为1,其他全为0的一种码制。图中独热码T依次为1000、0100、0010、0001

原理图长这样:

其实就跟串行存储类似,每一位流水线存储数据

本文来自博客园,作者:Alaso_shuang,转载请注明原文链接:https://www.cnblogs.com/Alaso687/p/18983696

浙公网安备 33010602011771号

浙公网安备 33010602011771号