锁存器和触发器的设计

基本SR锁存器的设计

简单介绍:

锁存器(Latch)是一种对脉冲电平敏感的存储单元电路,它们可以在特定输入脉冲电平作用下改变状态。锁存,就是把信号暂存以维持某种电平状态。锁存器的最主要作用是缓存。

锁存器的结构特点是交叉耦合(反馈),这是形成记忆能力的关键。

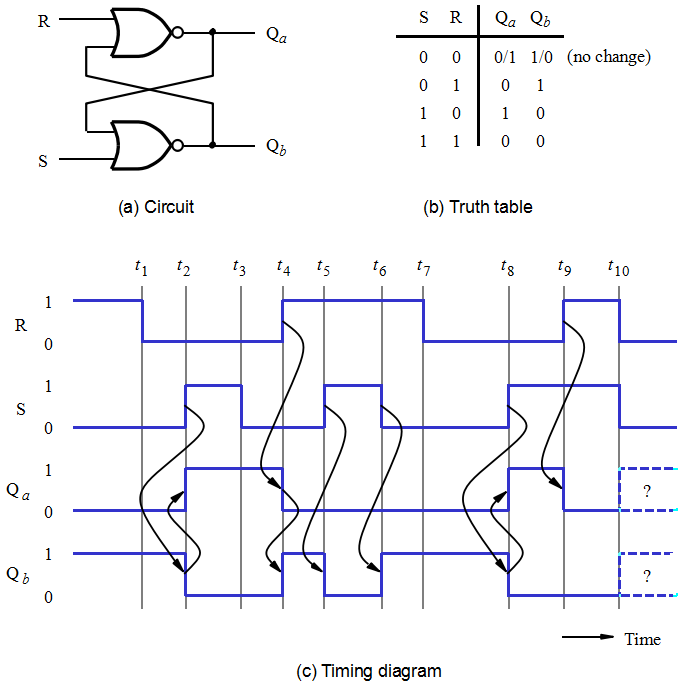

原理图长这样:

tips:功能口诀, 00保持、01置0、10置1、11不确定

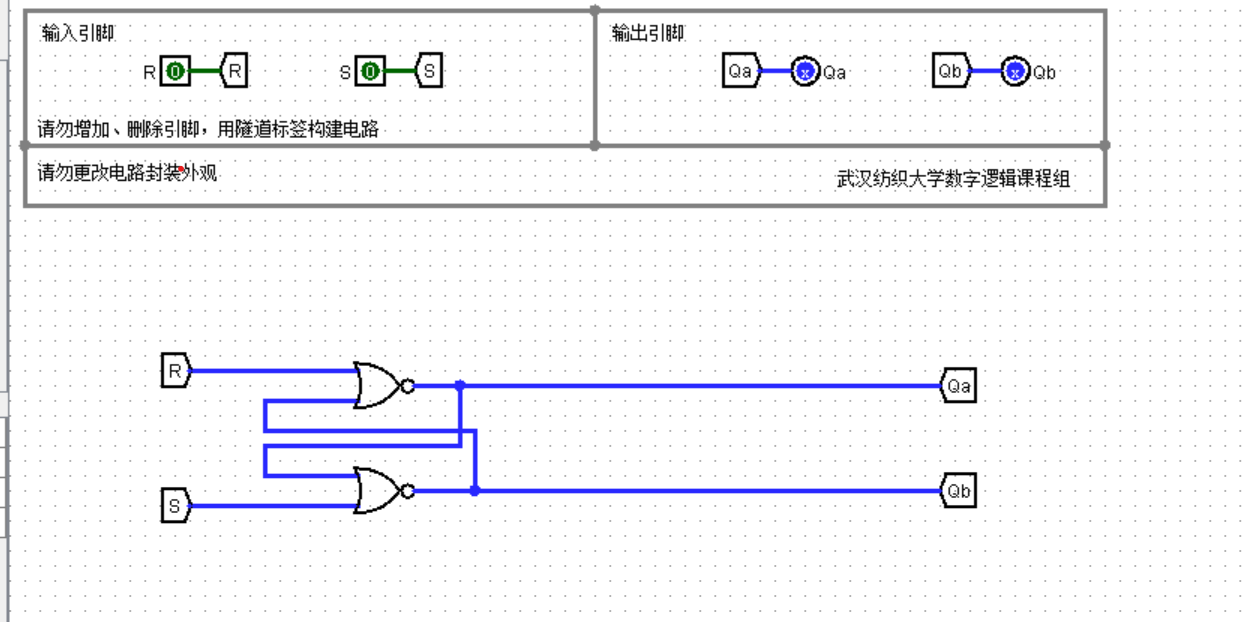

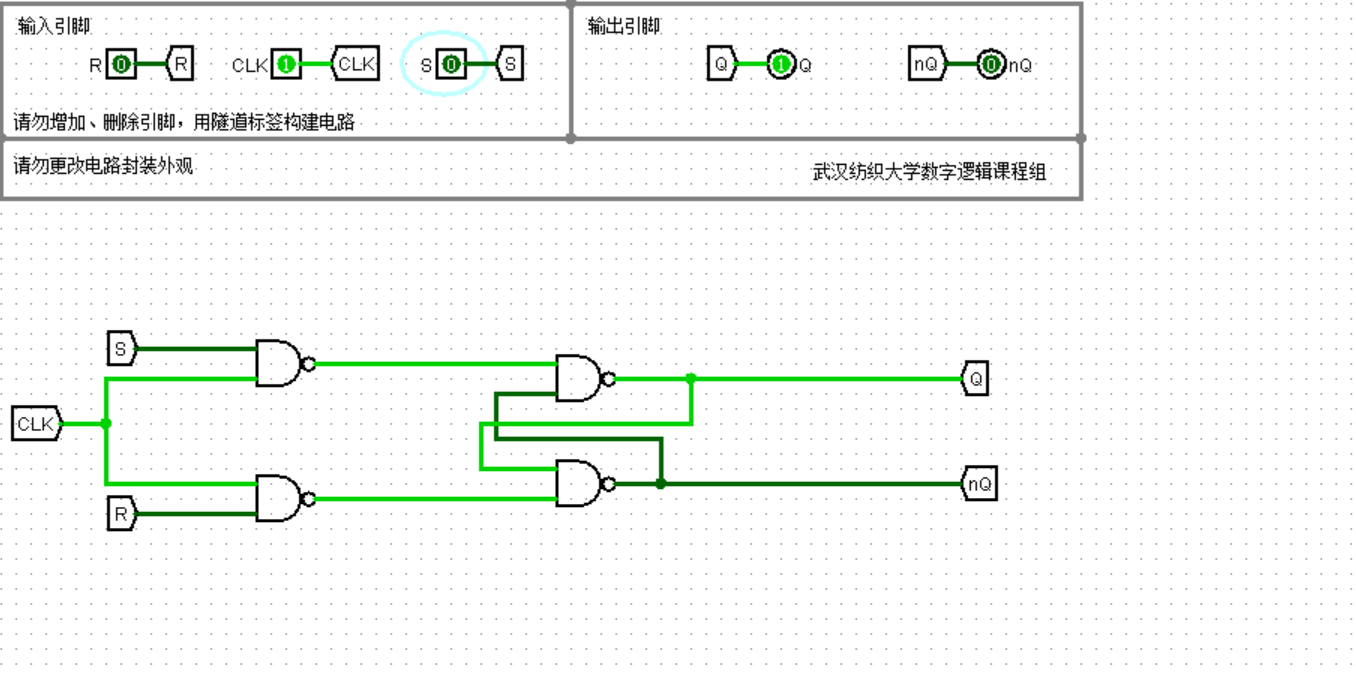

手搓内容如下:

当然这个方式其实你不知道内部有什么输出方式,可以说全靠后面有仪器测的话全靠猜,那有没有什么靠谱的办法能一开始就知道你输入进去的是什么呢?

有的,接下来让我们走进门控SR锁存器的设计

门控SR锁存器的设计

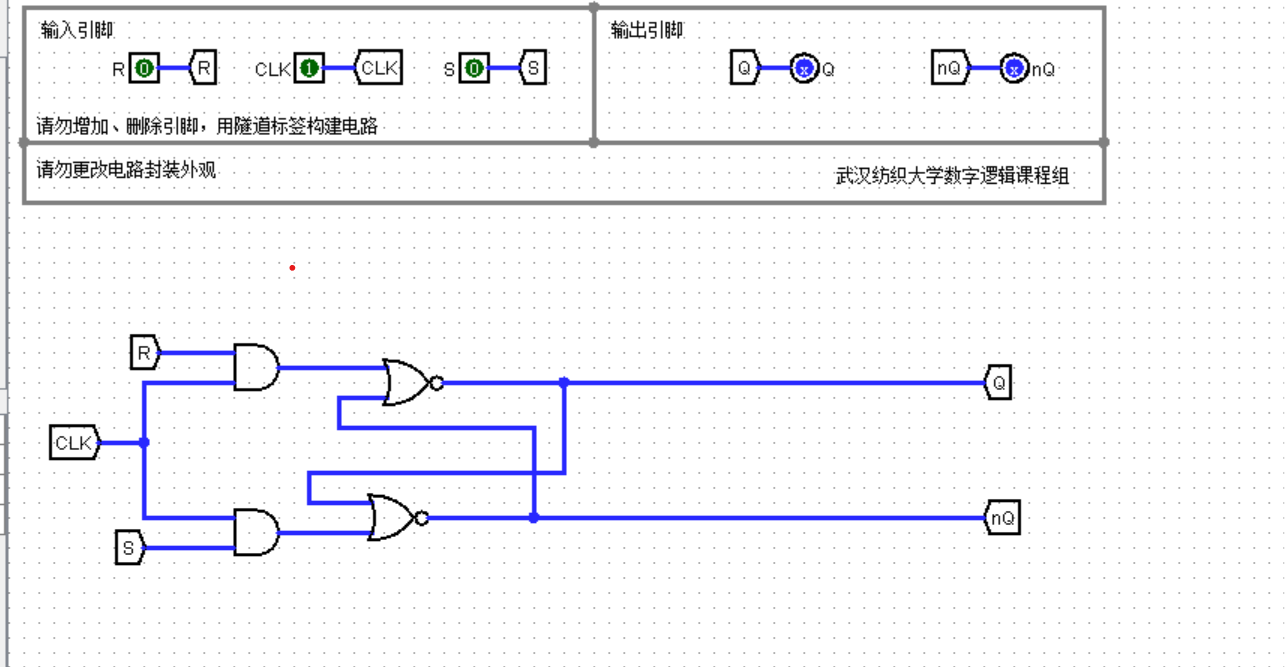

也就是加了个时钟,如果时钟为高电平,那么整个电路就可以改变电平状态

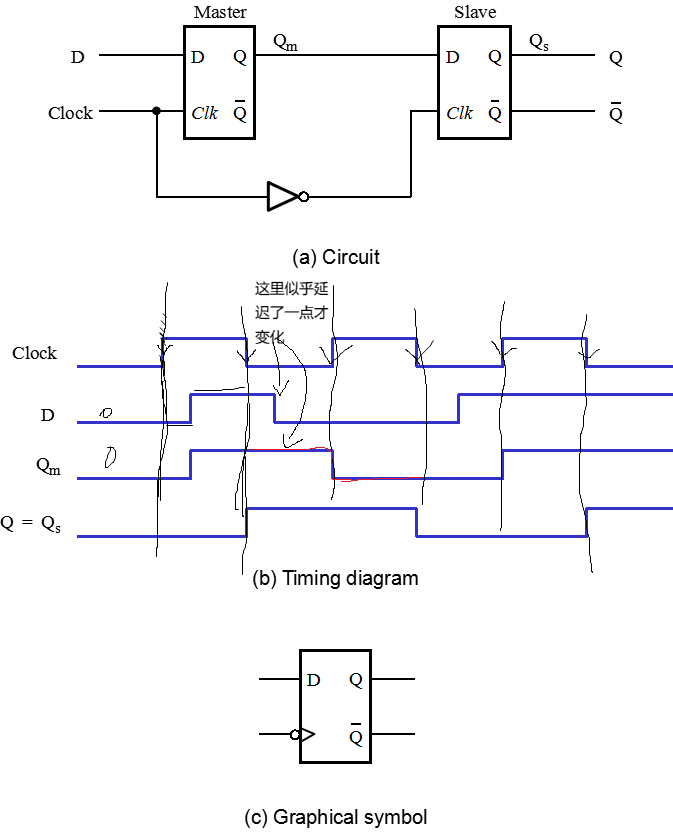

手搓电路图长这样

与非门构成的门控SR锁存器的设计

上述的SR锁存器全是或非门构建的,是否可以用与非门来建一个呢?

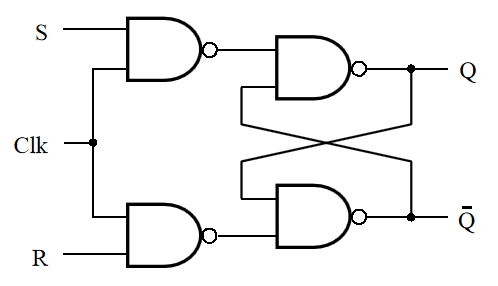

原理图长这样:

自己手搓:

门控D锁存器的设计

D锁存器其实跟SR锁存器的原理一样,但是只有一个输入端口,所以你在设计电路的时候通常要把另一个R端的端口取反

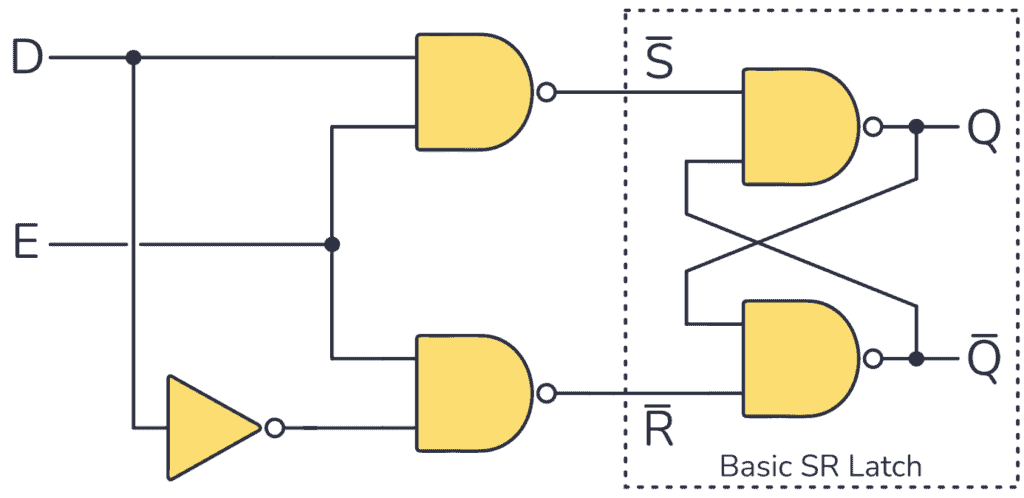

原理图长这样:

手搓电路图如下:

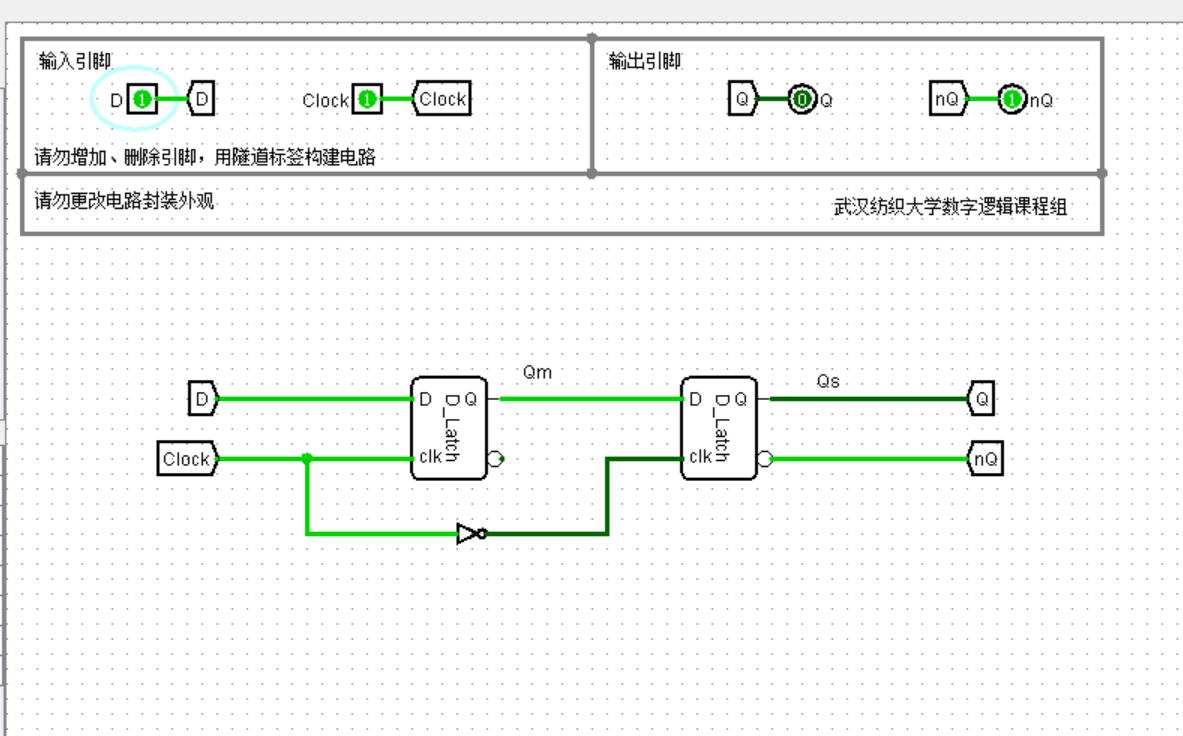

主从D触发器的设计

简介:在电平敏感型锁存器中,在时钟信号有效(如Clk=1)期间,锁存器的状态Q跟随输入的变化而变化,这种现象称为“空翻”。为了避免出现空翻,可以把状态变化时机限定在时钟信号的上升沿或者下降沿,这种类型的器件称为触发器(Trigger/Flipflop)

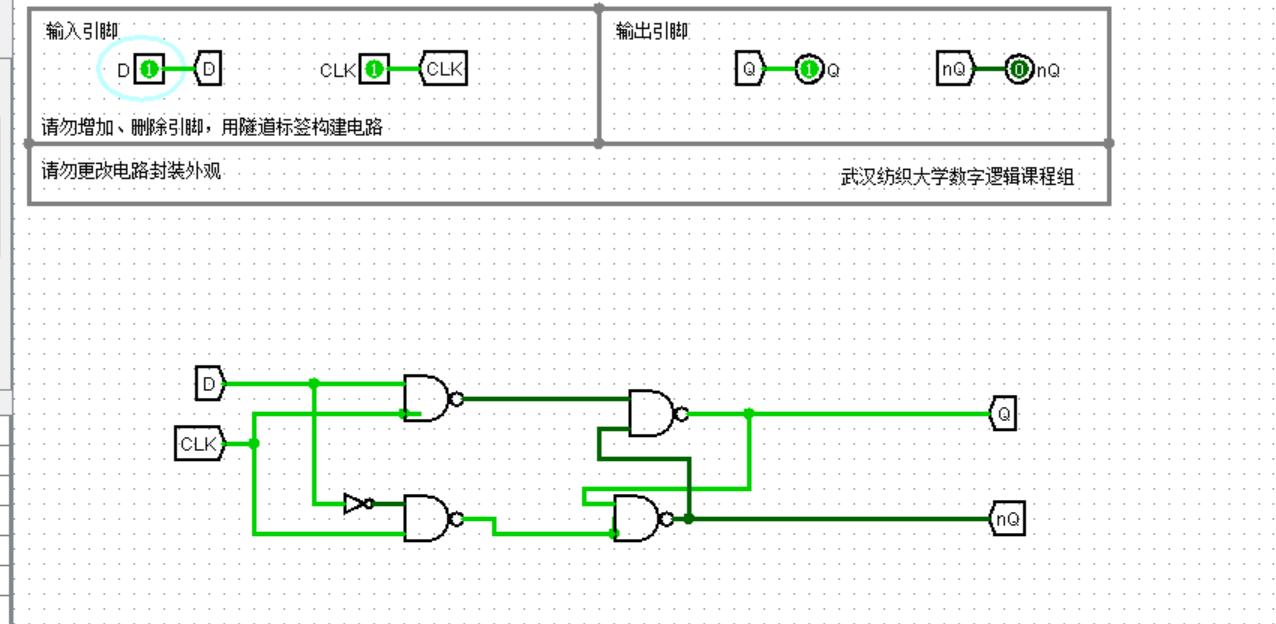

原理图长这样:

注意:时钟低电平时,只有主锁存器有效,Qm会随着D变化,但是输出Qs始终不变。当时钟高电平时,只有从锁存器有效,Qs会随着Qm变化,但是此时主锁存器处于保持状态,Qm是不变的,所以Qs也保持不变。 只有在时钟上升/下降沿的时候,此时Qm还在跟随D的值,而Qs正要开始跟随Qm的值。 此时D的值可以通过Qm传递到输出Qs,D触发器输出改变。

手搓电路图长这样,为什么没有变化是因为我的时钟没有设置上升沿和下降沿!

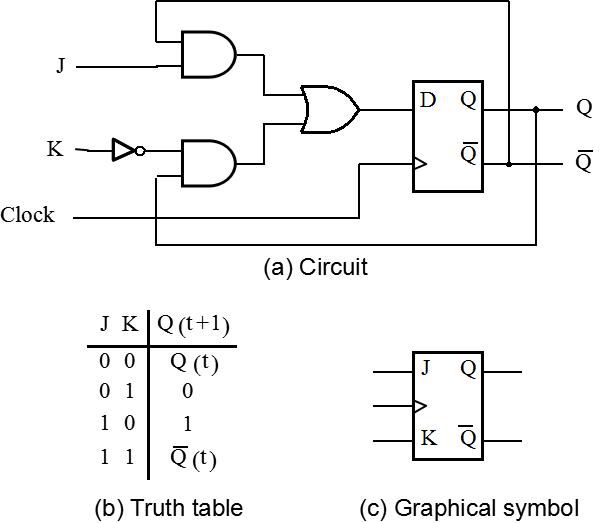

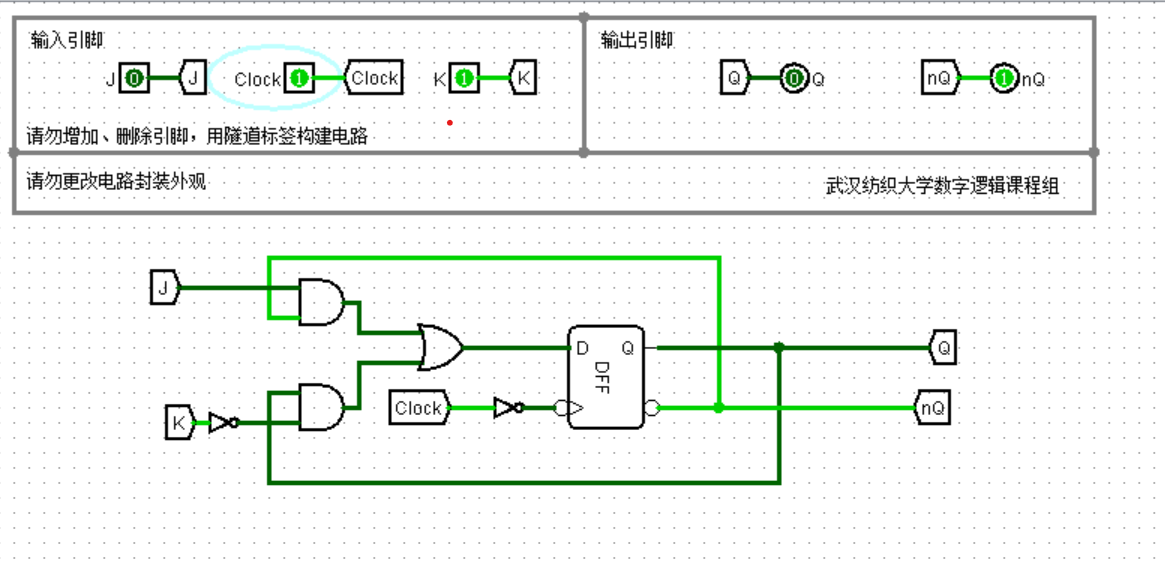

JK触发器的设计

也是基于D触发器上开发的一款触发器,有点像可控SR锁存器(主包只是感觉哈),但是当J = 1时,K = 1时,起到的作用是 翻转

原理图长这样:

特征方程是:Qn+1 = J & ~ Qn + ~ K & Qn

手搓电路图如下,PS:一定要注意你的D触发器当时是沿时钟上升沿还是下降沿设计的 如果你的JK触发器要求上升沿,但是你的D触发器又是下降沿的话就给时钟信号取个反即可!

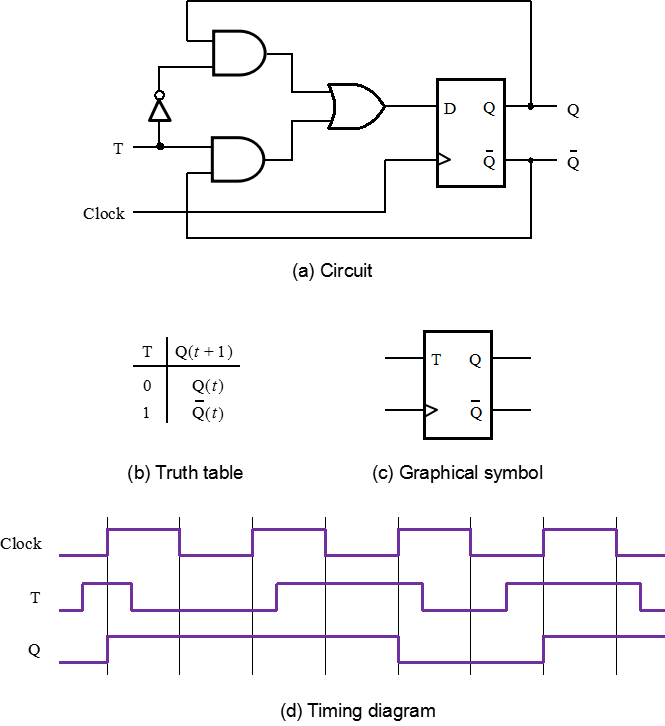

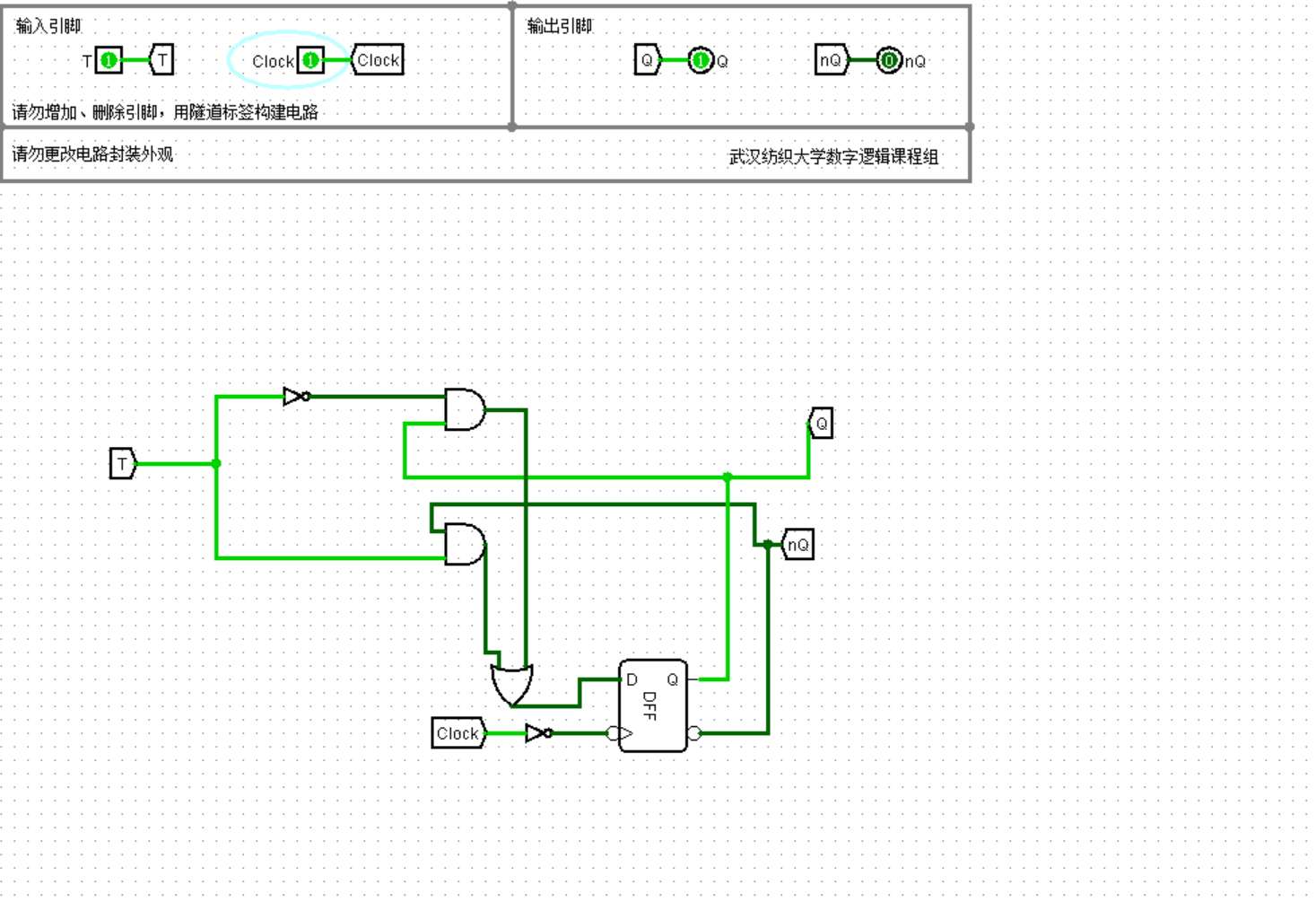

T触发器的设计

哈哈,也是基于D触发器搭建的,他的表达式是 Qn+1 = T & ~ Qn + ~T & Qn = T ^ Qn

原理图长这样:

我手搓的电路图,还是跟上面的解释一样,一定要注意你的D触发器当时是沿时钟上升沿还是下降沿设计的,我上次设计的D触发器是时钟下降沿的,所以时钟照旧得取反!

本文来自博客园,作者:Alaso_shuang,转载请注明原文链接:https://www.cnblogs.com/Alaso687/p/18982292

浙公网安备 33010602011771号

浙公网安备 33010602011771号