SPI通信协议接口概述

一、 spi的概述

SPI是串行外设接口(Serial Peripheral Interface)的缩写,是一种高速的,全双工,同步的通信总线,它是由Motorola公司推出,用来在微控制器和外围设备芯片之间实现数据交换的低成本、易使用的接口。SPI总线为同步串行数据传输总线,用于单片机的外围拓展。spi利用时钟线对数据位进行同步,时钟的上升沿或下降沿锁存数据,来自主机或从机的数据在时钟上升沿或下降沿同步,主机和从机可以同时传输数据。

二、 spi的配置

spi可以是三线式的也可以是四线式的

1、三线制半双工SPI可以分时收发

SCLK串行时钟

CS或SS外设片选或从机选择

DIO数据线,输入与输出共用

2、四线制全双工SPI可同时收发

MISO主机输入/从机输出

MOSI主机输出/从机输入

SCLK串行时钟

CS/SS外设片选或从机选择

来自主机的片选信号CS是从芯片是否被主芯片选中的控制信号,这通常式一个低电平有效,拉高时从机与SPI总线断开连接,当使用多个从机时,主机需要为每个从机提供单独的片选信号,产生时钟信号的器件称为主机

三、 spi的数据传输

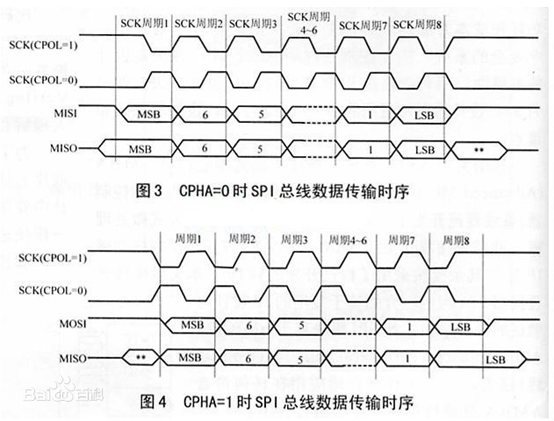

通讯是通过数据交换完成的,这里先要知道SPI是串行通讯协议,也就是说数据是一位一位的传输的。这就是SCLK时钟线存在的原因,由SCLK提供时钟脉冲,SDI,SDO则基于此脉冲完成数据传输。数据输出通过 SDO线,数据在时钟上升沿或下降沿时改变,在紧接着的下降沿或上升沿被读取。完成一位数据传输,输入也使用同样原理。因此,至少需要8次时钟信号的改变(上沿和下沿为一次),才能完成8位数据的传输。(源自百度百科)

四、 时钟极性和时钟相位

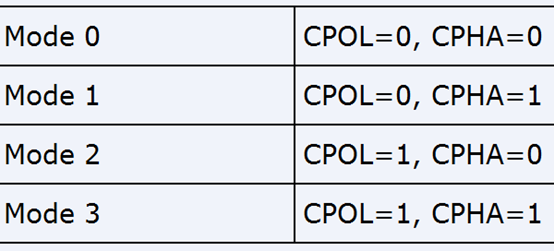

在spi的概述中我们讲spi利用时钟线对数据位进行同步,时钟的上升沿或下降沿锁存数据,那么主机就需要根据从机的要求去选择时钟极性和时钟相位。根据CPOL和CPHA位的选择,有四种SPI模式可用。

CKPOL (Clock Polarity) (时钟)极性:SPI空闲时的时钟信号电平(1高电平,0低电平)

CKPHA (Clock Phase) (时钟)相位:SPI在时钟的第几个边沿采样(1第二个边沿开始,0第一个边沿开始)

参考:SPI(SPI协议)_百度百科 (baidu.com)

浙公网安备 33010602011771号

浙公网安备 33010602011771号