数字IC设计中用到的EDA工具

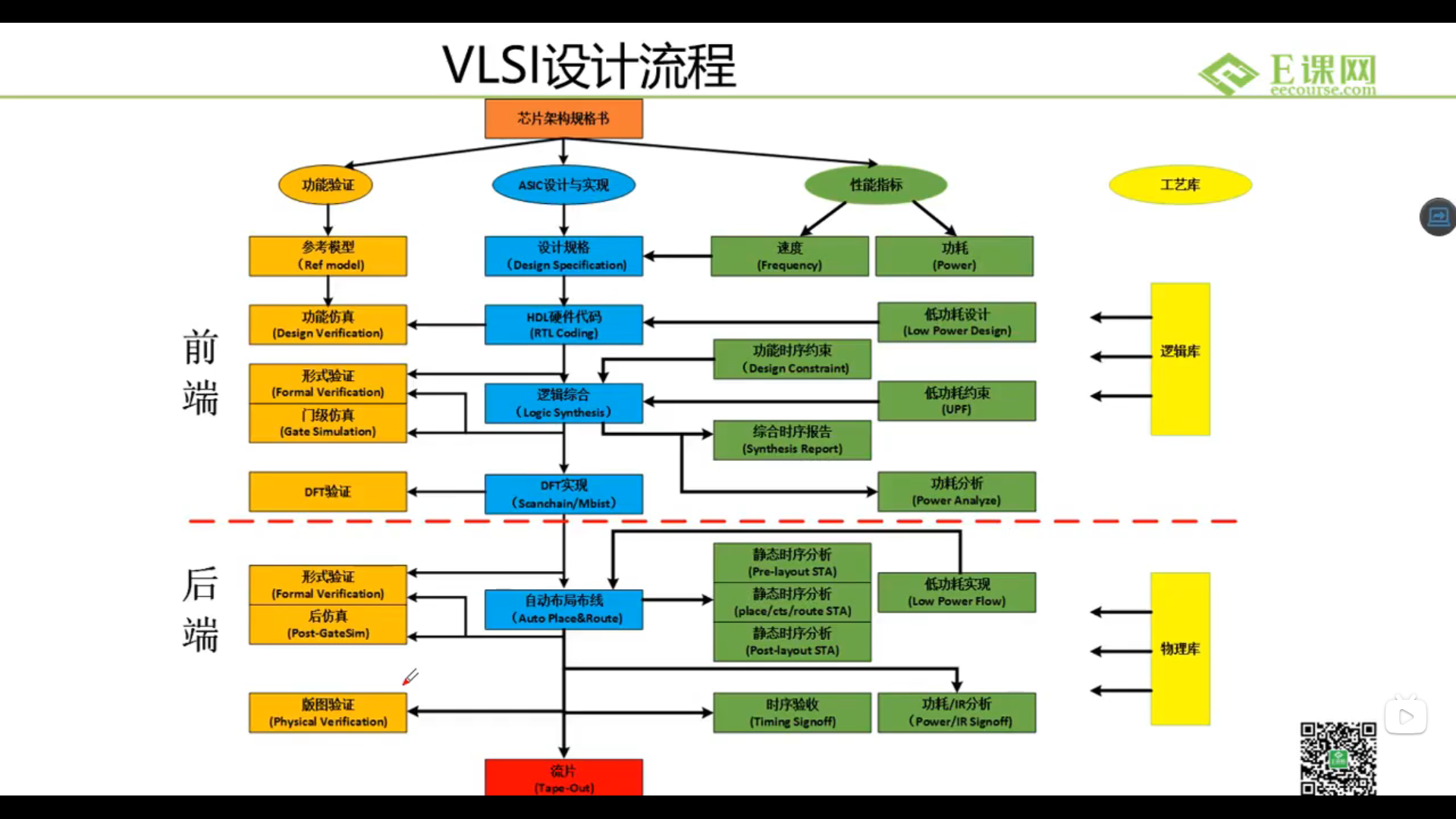

仿真验证工具:Cadence的Incisive、Synopsys的VCS、Mentor的QuestaSim

逻辑综合工具:Cadence的Gneus、Synopsys的Design Compiler(DC)

形式验证工具:Cadence的Conformal、Synopsys的Formality

静态时序分析工具:Cadence的Tempus、Synopsys的Prime Time(PT)

自动布局布线工具:Cadence的Innovus、Synopsys的IC Compiler(ICC)

物理验证工具:Mentor的Calibre、Synopsys的Hercules、Cadence的Diva/Dracula

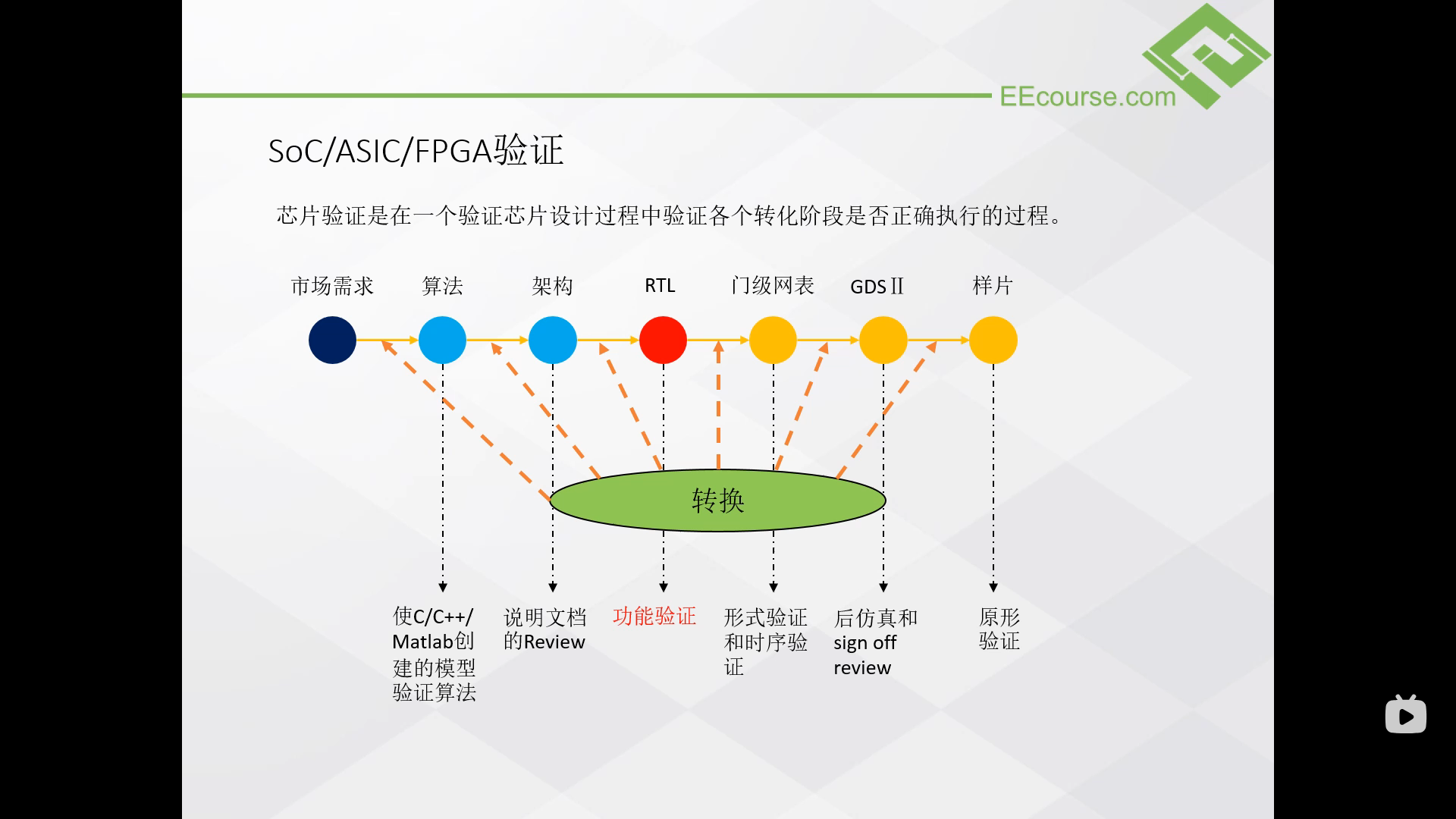

形式验证:从功能上(STA是时序上)对综合后的网表进行验证。常用的就是等价性检查(Equivalence Check)方法,以功能验证后的HDL设计为参考,对比综合后的网表功能,他们是否在功能上存在等价性。这样做是为了保证在逻辑综合过程中没有改变原先HDL描述的电路功能。

浙公网安备 33010602011771号

浙公网安备 33010602011771号