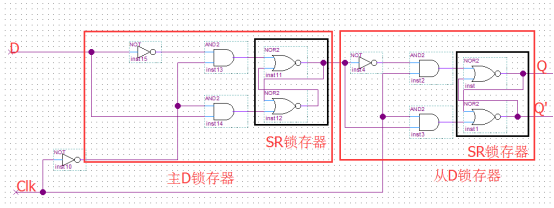

上升沿触发的D触发器电路结构图(一眼就能看懂)以及触发器为什么要有建立时间和保持时间要求

当clk为低电平时,主D锁存器的两个与门的~clk为高电平,与门打开,主D锁存器的输出随输入D变化,而从D锁存器的两个与门的clk为低电平,与门输出始终为0,从D锁存器的输出保持不变。

当clk为高电平时,与clk为低电平时情况刚好相反,主D锁存器保持不变,从D锁存器输出为主D锁存器输出值。

电路整体表现为在时钟上升沿Q输出D,其他时刻Q值保持不变。

触发器为什么要有建立时间和保持时间要求?

之所以有建立时间要求,就是要保证主D锁存器能够锁存住稳定的信号,因此时钟上升沿之前D输入信号要提前一段时间进入稳定。

之所以有保持时间要求,就是要保证主D锁存器锁存的信号不被D输入信号的变化而被破坏,因此时钟上升沿之后D输入信号要保持一段时间。

(注:上图中上升沿触发的D触发器电路结构并不唯一,也可用与非门+非门的电路结构实现,两种方式使用的基本门的数量是相同的。)

浙公网安备 33010602011771号

浙公网安备 33010602011771号