时钟配置流程

通常开发都是基于工程模板或者以前的项目增量开发,对于一些基础又会忘记,这里梳理一下时钟配置流程。

时钟配置相关文件

芯片STM32f407,基于标准库的时钟配置所涉及文件如下:

| 文件 | 说明 |

|---|---|

| startup_stm32f40_41xxx.s | 汇编启动文件:定义复位向量,在跳转到 C 语言main之前首先调用SystemInit。 |

| system_stm32f4xx.c | 系统初始化源文件:实现SystemInit()、SetSysClock()及 PLL 参数配置逻辑。 |

| stm32f4xx.h | 底层定义头文件:定义外部晶振频率HSE_VALUE、设备类型宏及寄存器映射。 |

| system_stm32f4xx.h | 系统初始化头文件:声明SystemCoreClock全局变量。 |

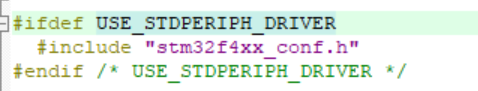

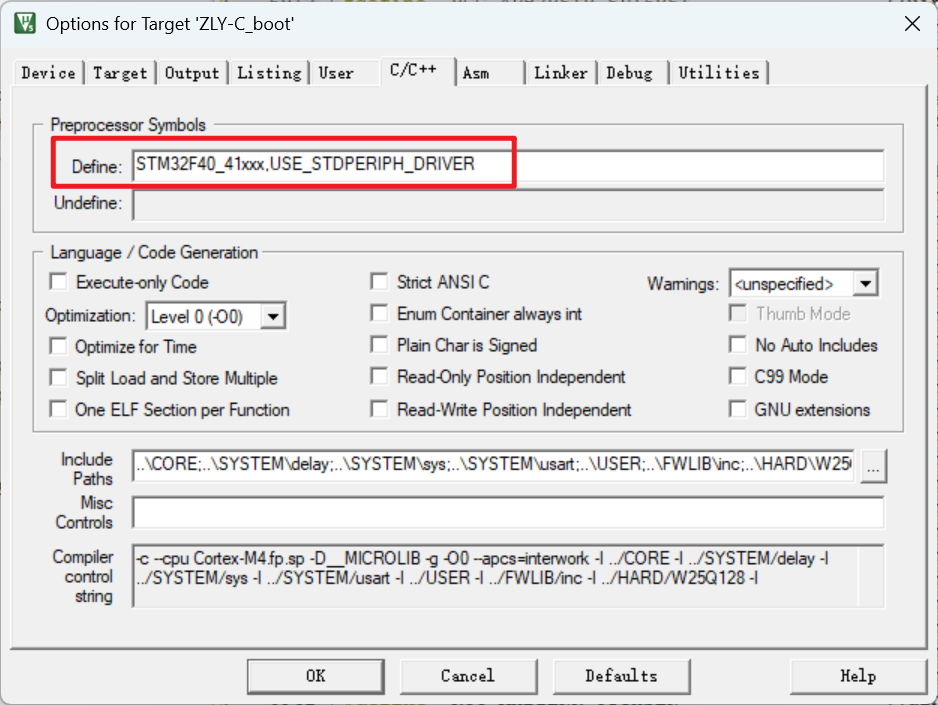

使用Keil5开发,使用宏定义选择型号芯片,影响system_stm32f4xx.c中的参数选择。

Project → Options → C/C++ → Define

这里型号为STM32F40_41xxx,即F407。这里还有要给宏USE_STDPERIPH_DRIVER,即告诉编译器,使用 STM32 标准外设库来操作外设寄存器。使用外设就要包含stm32f10x.h,由于宏定义,在stm32f10x.h中会include stm32f4xx_conf.h。stm32f4xx_conf.h 是用户配置文件,用于:启用/禁用各个外设驱动(如 #define USE_GPIO、#define USE_USART 等);配置系统时钟、中断等;包含必要的头文件。

时钟配置

参数

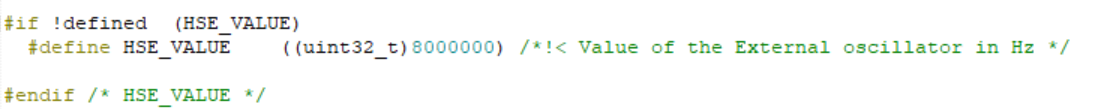

HSE_VALUE,使用外部高速晶振8MHz,其他格式,stm32f4xx.h中可进行配置

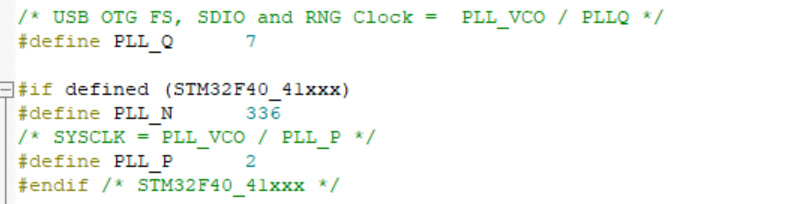

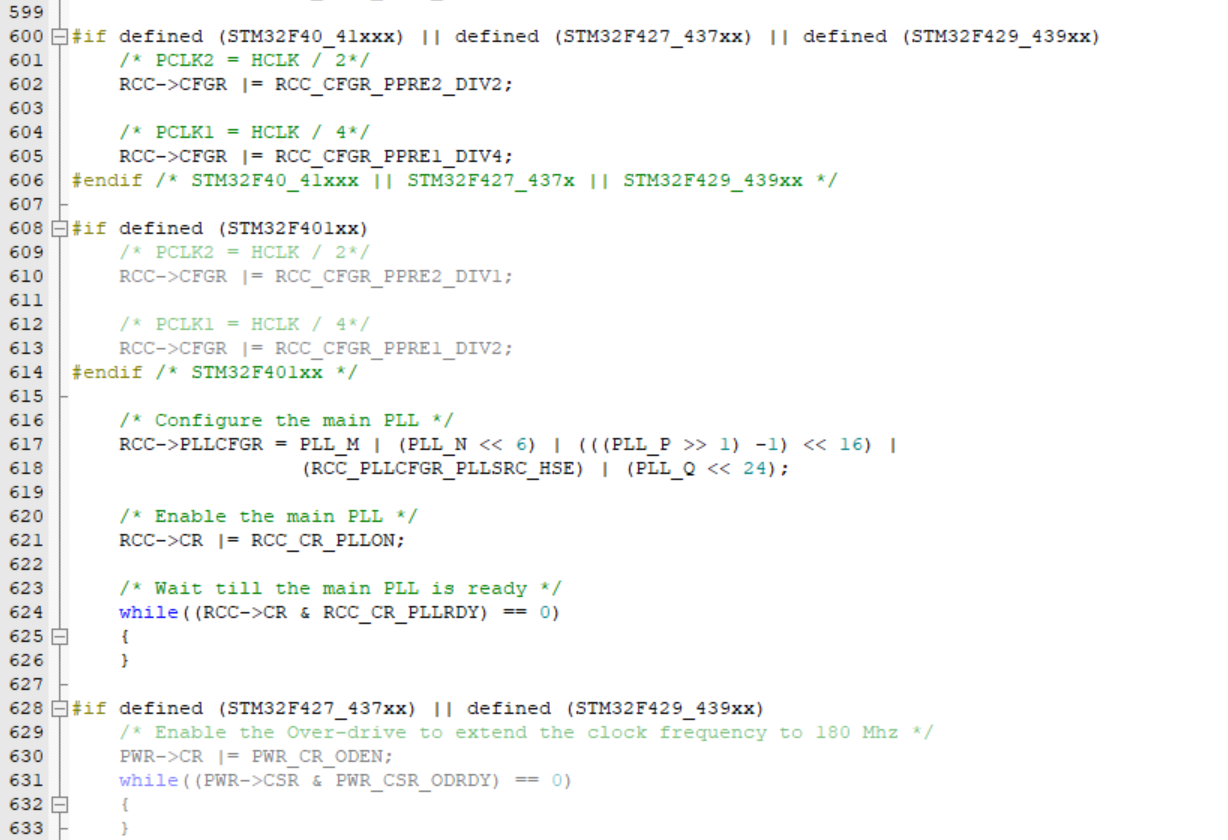

根据芯片型号宏定义,在system_stm32f4xx.c中可以看到,PLL_M分频系数为8,使VCO输入频率为1MHz,即8/1 = 1MHz

![]()

PLL_N倍频系数,使VCO输出频率达到336MHz,即8/1 * 336 = 336MHz

PLL_P系统时钟分频系数,即336/2 = 168MHz

PLL_Q usb/sdio/rng时钟分配系数,即336/7 = 48MHz

流程

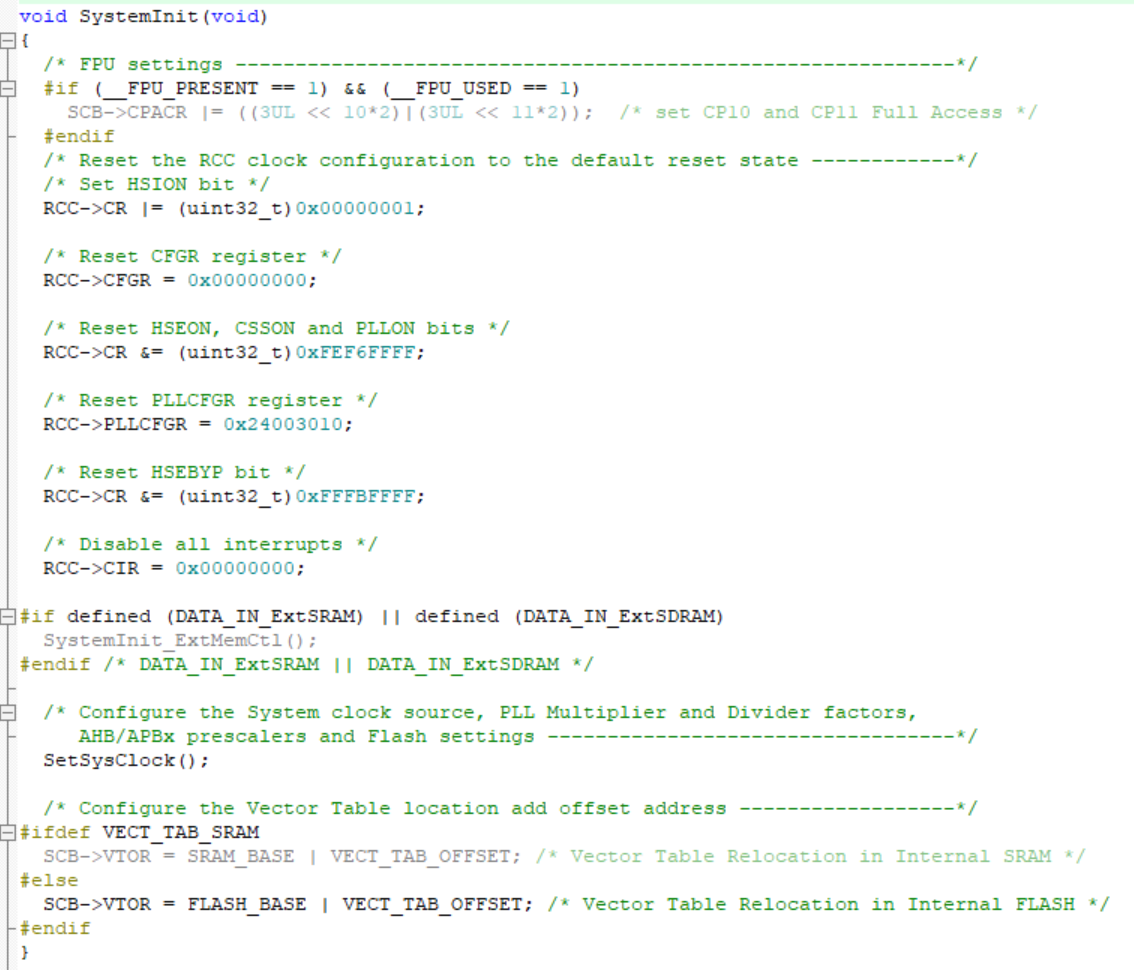

硬件复位后,执行 startup_stm32f40_41xxx.s 中的复位中断服务程序。其中SystemInit(): 位于 system_stm32f4xx.c,主要负责重置 RCC 寄存器到默认状态,并调用 SetSysClock()。SetSysClock(): 位于 system_stm32f4xx.c,静态函数,执行具体的硬件主频倍频操作。

; Reset handler

Reset_Handler PROC

EXPORT Reset_Handler [WEAK]

IMPORT SystemInit

IMPORT __main

LDR R0, =SystemInit

BLX R0

LDR R0, =__main

BX R0

ENDPSystemInit()中完成,使能内部高速晶振HSI,复位CFGR清除所有时钟源配置,关闭HSE,CSS,PLL,复位PLL配置寄存器默认值,关闭HSE旁路模式,禁用所有RCC,接着进入SetSysClock();

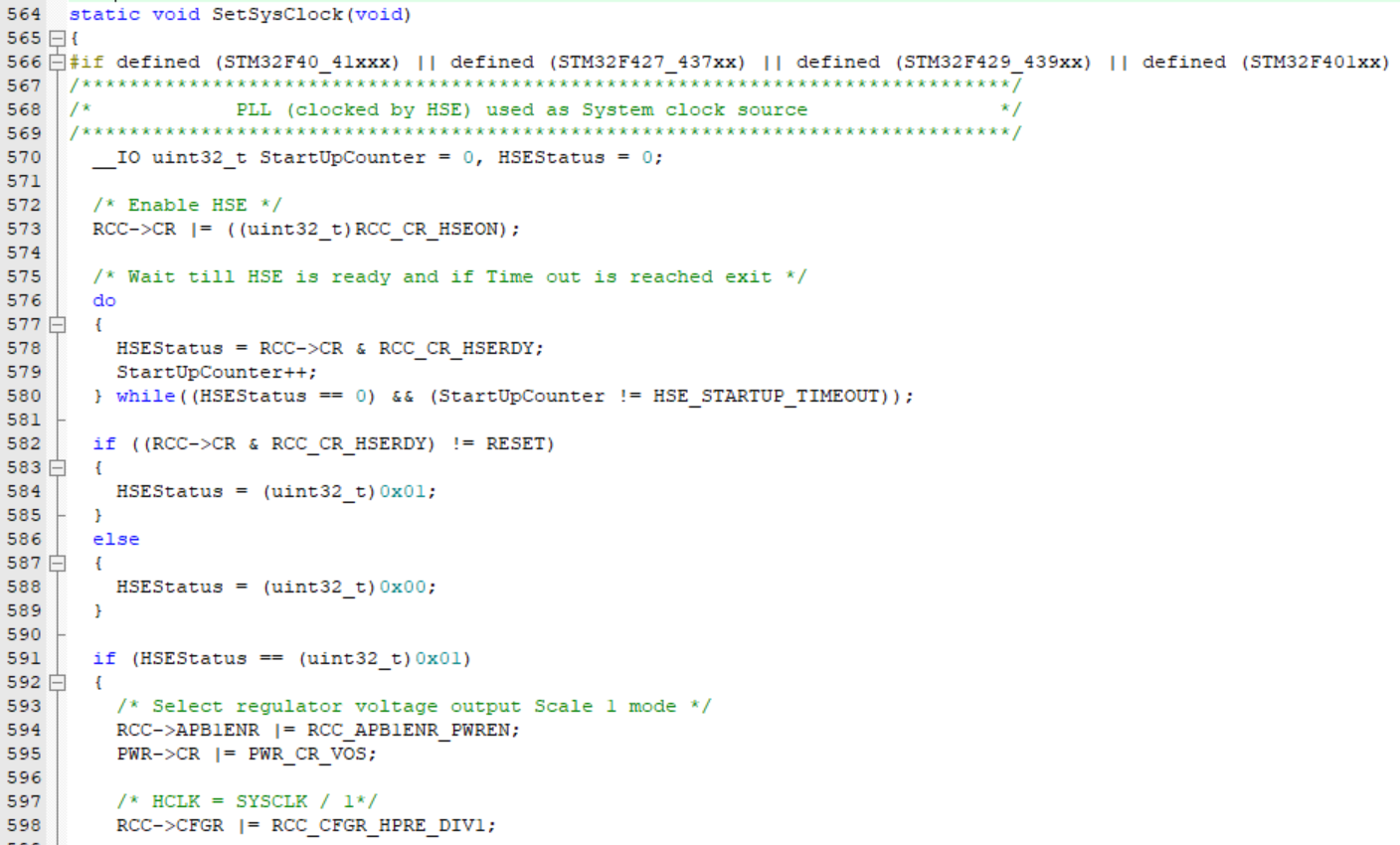

SetSysClock();启动HSE并等待(do while中),开启外部高速晶振HSE(STM32F4 支持动态电压调节:选择Scale 1:1.2V,支持最高 168 MHz)。

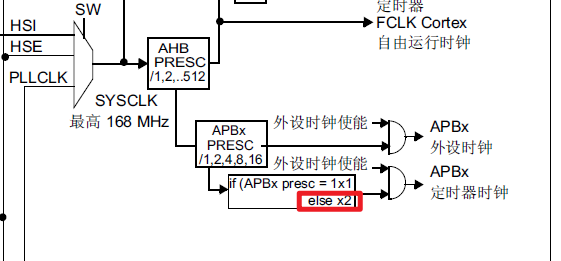

配置AHP和APB分频器

AHB 总线:全速 168 MHz;APB2(高速外设如 TIM1, USART1):84 MHz;APB1(低速外设如 TIM2-7, I2C, SPI2/3):42 MHz;

TIM3 挂在 APB1(42 MHz),因 APB1 分频 ≠ 1 → TIM3 时钟 = 84 MHz

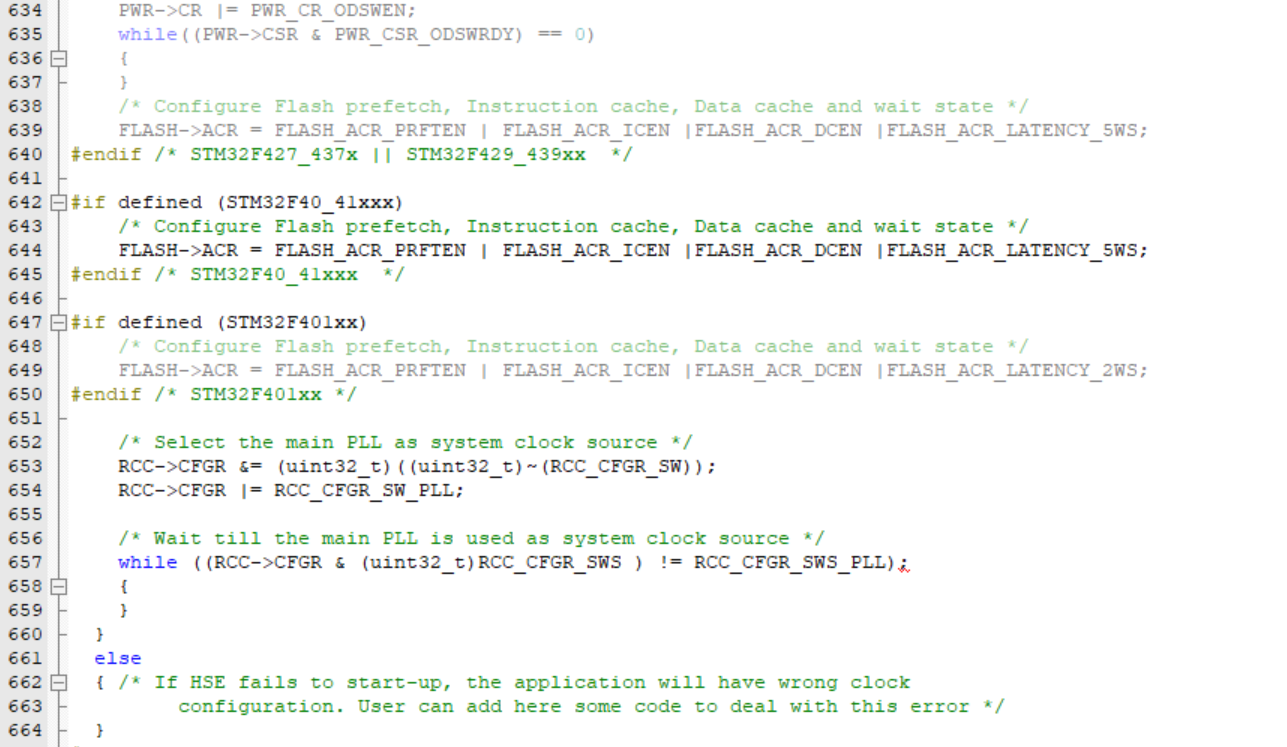

配置PLL寄存器,根据宏定义参数(while等待pll锁定)

切换时钟源为PLL

切换 SYSCLK 到 PLL 后,HSI 和 HSE 仍然保持之前的状态(开启或关闭),RCC 不会自动关闭它们。

至此,时钟配置完毕。

浙公网安备 33010602011771号

浙公网安备 33010602011771号