FPGA基础——异步FIFO的深度计算

一、理论基础与核心原则

-

异步FIFO的作用

异步FIFO用于解决跨时钟域的数据传输问题,尤其当写速率 > 读速率时,需通过缓存机制应对速率差带来的瞬时数据堆积。- 关键目标:确保在最大突发写入情况下,数据不溢出(FIFO未满)且不丢失(FIFO未空)。

-

最坏情况假设

计算深度需基于背靠背(Burst)写入的最恶劣场景,即连续两次突发写入之间无空闲周期,此时数据堆积量最大。 -

同步与资源优化

异步FIFO深度通常选择2的幂次方,以便利用格雷码(Gray Code)编码读写指针,减少跨时钟域同步时的亚稳态风险。

二、深度计算公式及推导

1. 基本公式

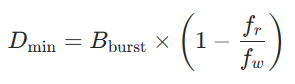

当写速率 > 读速率时,最小深度计算公式为:

- Bburst:单次突发写入的数据量;

- fr、fw:写时钟和读时钟频率。

2. 扩展公式(含空闲周期)

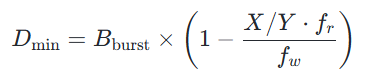

若写入或读取存在空闲周期,需调整有效速率:

- X/Y:读操作的有效速率(例如每Y个周期读取X个数据)。

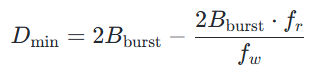

3. 背靠背写入场景

两次突发写入总长度为 2Bburst,此时公式修正为:

三、实例分析

案例1:AD采样与FPGA接口

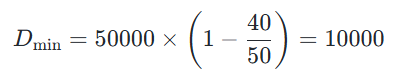

- 条件:AD采样率 fw=50 MHz,FPGA读取速率 fr=40 MHz,需传输5万个数据。

- 计算:

- 实际深度:选择 2^14=16384。

案例2:背靠背写入与空闲周期

- 条件:写时钟 fw=200 MHz(每100周期写40数据),读时钟 fr=100 MHz(每10周期读8数据)。

- 突发长度:两次突发写入共80数据(40+40)。

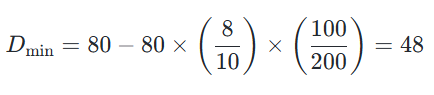

- 计算:

- 实际深度:选择64(2^6)。

浙公网安备 33010602011771号

浙公网安备 33010602011771号