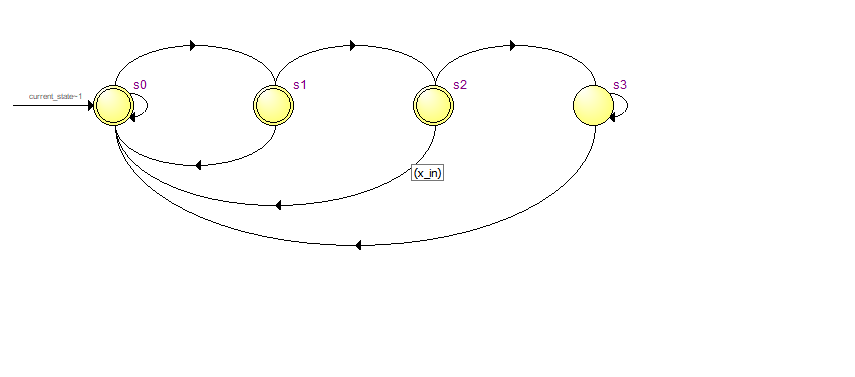

module melay_1 (input x_in,clk,rst_n, output reg y_out); reg current_state,next_state; parameter s0=2'b00,s1=2'b01,s2=2'b10,s3=2'b11; always@(posedge clk or negedge rst_n) begin if(!rst_n) current_state<=s0; else current_state<=next_state; end always@(current_state or x_in) begin case (current_state) s0: if (!x_in) next_state<=s1; else next_state<=s0; s1: if (x_in) next_state<=s2; else next_state<=s0; s2: if (!x_in) next_state<=s3; else next_state<=s0; s3: if (!x_in) next_state<=s0; else next_state<=s3; default: next_state<=s0; endcase end endmodule

以上这段程序,我们通过软件观察不到它的状态转换图。因为我在编写的时候,没有注意状态机的数据类型的位宽不正确,但是Verilog语法的自由型,并不报错,修改程序。

把上述程序的第四行修改为:reg[1:0] current_state,next_state;

则它的状态转换图可以看到,程序验证没有问题。

浙公网安备 33010602011771号

浙公网安备 33010602011771号