Debug日志

2025.11.11

今天在做TFT LCD屏幕 4线SPI时,出现屏幕背光打开,但是屏幕无任何显示。软件进行了debug好久一无所获,最终检查硬件连线,发现CS引脚存在虚焊(量电压竟然有,测试阻抗才发现虚焊),补焊后正常。程序后续需要加上ID读取,这个样软件debug也不至于没任何反应。

2025.11.13

今天在调试LKS的MCPWM时,发现调用函数更新门限比较值时,发现无法正常更新,调试了很久,才发现是打开了MCPWM中断使能。

2025.11.20

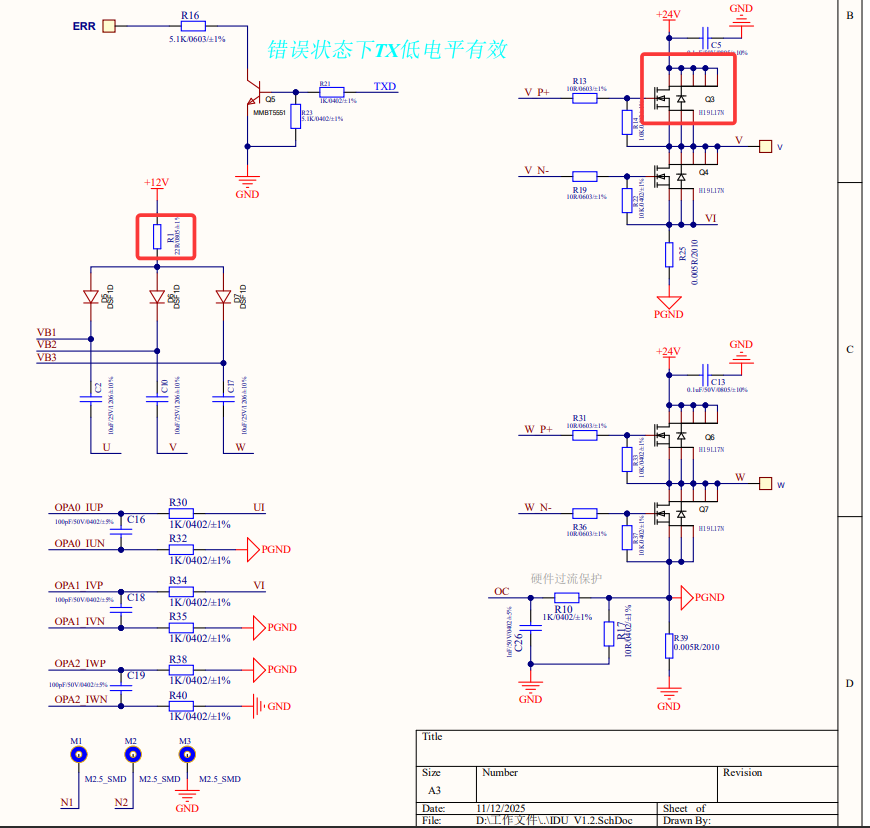

今天有一颗芯片,客户端反馈VB3对地短路,后解焊过程中导致外引脚脱落。外观上看芯片VB3附近存在小鼓包,测试电性HO3,VS3都正常,根据经验怀疑晶圆正常,有可能是封装异常。提出此种思路需要理论支撑,封装专家得评估可能性。需要前瞻性不要过于依赖他人,要质疑别人的观点给出理论依据。

2025.11.21

今天让第三方开封反馈提供的打线材质不对。封装金蝶的074D型号,实际上传的07DO的打线图。看了每一个步骤都得细心检查。有再看了一下,发现是索引关键字看错了,包含和等于。

2025.11.26

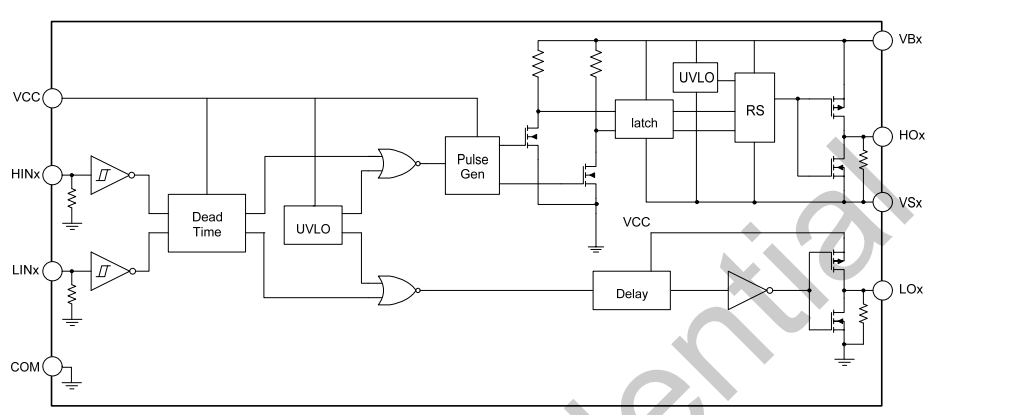

今天处理了疑似VS2负压的客诉。关于预驱结构有了更多的认识:

第一步:VS出现负压

第二步:芯片内部反并联二极管正向导通

半桥驱动芯片内部,为了保护悬浮驱动电路,会在 VS 脚与内部 VCC 供电端之间,集成反并联钳位二极管(或寄生二极管)。

其设计初衷是:当 VS 脚出现轻微过压时,二极管反向击穿钳位电压;但当 VS 脚出现大幅负压时,这个二极管会被正向偏置导通(因为二极管阳极接内部 VCC,阴极接 VS 脚,VS 为负压时,阳极电位高于阴极,满足正向导通条件)。

第三步:形成 VCC→Rboot→Cboot→芯片内部二极管→VCC 的短路回路

一旦内部反并联二极管导通,就相当于直接把芯片内部 VCC 端和 VS 脚短接。

此时电路形成闭合回路:外部 VCC 电源→限流电阻 Rboot→自举电容 Cboot(因充电不足,近似低阻抗)→芯片内部导通的反并联二极管→回到 VCC 电源。

VS 负压源自两股“力”之间的竞赛:电路“把 VS 往下拉的力”(大 di/dt 和反向恢复之类的瞬态,下桥打开瞬间)与自举回路“把 VS 抬起来/钳住的力”(Cboot 的可用电荷 + HO 驱动)——当前者胜出,VS 就跌入负压区,触发内部钳位/二极管导通,引发大电流回路与破坏。

失效现象分析:

- 产线测试存在三种失效:<1>板载芯片+MOS+电阻烧毁;<2>板载芯片+电阻烧毁;<3>板载

芯片,+MOS烧毁;根据三种不同损伤程度的失效判断是芯片首先发生故障。 - 失效芯片执行FA分析,VS2熔断且附近存在烧伤,说明VS路径存在过流(高能量灌入),推断

过流的原因大概率是VS欠冲产生负压。 - VS负压触发驱动芯片内部的钳位结构正向导通,使VCC经Rboot与VS形成低阻短路回路,导致

Rboot 烧毁并击穿芯片内部悬浮驱动电路。 - 汇总已有失效产品都是在1楼生产线出现,说明特定生产线故障,在VS2产生负压导致失效。

VS2负压产生可能原因: (由高至低) - 特定生产线故障;

- 上电瞬间自举电容充电不完全;

- 下桥驱动管开关瞬间;

- V相的驱动回路寄生电感偏大。

浙公网安备 33010602011771号

浙公网安备 33010602011771号