集成电路工艺与器件

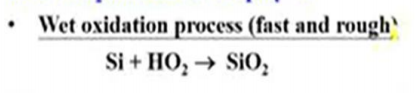

干法刻蚀与湿法刻蚀

干法刻蚀高能离子与材料表面的相互作用

湿法刻蚀主要基于溶液中的化学反应

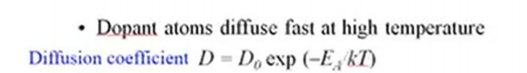

掺杂方法

热扩散、离子注入

扩散系数

快速退火

晶体缺陷修复:在半导体制造过程中,快速退火可帮助修复由于离子注入、沉积或蚀刻等步骤引入的晶体缺陷。通过高温快速退火,晶体中的缺陷可以重新排列和修复,从而提高晶体质量和电学性能。

激活掺杂离子:快速退火可用于激活和扩散掺杂离子。在离子注入后,通过快速加热样品至高温并快速冷却,掺杂离子可以在晶体中进行有效的扩散,从而形成所需的电学特性。

阴阳光刻胶

阳性光刻胶在光照后会发生化学变化,使得光刻胶的暴露部分变得可溶解,从而形成图案。阴性光刻胶则是在光照后,未受到光照的部分会变得可溶解,形成图案。

光刻机种类

光刻半径

焦深和数值孔径的平方成反比。这意味着,为了获得更小的特性尺寸,需要使用更大的数值孔径,焦深将会变小,从而导致对焦更为困难。

解决办法:增大NA(更大的数值孔径、增大光刻胶对焦偏差的容忍范围)、减小波长(发展新型光源、DUV to EUV(13.5nm))、增大K(相移掩模)

移相掩模(PSM)

在Mask的透明图形上增加一个透明的介质层-移相器,使光通过后产生180的相位差。

作用:通过光的干涉,消除图形边缘的衍射,从而提高分辨率。

OPC

OPC是光刻修正(Optical Proximity Correction)的缩写,是一种在光刻工艺中用于改善图形形状和尺寸的技术。

优点:

提高图形准确性:OPC技术通过对光刻图形进行修正,能够有效地提高图形的形状和尺寸的准确性。这对于微电子制造来说至关重要,可以帮助确保电路的功能和性能符合设计要求。

提高光刻过程容差:OPC技术可以增加光刻过程中的对焦容差范围,也就是DOF。这使得光刻胶对焦偏差的容忍度更大,降低了光刻过程中对对焦精度的要求,提高了工艺的可靠性和稳定性。

适应复杂结构:随着芯片尺寸的减小和复杂性的增加,光刻工艺需要应对更加复杂的结构。OPC技术能够根据不同的设计要求和工艺需求,灵活地进行优化和修正,使得光刻图形能够更好地适应复杂的结构。

缺点:

增加工艺复杂性:OPC技术需要对光刻图形进行额外的计算和修正,这增加了工艺的复杂性和计算量。这要求有专门的软件和算法支持,并可能增加芯片制造过程中的时间和成本。

可能引入新的制造问题:尽管OPC技术可以改善图形的形状和尺寸,但有时候可能会引入新的制造问题。这可能包括光刻图形在修正过程中出现的奇点、边缘偏差或者光刻胶的不均匀性等问题。

依赖模型准确性:OPC技术的有效性取决于模型的准确性。如果模型与实际工艺不匹配或者参数不准确,修正后的图形可能仍然无法满足要求。因此,建立准确的模型和对其进行校准是关键的,但也需要额外的工作和资源投入。

epi层

外延层用于提供更清洁的层设备形成并防止CMOS晶体管形成“闩锁”。EPI层在半导体制造中具有优化晶体质量、改变材料属性、提供结构设计灵活性和缩小器件尺寸等多重作用。当一个CMOS电路中的PNP(正负正型)和NPN(负正负型)晶体管同时处于导通状态时,就会发生串通效应,这会导致一条短路路径。

Finfet中,PMOS: 外延生长SiGe层,利用SiGe晶格常数与Si不匹配,使沿沟道方向的Si受到压缩产生压应力,从而提高了沟道Si中的空穴迁移率。

NMOS:外延生长SiC层,通过在沟道中产生单轴压应力来提高N M0SFET的电子迁移率。

槽刻蚀

分为4个步骤:

①隔离氧化层;

硅与氮化物的应力消除层,抗蚀剂

②氮化物淀积;

掩膜层,抛光停止层

③第三层掩膜(浅槽隔离);

④STI槽刻蚀,

离子刻蚀

⑤去除光刻胶

氧等离子体

⑥CVD氧化层

防止晶体管互相干扰

⑦cmp

化学抛光

⑧h3po4去除氮化物,HF去除氧化层

牺牲氧化物层:一种薄的氧化物层生长以捕获硅中的缺陷表面

栅氧化层:纯度高,薄。作为晶体管的电介质

1.低温氧化

2.惰性气体稀释O2

1st Interconnect Layer

第一层互连层的主要功能是将晶体管的源极、漏极等区域与其他电路单元进行电连接。这一层使用一种称为金属填充(metal fill)的工艺,通过在晶体管之间和周围填充金属导线,实现电流传输和信号传输。

LDD

低掺杂扩散(Low Dose Diffusion)的缩写。

在LDD中,掺杂的过程被分为两个阶段:首先是LDD区域的低掺杂,然后是高掺杂的源和漏区域。低掺杂区域的目的是在源和漏之间形成一个渐变的掺杂剖面,在高电场情况下减弱电子和空穴的散射效应。

通过LDD技术,可以减小热效应,减少隧穿的电子数,减少电场。这有助于提高MOS器件的性能、可靠性和稳定性。

TIP

N_TIP用砷离子,P_TIP用BF2。作用:阻碍热电子效应。

阱

N well用磷,P well用硼。

RIE:反应离子刻蚀 同时利用了等离子刻蚀和溅射刻蚀机制(化学刻蚀和物理刻蚀的结合)

Self-Aligned Silicide:自对准硅化物技术。

首先在整个晶片表面上沉积一层金属(通常是钨、钛、铚等),然后进行一个热处理步骤。热处理过程中,金属会与晶片表面上的硅发生反应,形成金属硅化物。通过适当的处理条件和控制,通常可以实现硅化物反应限定在源漏和栅极区域。硅化物具有低电阻性能,可以降低电阻并提高器件的性能。

TiSi2在硅化物与金属之间形成欧姆接触。

欧姆接触与肖特基接触

欧姆接触是一种低电阻的接触结构,可以让电流以欧姆接触方式流过。在欧姆接触中,金属电极与半导体材料之间形成良好的能带匹配,使得电流能够顺利地通过,而不会发生明显的反射和散射。欧姆接触的特点是电流随电压的增加而线性增加,且接触电阻较低。

肖特基接触则是一种特殊的接触结构,它由半导体材料与金属之间的异质结构组成。肖特基接触中,金属与半导体之间存在一个肖特基势垒,这个势垒可以阻碍电流的流动。肖特基接触的特点是对于正向偏置情况下的电流流动较好,但在反向偏置时电流流动会受到较大阻碍。肖特基接触具有整流特性,可以用于制作二极管等器件。

BPSG

二氧化硅掺杂少量硼和磷,以使薄膜回流并使用化学气相沉积吸附污染物。填充结构的空隙和孔洞,在后续的工艺步骤中可以进行平坦化和绝缘处理。

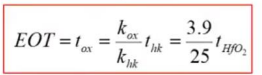

EOT计算

Gate-first和Gate-last

Gate-first和Gate-last的区别主要体现在栅极结构的形成顺序。Gate-first工艺可以更容易地控制栅极的形状和尺寸,因为它是在早期步骤中完成的。然而,由于栅极是在较早的阶段形成的,其材料可能会受到后续制造步骤的影响。另一方面,Gate-last工艺在形成栅极之前完成了其他部分的制造,可以减少栅极材料受到其他步骤的损害或污染的可能性。

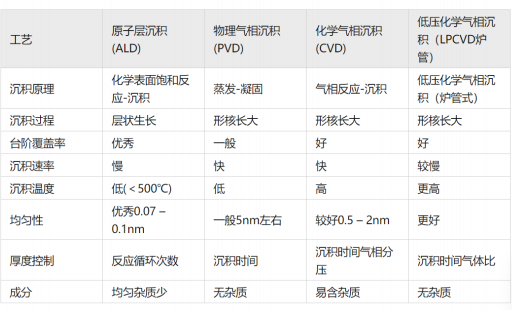

沉积技术

传统平面的挑战

VT roll-off是指晶体管的阈值电压(Threshold Voltage)随通道长度缩短而发生的变化。阈值电压不稳定,非线性,降低。解决办法:浅结、薄栅极氧化物、重掺杂

DIBL:

短沟道效应:电场峰值的增加,从而可能引起热效应、漏电和击穿等问题。

Finfet

优势:

增强对于短沟道效应的控制。

减少DIBL效应。

Vdd很低,低能耗。

高可扩展性。

缺点:

- 必须严格控制每个翼片的高度和宽度,这些关键尺寸影响器件性能。

- 良好的刻蚀选择性,并除去翼片和栅角落的残留物。

- 钨填充带来了额外的困难。理想情况下,这种钨金属可以被沉积而不留下任何孔隙(空洞),随着结构变窄得越来越困难。

SADP

自对准双重图案形成技术

优势:1.同样的光刻步骤可以进行不同步长的光刻

2.实现2的n次方的增长

3.对于finfet来说,Fin width更加统一

BULK finfet与SOI finfet

前者:1.需要PTS层 2.需要HALO(在器件的特定区域周围引入高浓度的掺杂物) 3.形状像鱼鳍

后者:1.不需要沉积来避免PT 2.长方形形状

缺陷

- 纯度不够 氧气为常见来源。

- 污染物(杂质颗粒,金属污染物,有机污染物,自身的氧化)

- ⚫拉应力(tensile stress):薄膜就会破裂甚至剥离基体而翘起。

⚫压应力(compressive stress),薄膜向基板内侧卷曲,导致膜层起泡.

主要来源

✓外应力: 由外力作用施加于薄膜所引起的。

✓热应力: 基体与膜的热膨胀系数相差太大而引起

✓內应力: 薄膜本身与基体材料的特性引起的, 主要取决于薄膜的微观结构和分子沉积缺陷等因素,薄膜彼此的界面及薄膜与基体边界的相互作用就相當重要

致命缺陷符合”1/3原则”:致命缺陷尺寸大小约为最小特征尺寸的三分之一

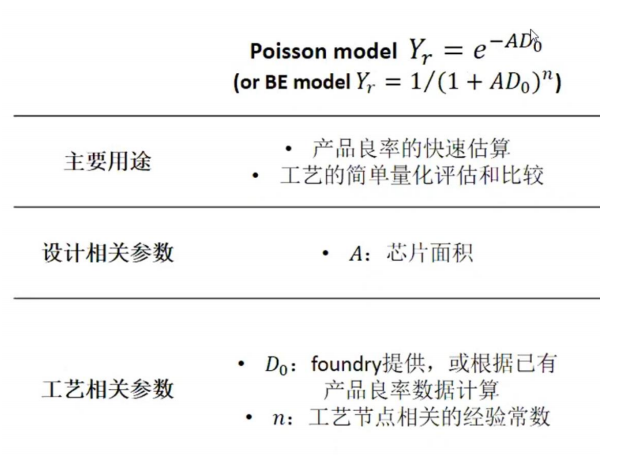

良率模型

前提:芯片所有区域受到defect的影响完全一样。

多晶硅的问题

1.Cox较小,意味着对栅极电压变化的响应程度较小。

2.电导率较低:相对于单晶硅,多晶硅的电导率较低。

3.多晶硅的费米能级位置直接影响了器件的门阈电压。

高介电常数(High-K)材料与金属栅(Metal Gate)

高介电常数(High-K)材料与金属栅(Metal Gate)是微电子器件制造中的两个关键技术,用于替代传统的多晶硅栅材料,以提高场效应晶体管(FET)的性能。

传统的栅结构是由多晶硅材料构成的,用于控制器件通道的电场。然而,随着器件尺寸的不断缩小,多晶硅栅的尺寸也变得难以满足需求,产生一些限制。为了克服这些限制,引入了高介电常数材料和金属栅技术。

高介电常数材料是一类具有高相对介电常数的材料,可以在较薄的厚度下提供与传统氧化硅相同的栅电容。这样可以减少栅电极的尺寸并增强电场控制能力。常用的高介电常数材料有氧化铪(HfO2)和氧化锆(ZrO2),它们具有更高的介电常数和较低的泄漏电流。

金属栅是指用金属材料取代传统的多晶硅栅电极。金属栅材料通常选用具有优异电导性和稳定性的金属,如钨(W)或钼(Mo)。金属栅材料的导电性能更好,使得器件具有低电阻和更快的开关速度。

优势:1.电阻低,可以提高开关速度。2.去除费米能级,增加迁移率

EBL

EBL (Electron Beam Lithography)是一种高分辨率的光刻技术,常用于微纳米制造和纳米器件研究中。

EBL 使用一个高能的电子束来控制性地曝光在光敏物质上,从而在光刻层中形成所需的图案和结构。它具有以下特点:

高分辨率:由于电子具有较短的波长,EBL 可以实现非常小的图案尺寸和高分辨率。通常,EBL 可以达到亚纳米级别的分辨率,使其成为纳米器件制造和研究的理想选择。

灵活性:EBL 可以根据需要创建复杂的图案和结构,可以制作出不同尺寸、形状和排列的微纳米特征。这种灵活性使其在纳米电子、光子学、生物医学和纳米磁学等领域具有广泛的应用。

直接写入:与传统的光刻技术相比,EBL 是一种直接写入技术,可以实时、灵活地控制电子束进行图案曝光。这意味着可以在同一样本上制作不同的图案,提高工艺的效率与灵活性。

然而,EBL 也有一些局限性,如曝光速度相对较慢、设备和操作成本较高。因此,在实际应用中,EBL 往往用于对分辨率要求极高的特殊制造过程,或者在科研领域用于构建微纳米结构和研究新材料的特性。

工艺节点定义

1/3 pitch(指相邻FIN之间的间距或间隔长度)

扩展

浸入式光刻

在透镜与Si片间,用折射率大于1的液体(如水,n=1.44)替换空气介质,可使NA增大。

浙公网安备 33010602011771号

浙公网安备 33010602011771号