fpga时序约束 - set_input_delay

set_input_delay,是指信号到达fpga的pin脚相对于参考时钟的延迟,这里fpga是下游器件,因为上游芯片的数据和时钟到达fpga管脚的相位关系不确定,而为了满足时序要求,fpga必须要知道这个值,好来做内部布局布线,同时满足建立时间和保持时间的要求公式:

- Tco_ext + Tpcb_ext + Tdelay_inter <= Tclock -Tsu

- Tco_ext + Tpcb_ext + Tdelay_inter >= Th

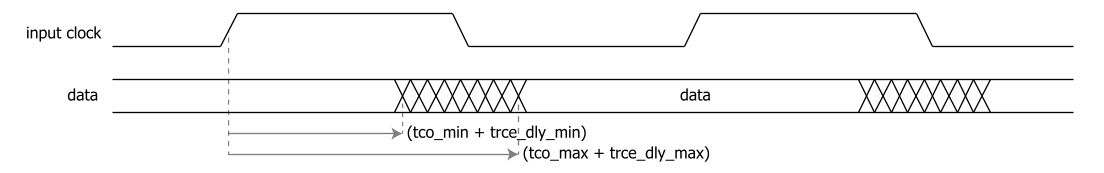

注意这里:Tsu指的是fpga自己内部的reg的Tsu,不是外部的,Th也是。而Tco_ext和Tpcb_ext分别就是上游芯片的寄存器输出延时和信号在pcb上走线延迟。这俩式子,Tco_ext 和 Tpcb_ext是工具不知道的,所以要通过约束语句告诉工具,这俩就是输入的延迟。xilinx手册里有个图可以帮助我们理解:

所以,我们通常这样写set_input_delay约束:

- set_input_delay -clock xxx -max Tco_ext(max) + Tpcb_ext(max) [get_ports xxx]

- set_input_delay -clock xxx -min Tco_ext(min) + Tpcb_ext(min) [get_ports xxx]

Tco一般我们要去上游芯片手册里去查,这个指标一般不会写直接Tco,比如AD7699的手册:

图里,SCK Falling Edge to Data Valid Delay其实指的就是Tco。

有些手册可能会写Tsu是多少,我们也可以大致推算出Tco的值,就是Tco = T- Tsu,如图所示:

类似这个手册:

最后我们可能会在某些input_delay约束里看到负值,负值怎么理解?典型的input_delay里,数据一般是晚于发送时钟沿的,相位关系大致是这样的:

这个图可能更直观一些:

所以负值的意思,就是数据比发送的时间沿还要早到达,这个其实对保持时间的约束提出了较高的要求,综合工具可能会在内部加很多buffer来增加延迟,所以值的正负反映的其实是数据和时钟的相位关系。假设我们不设置任何input_delay的话,是欠约束还是过约束了呢?答案是欠约束,因为不做任何约束,相当于设置delay为0,也就是数据和时钟同时都到了fpga口上,对于建立时间来说,数据提前了很多,建立时间的裕量很多,实际是有延迟的,没有那么多裕量,所以是欠约束了,相反,如果max设置的很大,就是告诉工具,数据到达的很晚,为了满足fpga内部的寄存器Tsu要求,fpga内部就会拼命优化走线,去满足时序要求。就是过约束。针对min来说,不做设置,则数据只有fpga内部的延迟,为了满足Thold的要求,fpga内部就会插buffer,但是实际有延迟fpga内部就不会加buffer了,所以也是欠约束。min设置的越小,保持时间要求就越紧张,就是过约束。

浙公网安备 33010602011771号

浙公网安备 33010602011771号