浅谈FPGA里的LUT

通俗易懂的解释下LUT,大部分人都说叫查找表,确实,它原本英文就叫"look up table"。但是具体怎么实现的,啥是4输入lut,6输入lut?

首先,这个查找表其实就是真值表,假设有个组合逻辑关系y = (A & B) | C,它的真值表:

| A | B | C | y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 |

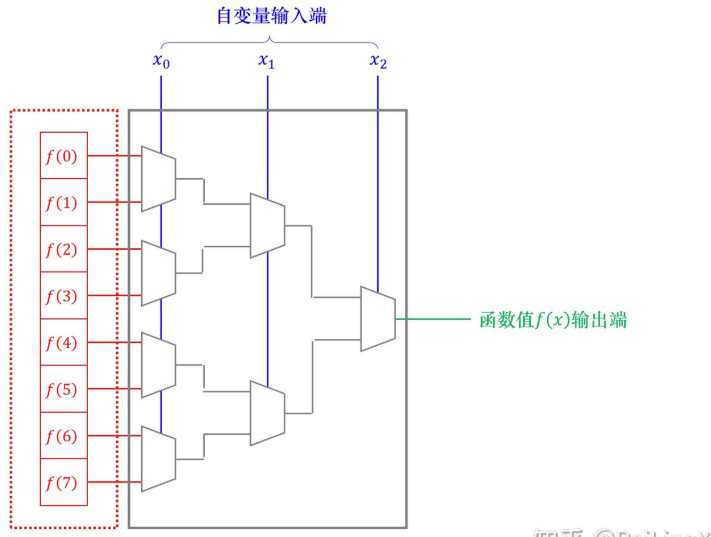

fpga要实现这个组合逻辑时,做的就是把这个结果y的值,都存起来,存在sram里,然后通过输入信号A B C,不同输入组合,就输出对应的结果值,这个操作就很像寻址的操作一样,A B C就是3根地址线,根据地址拿数据。但是具体是怎么做到地址组合和结果相对应的?它其实是使用了mux,很巧妙的设计。先看个图:

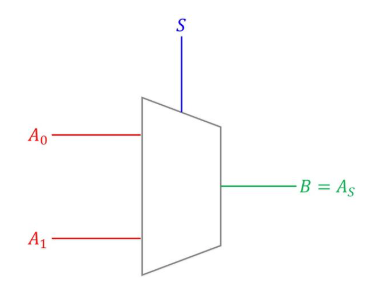

图里左侧f(0)到f(7)就是所有的组合逻辑输出y的值,存放在sram里,A B C就分别对应x0 x1 x2。mux选择电路就是当选通S有效时,选择下面的A1输出,否则选择上面的A0输出:

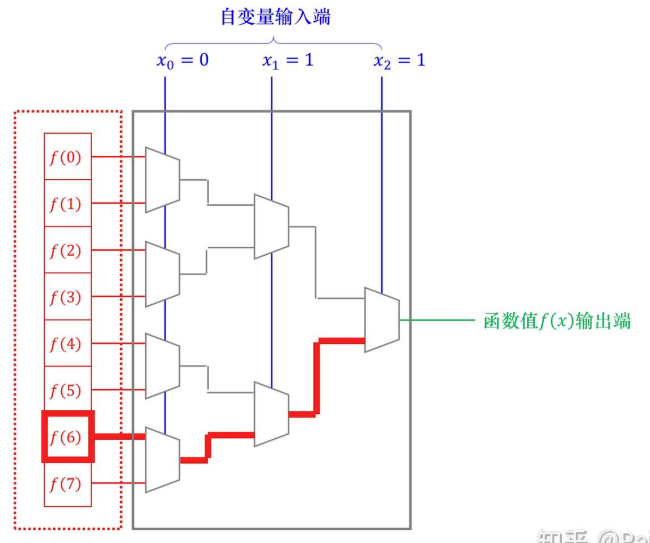

假设A B C 是 0 1 1,则x0 x1 x2就是011,看真值表应该输出f(6),我们看下逻辑电路是怎么找到f(6)的,

- x2是1,走下面的通路

- x1是1,走下面的通路

- x0是0,走上面的通路

正好找到f(6):

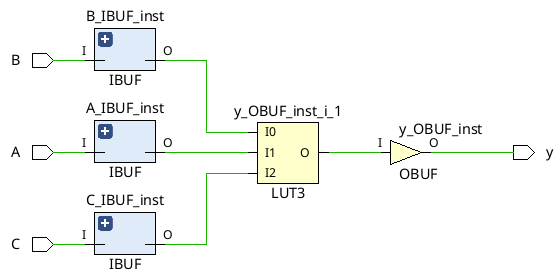

同理假设输入是010,按规则也正好找到f(2)。可见LUT的核心组成就是sram+mux。实际中,组合逻辑可能不止这几个变量,我们开头提到的lut4表示最多支持4个变量的输入,可以存储2^4个函数值,这里只有3个值,在vivado这里,工具会优化成LUT3,可能是LUT6拆成的,也可能是LUT4屏蔽了一个输入,我没有很确定,但是综合后是LUT3:

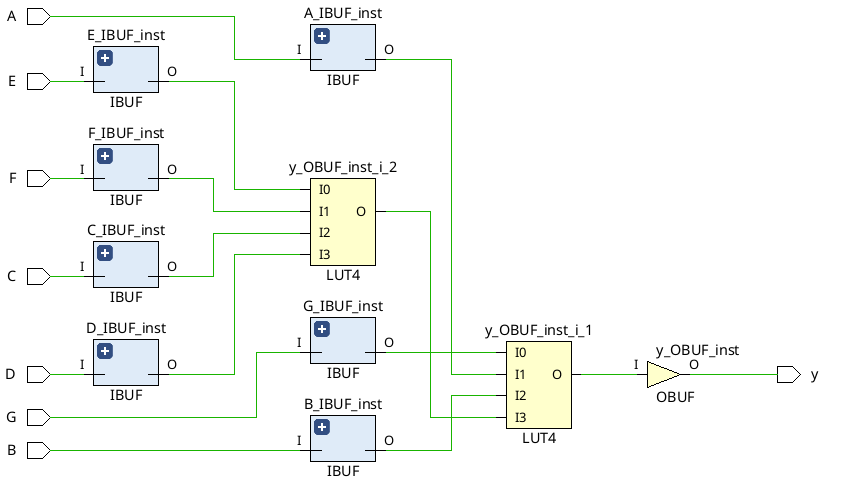

当输入个数很多时,就会采用LUT级联的方式,也就是几个LUT连接完成一个组合逻辑,毫无疑问,这加大了信号的延迟,对高频系统来说这不是好事,通常的做法就是拆分,中间插入寄存器的形式。

参:

浙公网安备 33010602011771号

浙公网安备 33010602011771号