XILINX FPGA局部重构的一些关键概念和方法-bitstream

XILINX FPGA局部重构的一些关键概念和方法-bitstream

Bitstream 类型定义 (ug909)

在进行局部重构设计时,bitstream 分为如下类型:

• Full Configuration Bitstreams

• Partial Bitstreams

• Blanking Bitstreams 这里不做解释

• Clearing Bitstreams

DFX 解释:Dynamic Function eXchange 也就是局部重配置,是一个概念

Full Configuration Bitstreams

所有 DFX 设计都从使用全配置比特流对整个器件进行标准配置开始。这种全配置比特流的格式和结构与普通非DFX设计(平面设计)完全相同(只有一个例外),并且该比特流用于初始编程 FPGA 的方式也完全一致。

唯一的区别在于:对于 DFX 设计,全局信号屏蔽(global signal mask)是关闭的;而在每次加载部分(或清空)比特流时,该屏蔽会被打开,以仅影响目标可重配置区域。正因如此,在初始配置之后,不能再触发芯片范围的 GSR(全局复位)事件。

但请注意,该设计本身已经过处理,为在完成全配置之后进行部分重配置做好了准备。标准功能如加密和压缩仍然是支持的。

设置为黑盒(black box)的 RP(Reconfigurable Partition,可重配置分区)也是被支持的,因此可以在初始配置中包含没有实际功能的 RM(Reconfigurable Module,可重配置模块),并在后续用所需的 RM 进行替换。在这种情况下,比特流压缩可以有效减少比特流的大小以及初始配置所需的时间。

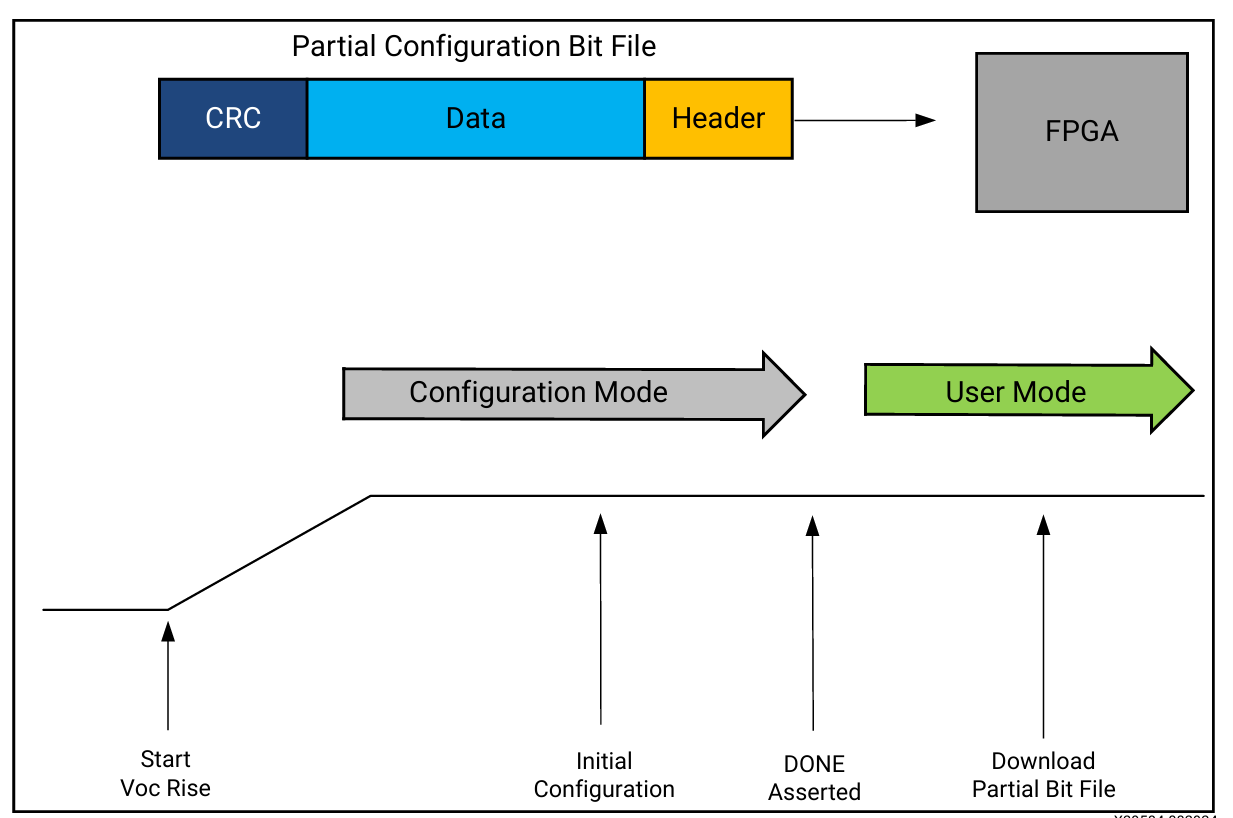

初始配置完成后并经过验证,FPGA 将进入用户模式,下载的设计开始正常运行。如果检测到 BIT 文件损坏,则 DONE 信号不会被置位,FPGA 也不会进入用户模式,损坏的设计将永远不会开始运行。

Partial Bitstreams

在器件正常运行期间,部分比特流(Partial Bitstream) 被加载,用于替换预定义区域中的功能。这些比特流与全比特流具有相同的结构,但仅限于特定的地址范围,以编程器件中的特定部分。

DFX 专用功能也得到支持,例如:

逐帧 CRC 校验(确保比特流完整性)

自动初始化(使该区域进入已知状态)

此外,全比特流所支持的功能(如加密和压缩)也同样适用于部分比特流。部分比特流的大小与它所重配置的区域大小成正比。例如,如果某个可重配置分区(RP)占用了器件资源的 20%,那么对应的部分比特流大小大约是全比特流的 20%。

部分 BIT 文件具有简化的文件头,并且不包含启动序列(startup sequence),因此不会使 FPGA 进入用户模式。该 BIT 文件(在默认设置下)本质上仅包含帧地址和配置数据,以及一个最终的校验和值。如果需要,也可以插入额外的 CRC 校验,以执行比特流完整性检查。

如果启用了 “重配置后复位(Reset After Reconfiguration)” 功能,则在开始重配置时,DONE 引脚会变为低电平,在部分重配置成功完成后再次拉高。当然,你也可以通过内部方式监控部分比特流的加载过程。

⚠️ 注意:对于 UltraScale 器件,在清空比特流(clearing bitstream)开始时,DONE 引脚会被拉低,并且在整个清空比特流和随后的部分比特流过程中保持低电平,因为这两个比特流共同构成了一次完整的部分重配置流程。在清空比特流结束后,DONE 引脚不会恢复为高电平。

如果没有启用“重配置后复位”,则必须通过监控发送的数据来判断配置何时完成。一个部分 BIT 文件的结尾包含一个 DESYNC 字(0000000D),它通知配置引擎该 BIT 文件已完全传输完毕。这个 DESYNC 字出现在一系列填充用的 NO OP 命令之后,确保一旦到达 DESYNC,所有配置数据已经发送到器件中的目标帧。

一旦整个部分 BIT 文件被完整地发送到配置端口,就可以安全地释放可重配置区域,使其进入可用状态。

🔍 小结关键点:

|

内容 |

说明 |

|---|---|

|

部分 BIT 文件结构 |

简化头部,无启动序列,仅含地址、数据和校验 |

|

CRC 校验支持 |

可选,用于保证比特流完整性 |

|

DONE 引脚行为 |

若启用“重配置后复位”,会在重配置期间拉低并在完成后拉高;否则需手动监控 |

|

UltraScale 特殊情况 |

清空 + 部分比特流是一个整体流程,DONE 在整个流程结束前保持低电平 |

|

DESYNC 字 |

0000000D,表示比特流传输完成 |

|

安全使用时机 |

收到 DESYNC 后即可确认配置完成,释放 RP 区域 |

Clearing Bitstreams

与上述比特流类型不同,这种比特流仅用于 UltraScale 器件(UltraScale+ 不需要此步骤)。

对于该架构的一个新要求是:在加载新的功能模块之前,必须先清空已有的模块。

这种“清空比特流(clearing bitstream)”的作用是在向某个可重配置区域(RP)加载后续的部分比特流之前,建立该区域的全局信号屏蔽(global signal mask),为设备做好准备。虽然从技术上讲,原有模块并没有被真正移除(当前逻辑模块仍然存在),但可以简单地理解为它已被“清除”。

如果不加载清空比特流,那么接下来的 RM(Reconfigurable Module,可重配置模块)将不会被正确初始化。

清空比特流不是部分比特流。它们通常只包含目标区域不到 10% 的帧数据,因此其大小也通常小于对应部分比特流的 10%。

它们不会改变功能逻辑,但会关闭驱动该区域逻辑的时钟。

清空比特流必须在两个部分比特流之间加载,并且应尽快紧接着加载下一个部分比特流。

✅ 关键点总结:

|

项目 |

说明 |

|---|---|

|

适用器件 |

仅适用于 UltraScale,7 系列,UltraScale+ 不需要 |

|

清空比特流作用 |

建立全局信号屏蔽,为部分重配置做准备 |

|

是否改变功能 |

否,只是关闭时钟、准备区域 |

|

大小 |

小于目标区域帧数的 10%,比部分比特流小得多 |

|

使用方式 |

必须在两次部分比特流之间使用,并紧接部分比特流发送 |

示例

下面是一个KU040 FPGA的测试示例

如何生成下载所需bitstream

VIVADO 基本流程不在这里描述,这里只描述如何把局部bit文件转换为内部配置接口接受的配置帧数据。

Partial Bit 文件(部分比特文件)与 Full Bit 文件(完整比特文件)具有相同的基本格式,但它们只包含目标区域的配置帧(bin文件删除了bit文件的文件头信息),并且仅限于与有效设备相关的配置事件。

Partial Bit 文件可以:

- 通过外部接口(如 JTAG 或从设备配置端口)加载;

- 被重新格式化为 BIN 文件,用于加载到内部配置端口:

- ICAP(适用于 7 系列或 UltraScale 器件)

- PCAP(仅适用于 Zynq 器件)

- MCAP(仅适用于 UltraScale 器件)

使用 write_cfgmem 工具生成 BIN 文件时,有三个关键选项需要注意:

- 使用 -format BIN 指定生成的是 BIN 文件类型;

- 使用 -interface 设置 SelectMap 的宽度:

- 对于 PCAP 或 UltraScale ICAP 使用 SMAPx32;

- SMAPx16 和 SMAPx8(默认)可用于 7 系列 ICAP;

- 如果是 7 系列加密的部分比特流,则必须使用 SMAPx8;

- 必须使用 -disablebitswap 参数来适配 PCAP 或 MCAP。

- ✅ 示例

7 系列器件的 ICAP 配置:

write_cfgmem -format BIN -interface SMAPx8 -loadbit "up 0x0 <file.bit>"

UltraScale 器件的 ICAP 配置:

write_cfgmem -format BIN -interface SMAPx32 -loadbit "up 0x0 <file.bit>"

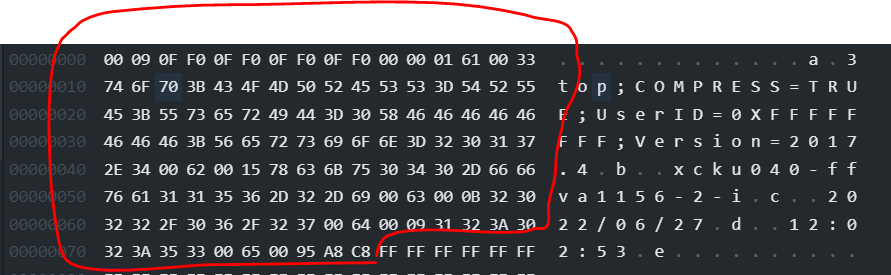

图 1 bit文件头,bin文件会删除这个头 只保留配置数据

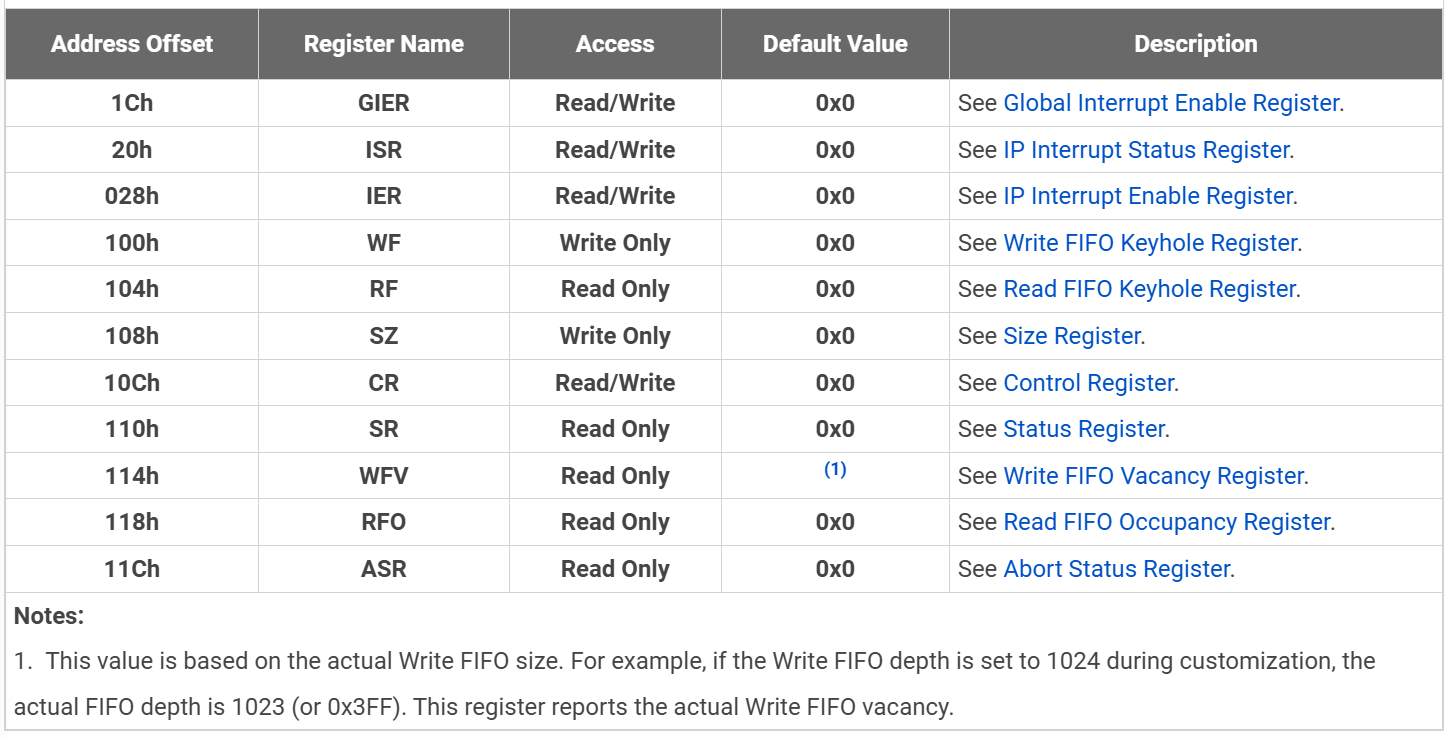

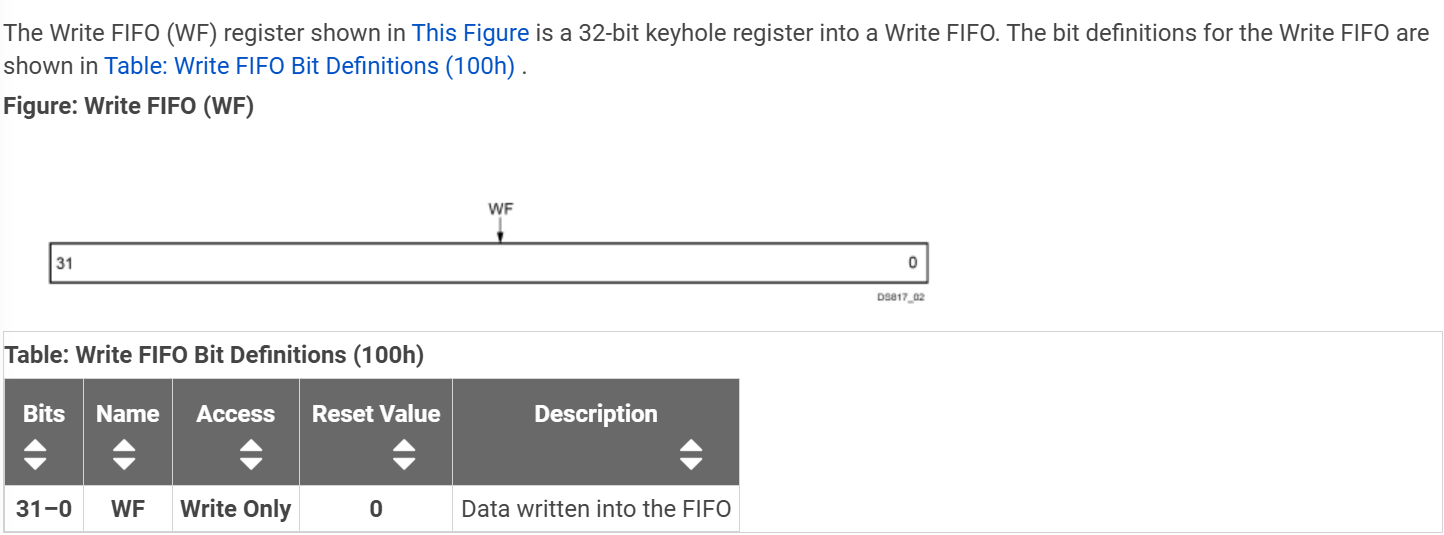

如下通过内部接口下载bitstream (PG134)

AMD 的 AXI HWICAP(Hardware Internal Configuration Access Port,硬件内部配置访问端口)LogiCORE™ IP 核通过 AXI 接口,使嵌入式微处理器(如 MicroBlaze™ 处理器)能够通过 ICAP(Internal Configuration Access Port) 读取和写入 FPGA 的配置内存。这使得你能够编写软件程序,在电路运行过程中动态修改电路结构和功能。

重点关注CR,FIFO寄存器

注意FIFO 的32bit都是有效数据,那么bitstream 填充的时候就要将其填满。

如何写入bitstream

- 将指令写入写 FIFO 寄存器(Write FIFO Register)以进行配置。

- 向控制寄存器(Control Register)写入值,以启动指令的写入操作。

CR 寄存器决定了数据传输的方向。向控制寄存器中写入 0x00000001 将启动配置写入操作。 - 配置成功完成后,硬件会自动清除控制寄存器中的相关位。

- 将第二条指令写入写 FIFO 寄存器,并再次向控制寄存器写入以启动对 ICAPEn 的写入操作。

- 重复此过程,直到所有指令都被写入 ICAPEn。

因此看来,用户不需要关心bitstream的细节,直接写入即可(由于.bit文件有无用的文件头,因此需要真正写入的bitstream文件是去除了文件头的bin文件)。

重点注意:

- 写入时,如果FIFO 深度只有64,那么每次可以先写入64深度数据, 然后控制CR开始写入,检查是否FIFO空,空则继续写入下一个64,循环直到全部写入。

浙公网安备 33010602011771号

浙公网安备 33010602011771号