FPGA 配置方式与配置文件结构说明

✅ Xilinx(AMD)7 系列 FPGA 的配置机制

🧩 核心概念

- FPGA 是“空白”硬件,必须通过加载bitstream(比特流)文件来定义其功能。

- Bitstream 是一个二进制文件,包含所有逻辑、互连和 I/O 的配置信息。

- 配置数据存储在 CMOS 配置锁存器(CCL)中,属于 SRAM 型存储单元,掉电后丢失。

⚙️ 配置方式

FPGA 可以通过多种接口从不同来源加载 bitstream:

| 配置模式 | 说明 |

|---|---|

| Master Serial | FPGA 主动从串行 Flash 加载 |

| Slave Serial | 由外部控制器(如 CPU)发送配置数据 |

| Master SelectMAP (x8/x16) | 使用并行接口从 Flash 加载 |

| Slave SelectMAP (x8/x16/x32) | 外部主机(如 DSP/ARM)写入配置数据 |

| JTAG | 用于调试或烧录,常用于开发阶段 |

| Master SPI (x1/x2/x4) | 支持标准 SPI NOR Flash 启动 |

| Master BPI (x8/x16) | 支持并行 NOR Flash 启动,高速 |

🔘 模式选择引脚 M[2:0]

- 使用 M2、M1、M0 三个引脚的高低电平组合选择配置模式。

- 引脚应通过 ≤ 1kΩ 的上拉/下拉电阻固定电平,或直接连接 VCC/GND。

- 配置过程中不能更改模式引脚状态。

🔄 可重复编程特性

- FPGA 是非永久性配置器件,支持无限次重新配置。

- 可实现现场升级、动态重配置、多配置切换等功能。

📁 相关文档

- 官方权威参考文档:

- UG470: 7 Series FPGAs Configuration User Guide

- 包含详细配置流程、接口协议、时序要求等。

- UG470: 7 Series FPGAs Configuration User Guide

🧠 总结一句话:

Xilinx 7 系列 FPGA 是基于 SRAM 的可编程器件,每次上电都需要加载 bitstream。它支持多种配置模式,包括 JTAG、SPI、BPI 和 SelectMAP,并可通过 M[2:0] 引脚选择具体模式,适用于嵌入式系统、工业控制、通信设备等多种应用场景。

✅ 总结:AMD(Xilinx)FPGA 配置文件的生成与格式

🧩 核心内容概述

AMD(原 Xilinx)的 FPGA 设计工具(如 ISE 和 Vivado)可以将设计转换为多种格式的配置文件,用于加载或烧录到 FPGA 或非易失性存储器中。

🛠️ 主要工具和命令

| 工具 | 功能 | 命令/工具 |

|---|---|---|

| ISE | 生成比特流 | BitGen(从 NCD 文件生成 .bit 文件) |

| ISE | 生成 PROM 文件 | PROMGen(将 .bit 转换为 Flash 可用格式) |

| Vivado | 生成比特流 | write_bitstream |

| Vivado | 生成 Flash 文件 | write_cfgmem |

📁 常见配置文件格式

| 格式 | 描述 |

|---|---|

.bit |

标准比特流文件,用于直接加载到 FPGA |

.mcs |

多配置支持的 Flash 存储文件(常用于 SPI/BPI Flash) |

.bin |

二进制格式,适用于通用 Flash 编程 |

.hex |

十六进制格式,部分调试工具使用 |

.elf / .exo |

在嵌入式系统中用于软核处理器配置 |

💡 关键特点

- 不局限于 PROM:虽然叫“PROM 文件”,但这些文件也可用于 SD 卡、U盘、网络传输等。

- 多配置支持:一个文件可包含多个 bitstream,实现 FPGA 的多启动模式。

- 灵活部署:可存储在任意位置,通过任何方式加载到 FPGA。

📚 推荐文档

🧠 一句话总结:

AMD(Xilinx)FPGA 开发工具支持将设计编译为多种配置文件格式(如

.bit,.mcs),既可用于直接加载 FPGA,也可用于烧录到 Flash 或其他介质,具有高度灵活性和可扩展性。

Xilinx 的 .bit 文件格式是一种基于“键-值对”(Key-Value Pair)结构的二进制文件,用于将 FPGA 的配置数据加载到器件中。你提供的 hex dump 展示了 .bit 文件开头的部分内容,并对其字段进行了初步解析。下面我将详细解释其结构、含义和比特流的组成方式。

bit文件头结构

🔍 一、整体结构概览

.bit 文件由多个字段(Field)组成,每个字段都以一个长度 + 键 + 数据的方式组织:

[Length (2 bytes)] [Key (1 byte)] [Data (variable length)]

- Length:2 字节,大端序(Big Endian),表示该字段的数据部分长度。

- Key:1 字节,ASCII 字符,标识该字段的内容类型。

- Data:可变长度数据,根据 Key 不同而不同。

📄 二、逐字段分析

以下是 .bit 文件头部十六进制数据及解析:

00000000: 00 09 0f f0 0f f0 0f f0 0f f0 00 00 01 61 00 0a

00000010: 78 66 6f 72 6d 2e 6e 63 64 00 62 00 0c 76 31 30

00000020: 30 30 65 66 67 38 36 30 00 63 00 0b 32 30 30 31

00000030: 2f 30 38 2f 31 30 00 64 00 09 30 36 3a 35 35 3a

00000040: 30 34 00 65 00 0c 28 18 ff ff ff ff aa 99 55 66

✅ Field 1:Header Padding(可忽略)

00000000: 00 09 0f f0 0f f0 0f f0 0f f0

- Length:

0x0009= 9 字节 - Data:

0F F0 ... - 说明:可能是某种填充或保留字段,通常可以忽略。

✅ Field 2:Start of Keyed Sections(标识开始)

0000000a: 00 00 01 61

- Length:

0x0001= 1 字节 - Key:

0x61= ASCII'a' - 说明:表示第一个元数据字段开始。

✅ Field 3:Design Name(设计名称)

0000000f: 00 0a 78 66 6f 72 6d 2e 6e 63 64 00

- Length:

0x000a= 10 字节 - Key:

0x61= ASCII'a' - Value:

"xform.ncd"+ null (0x00) - 说明:这是设计的名字,通常来自 ISE 工具中的 NCD 文件名。

✅ Field 4:Part Name(器件型号)

0000001a: 62 00 0c 76 31 30 30 30 65 66 67 38 36 30 00

- Key:

0x62= ASCII'b' - Length:

0x000c= 12 字节 - Value:

"v1000efg860"+ null (0x00) - 说明:目标 FPGA 器件型号,例如 Virtex-4 或其他系列。

✅ Field 5:Date(日期)

0000002a: 63 00 0b 32 30 30 31 2f 30 38 2f 31 30 00

- Key:

0x63= ASCII'c' - Length:

0x000b= 11 字节 - Value:

"2001/08/10"+ null (0x00) - 说明:生成 bitstream 的日期。

✅ Field 6:Time(时间)

0000003a: 64 00 09 30 36 3a 35 35 3a 30 34 00

- Key:

0x64= ASCII'd' - Length:

0x0009= 9 字节 - Value:

"06:55:04"+ null (0x00) - 说明:生成 bitstream 的时间。

✅ Field 7:Bitstream Data(真正的比特流数据)

0000004a: 65 00 0c 28 18 ff ff ff ff aa 99 55 66 ...

- Key:

0x65= ASCII'e' - Length:

0x000c9090= 8,233,440 字节(取决于器件大小) - 数据起始标志:

FF FF FF FF AA 99 55 66AA995566是同步字(Sync Word),标志着 bitstream 数据的正式开始。

- 说明:这部分才是 FPGA 实际需要加载的配置数据。

示例:

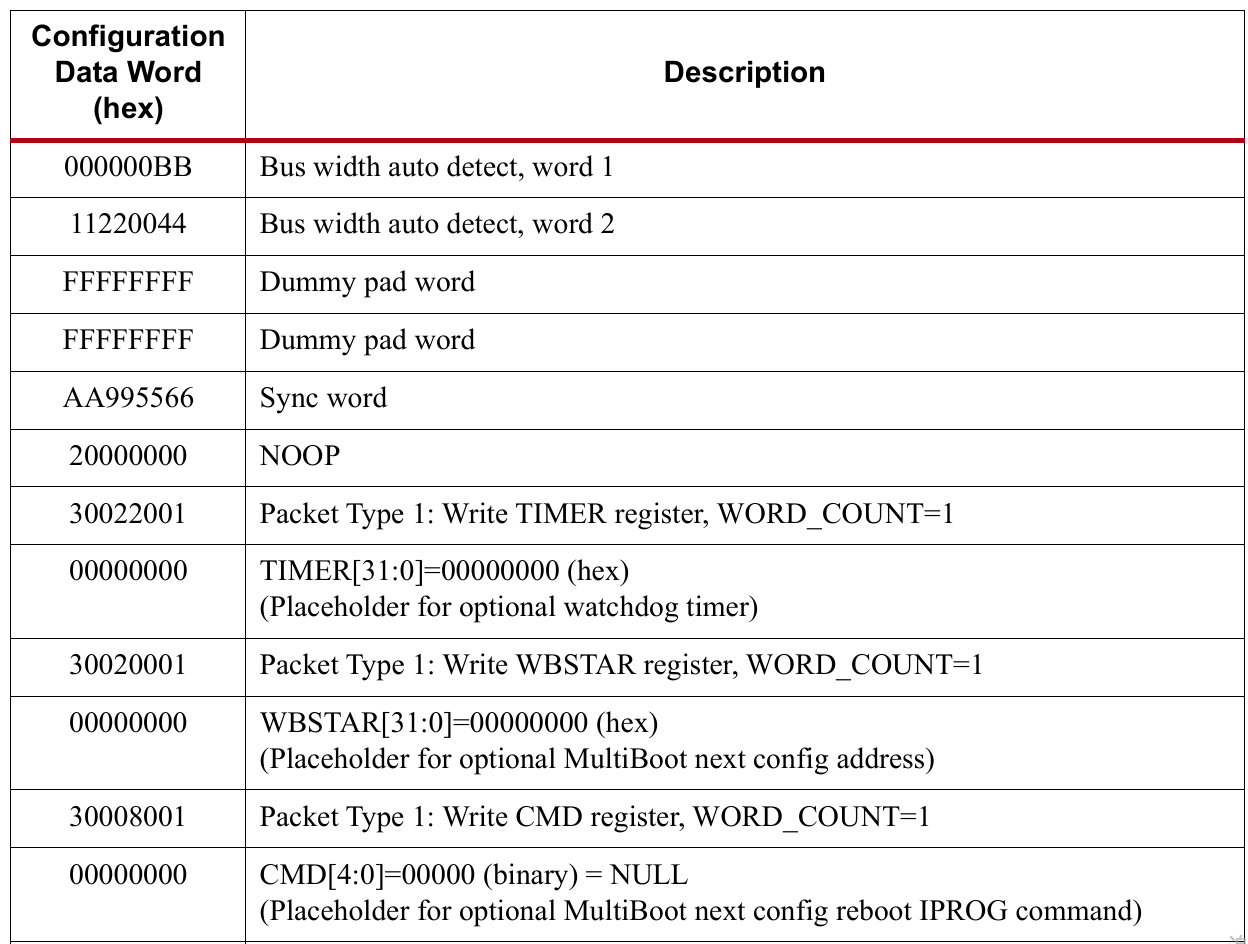

Bitstream 配置数据结构

-

Padding(填充数据)

- 作用:用于分隔存储在非易失性内存中的多个 bitstream。

- 特性:通常为全0或全1序列,FPGA配置控制器会忽略这部分数据。使用全1填充较为常见,因为Flash擦除后的状态也是全1。

-

Sync Word(同步字)

- 值:

0xAA995566 - 作用:通知FPGA配置控制器开始处理后续的bitstream数据。

- 值:

-

Desync Word(去同步字)

- 作用:指示bitstream的结束位置。遇到去同步字后,配置控制器会忽略所有后续的bitstream数据直到下一个同步字出现。

-

Commands(命令)

- 用途:用于读写FPGA配置控制器寄存器。

- 示例:

- ID-CODE:识别bitstream对应的FPGA设备。

- FAR (Frame Address Register):指定要配置的帧地址。

- FDRI (Frame Data Register Input):写入帧数据。

- NOOP:无操作命令,被配置控制器忽略。

-

Memory Frames(内存帧)

- 定义:是Xilinx FPGA配置的基本单位。

- 大小:取决于具体的FPGA系列;例如,Virtex-6系列中每个帧大小为2592位。

- 用途:用于配置多个逻辑切片、IO、BRAM等FPGA组件。每个帧都有一个与FPGA配置空间相对应的地址。Bitstream通过一系列FAR和FDRI命令来配置这些帧。

我们具体来看一下

配置内存以帧(Frame)为单位组织:

每个帧是配置内存中最小可寻址单元。

每个帧包含 101 个 32 位字(words),即:

101×32=3232 bits

📌 所有配置操作必须作用于完整的帧:

不能对帧的一部分进行写入或读取。

帧地址通过 FAR(Frame Address Register) 设置。

更详细的指令定义解释可以参考UG470

浙公网安备 33010602011771号

浙公网安备 33010602011771号