SOC中的DFT和BIST对比与比较-IC学习笔记(二)

ATE:ATE是Automatic Test Equipment的缩写,根据客户的测试要求、图纸及参考方案,采用MCU、PLC、PC基于VB、VC开发平台,利用TestStand&LabVIEW和JTAG/Boundary Scan等技术开发、设计各类自动化测试设备。

BIST:BIST是在设计时在电路中植入相关功能电路用于提供自我测试功能的技术,以此降低器件测试对自动测试设备(ATE)的依赖程度。BIST技术的快速发展很大的原因是由于居高不下的ATE成本和电路的高复杂度。现在,高度集成的电路被广泛应用,测试这些电路需要高速的混合信号测试设备。BIST技术可以通过实现自我测试从而减少对ATE的需求。

优点:

1, 降低测试成本

2, 提高错误覆盖率

3, 缩短测试所需时间

4, 方便客户服务

5, 独立测试的能力

缺点:

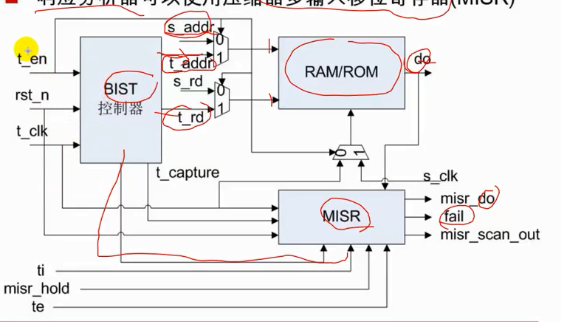

![]() 测试向量通过RAM/ROM产生结果与分析器输入结果进行对比,比较过程在MISR中进行。

测试向量通过RAM/ROM产生结果与分析器输入结果进行对比,比较过程在MISR中进行。

@作者:高建新

链接:https://www.zhihu.com/question/50626097/answer/152109180

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

1, 额外的电路占用宝贵面积

2, 额外的引脚

3, 可能存在的测试盲点

BIST技术大致可以分两类: Logic BIST(LBIST) 和 Memory BIST (MBIST)

MBIST只用于存储器测试,典型的MBIST包含测试电路用于加载,读取和比较测试图形。目前存在几种业界通用的MBIST算法,比如“March”算法,Checkerboard算法等等。

另一种比较少见的BIST称为Array BIST,它是MBIST的一种,专门用于嵌入式存储器的自我测试。Analog BIST则用于模拟电路的自我测试。

基于各种算法生成多种测试向量,每种有不同针对的电路错误类型。

测试向量通过RAM/ROM产生结果与分析器输入结果进行对比,比较过程在MISR中进行。

测试向量通过RAM/ROM产生结果与分析器输入结果进行对比,比较过程在MISR中进行。 在芯片测试中scan和bist有什么区别?

bist是内建自测试,一般有rambist、flashbist等,它是内部集成专门测试算法,同时还包括测试控制电路,输出结果比较等电路,它是芯片中实际电路;scan是一种结构性测试,它将芯片内部的寄存器替换成专门的寄存器,然后连接成1条链或多条,这种方式只需要在输入端输入pattern,在输出端对比输出即可,它不care芯片功能,可以节省很多测试case开发时间,同时也减少测试时间

@作者:高建新

链接:https://www.zhihu.com/question/50626097/answer/152109180

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

DFT,即可测试性设计(Design for Testability, DFT)是一种集成电路设计技术,它将一些特殊结构在设计阶段植入电路,以便设计完成后进行测试。电路测试有时并不容易,这是因为电路的许多内部节点信号在外部难以控制和观测。通过添加可测试性设计结构,例如扫描链等,内部信号可以暴露给电路外部。

浙公网安备 33010602011771号

浙公网安备 33010602011771号