libero verilog crc16-CCITT

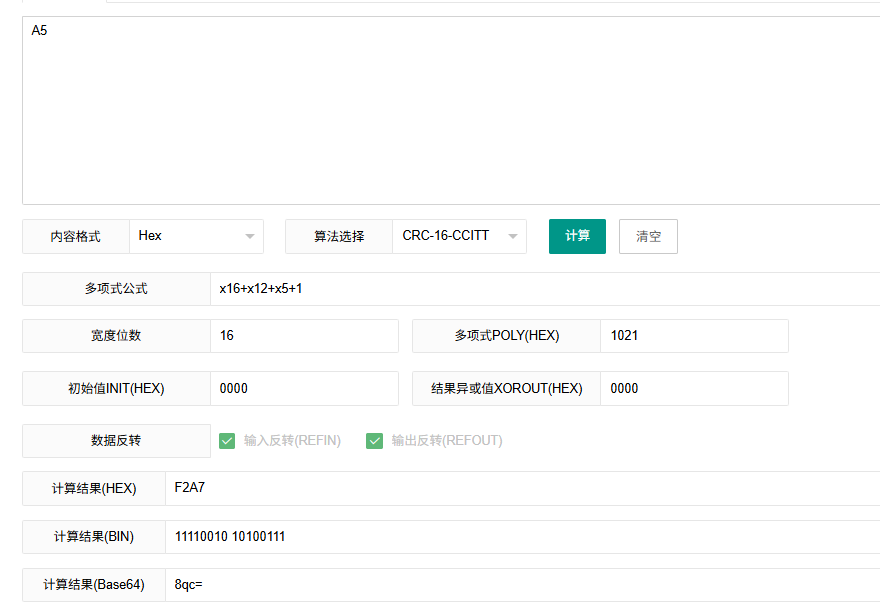

1、在线计算 0xA5 得出 0xF2A7

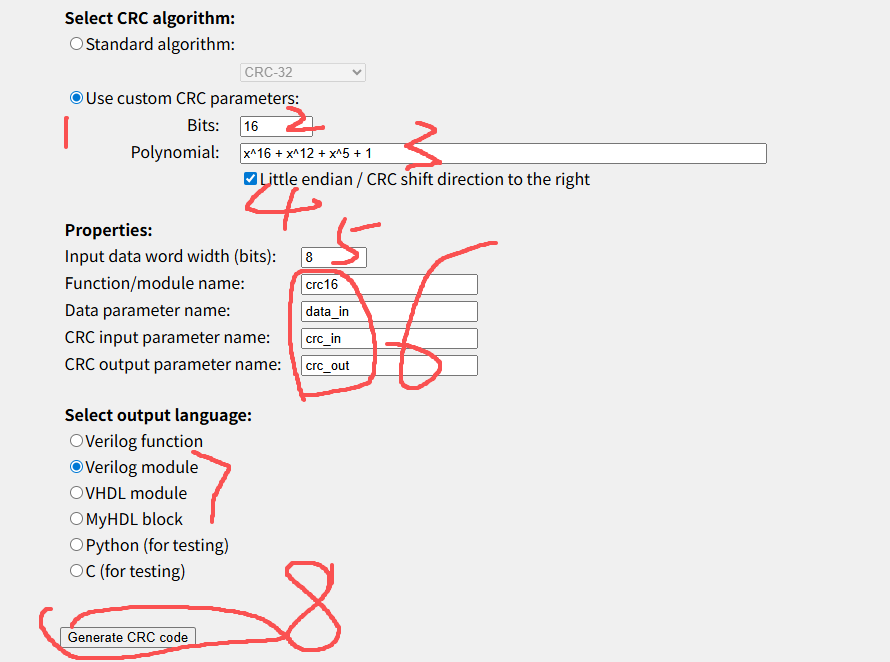

2、在线 生成 verilog code Generator for CRC HDL code, 参数配置如下:

// vim: ts=4 sw=4 expandtab // THIS IS GENERATED VERILOG CODE. // https://bues.ch/h/crcgen // // This code is Public Domain. // Permission to use, copy, modify, and/or distribute this software for any // purpose with or without fee is hereby granted. // // THE SOFTWARE IS PROVIDED "AS IS" AND THE AUTHOR DISCLAIMS ALL WARRANTIES // WITH REGARD TO THIS SOFTWARE INCLUDING ALL IMPLIED WARRANTIES OF // MERCHANTABILITY AND FITNESS. IN NO EVENT SHALL THE AUTHOR BE LIABLE FOR ANY // SPECIAL, DIRECT, INDIRECT, OR CONSEQUENTIAL DAMAGES OR ANY DAMAGES WHATSOEVER // RESULTING FROM LOSS OF USE, DATA OR PROFITS, WHETHER IN AN ACTION OF CONTRACT, // NEGLIGENCE OR OTHER TORTIOUS ACTION, ARISING OUT OF OR IN CONNECTION WITH THE // USE OR PERFORMANCE OF THIS SOFTWARE. `ifndef CRC16_V_ `define CRC16_V_ // CRC polynomial coefficients: x^16 + x^12 + x^5 + 1 // 0x8408 (hex) // CRC width: 16 bits // CRC shift direction: right (little endian) // Input word width: 8 bits module crc16 ( input [15:0] crc_in, input [7:0] data_in, output [15:0] crc_out ); assign crc_out[0] = crc_in[0] ^ crc_in[4] ^ crc_in[8] ^ data_in[0] ^ data_in[4]; assign crc_out[1] = crc_in[1] ^ crc_in[5] ^ crc_in[9] ^ data_in[1] ^ data_in[5]; assign crc_out[2] = crc_in[2] ^ crc_in[6] ^ crc_in[10] ^ data_in[2] ^ data_in[6]; assign crc_out[3] = crc_in[0] ^ crc_in[3] ^ crc_in[7] ^ crc_in[11] ^ data_in[0] ^ data_in[3] ^ data_in[7]; assign crc_out[4] = crc_in[1] ^ crc_in[12] ^ data_in[1]; assign crc_out[5] = crc_in[2] ^ crc_in[13] ^ data_in[2]; assign crc_out[6] = crc_in[3] ^ crc_in[14] ^ data_in[3]; assign crc_out[7] = crc_in[0] ^ crc_in[4] ^ crc_in[15] ^ data_in[0] ^ data_in[4]; assign crc_out[8] = crc_in[0] ^ crc_in[1] ^ crc_in[5] ^ data_in[0] ^ data_in[1] ^ data_in[5]; assign crc_out[9] = crc_in[1] ^ crc_in[2] ^ crc_in[6] ^ data_in[1] ^ data_in[2] ^ data_in[6]; assign crc_out[10] = crc_in[2] ^ crc_in[3] ^ crc_in[7] ^ data_in[2] ^ data_in[3] ^ data_in[7]; assign crc_out[11] = crc_in[3] ^ data_in[3]; assign crc_out[12] = crc_in[0] ^ crc_in[4] ^ data_in[0] ^ data_in[4]; assign crc_out[13] = crc_in[1] ^ crc_in[5] ^ data_in[1] ^ data_in[5]; assign crc_out[14] = crc_in[2] ^ crc_in[6] ^ data_in[2] ^ data_in[6]; assign crc_out[15] = crc_in[3] ^ crc_in[7] ^ data_in[3] ^ data_in[7]; endmodule `endif // CRC16_V_

测试文件:

wire [15:0] crc_value;

crc16 crc16_0

(

// Inputs

.crc_in(16'h0000),

.data_in(8'hA5),

// Outputs

.crc_out(crc_value)

);

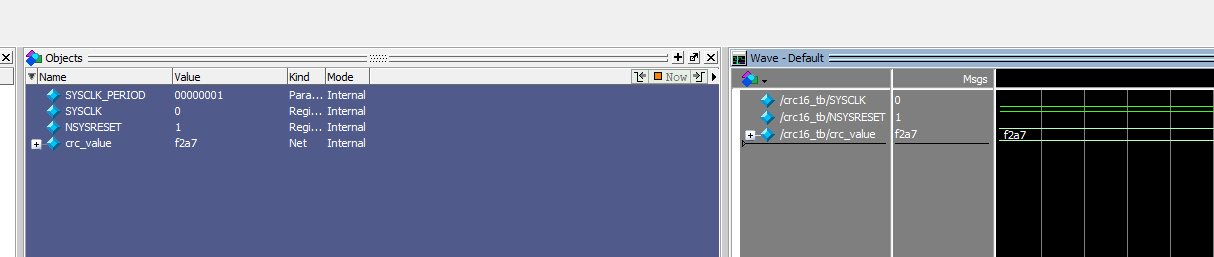

仿真结果 和 在线测试一致

浙公网安备 33010602011771号

浙公网安备 33010602011771号