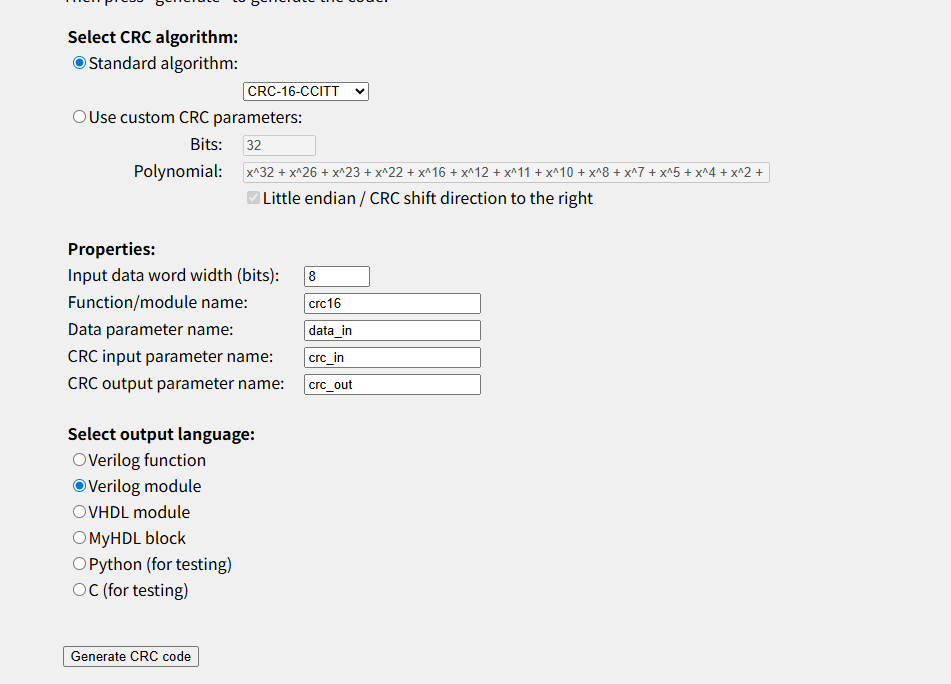

libero verilog crc16-CCITT-FALSE

// vim: ts=4 sw=4 expandtab // THIS IS GENERATED VERILOG CODE. // https://bues.ch/h/crcgen // // This code is Public Domain. // Permission to use, copy, modify, and/or distribute this software for any // purpose with or without fee is hereby granted. // // THE SOFTWARE IS PROVIDED "AS IS" AND THE AUTHOR DISCLAIMS ALL WARRANTIES // WITH REGARD TO THIS SOFTWARE INCLUDING ALL IMPLIED WARRANTIES OF // MERCHANTABILITY AND FITNESS. IN NO EVENT SHALL THE AUTHOR BE LIABLE FOR ANY // SPECIAL, DIRECT, INDIRECT, OR CONSEQUENTIAL DAMAGES OR ANY DAMAGES WHATSOEVER // RESULTING FROM LOSS OF USE, DATA OR PROFITS, WHETHER IN AN ACTION OF CONTRACT, // NEGLIGENCE OR OTHER TORTIOUS ACTION, ARISING OUT OF OR IN CONNECTION WITH THE // USE OR PERFORMANCE OF THIS SOFTWARE. `ifndef CRC16_V_ `define CRC16_V_ // CRC polynomial coefficients: x^16 + x^12 + x^5 + 1 // 0x1021 (hex) // CRC width: 16 bits // CRC shift direction: left (big endian) // Input word width: 8 bits module crc16 ( input [15:0] crc_in, input [7:0] data_in, output [15:0] crc_out ); assign crc_out[0] = crc_in[8] ^ crc_in[12] ^ data_in[0] ^ data_in[4]; assign crc_out[1] = crc_in[9] ^ crc_in[13] ^ data_in[1] ^ data_in[5]; assign crc_out[2] = crc_in[10] ^ crc_in[14] ^ data_in[2] ^ data_in[6]; assign crc_out[3] = crc_in[11] ^ crc_in[15] ^ data_in[3] ^ data_in[7]; assign crc_out[4] = crc_in[12] ^ data_in[4]; assign crc_out[5] = crc_in[8] ^ crc_in[12] ^ crc_in[13] ^ data_in[0] ^ data_in[4] ^ data_in[5]; assign crc_out[6] = crc_in[9] ^ crc_in[13] ^ crc_in[14] ^ data_in[1] ^ data_in[5] ^ data_in[6]; assign crc_out[7] = crc_in[10] ^ crc_in[14] ^ crc_in[15] ^ data_in[2] ^ data_in[6] ^ data_in[7]; assign crc_out[8] = crc_in[0] ^ crc_in[11] ^ crc_in[15] ^ data_in[3] ^ data_in[7]; assign crc_out[9] = crc_in[1] ^ crc_in[12] ^ data_in[4]; assign crc_out[10] = crc_in[2] ^ crc_in[13] ^ data_in[5]; assign crc_out[11] = crc_in[3] ^ crc_in[14] ^ data_in[6]; assign crc_out[12] = crc_in[4] ^ crc_in[8] ^ crc_in[12] ^ crc_in[15] ^ data_in[0] ^ data_in[4] ^ data_in[7]; assign crc_out[13] = crc_in[5] ^ crc_in[9] ^ crc_in[13] ^ data_in[1] ^ data_in[5]; assign crc_out[14] = crc_in[6] ^ crc_in[10] ^ crc_in[14] ^ data_in[2] ^ data_in[6]; assign crc_out[15] = crc_in[7] ^ crc_in[11] ^ crc_in[15] ^ data_in[3] ^ data_in[7]; endmodule `endif // CRC16_V_

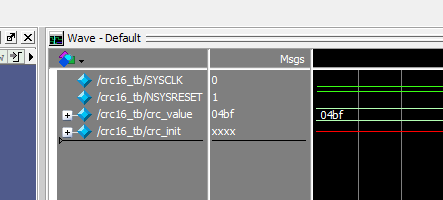

测试文件

////////////////////////////////////////////////////////////////////// // Created by Microsemi SmartDesign Wed Jan 28 10:31:43 2026 // Testbench Template // This is a basic testbench that instantiates your design with basic // clock and reset pins connected. If your design has special // clock/reset or testbench driver requirements then you should // copy this file and modify it. ////////////////////////////////////////////////////////////////////// /////////////////////////////////////////////////////////////////////////////////////////////////// // Company: <Name> // // File: crc16_tb.v // File history: // <Revision number>: <Date>: <Comments> // <Revision number>: <Date>: <Comments> // <Revision number>: <Date>: <Comments> // // Description: // // <Description here> // // Targeted device: <Family::ProASIC3> <Die::A3P250> <Package::100 VQFP> // Author: <Name> // /////////////////////////////////////////////////////////////////////////////////////////////////// `timescale 1ns/100ps module crc16_tb; parameter SYSCLK_PERIOD = 1;// 1000MHZ reg SYSCLK; reg NSYSRESET; initial begin SYSCLK = 1'b0; NSYSRESET = 1'b0; end ////////////////////////////////////////////////////////////////////// // Reset Pulse ////////////////////////////////////////////////////////////////////// initial begin #(SYSCLK_PERIOD * 10 ) NSYSRESET = 1'b1; end ////////////////////////////////////////////////////////////////////// // Clock Driver ////////////////////////////////////////////////////////////////////// always @(SYSCLK) #(SYSCLK_PERIOD / 2.0) SYSCLK <= !SYSCLK; ////////////////////////////////////////////////////////////////////// // Instantiate Unit Under Test: crc16 ////////////////////////////////////////////////////////////////////// wire [15:0] crc_value; reg [15:0] crc_init; crc16 crc16_0 ( // Inputs .crc_in(16'hFFFF), .data_in(8'hA5), // Outputs .crc_out(crc_value) ); initial begin end endmodule

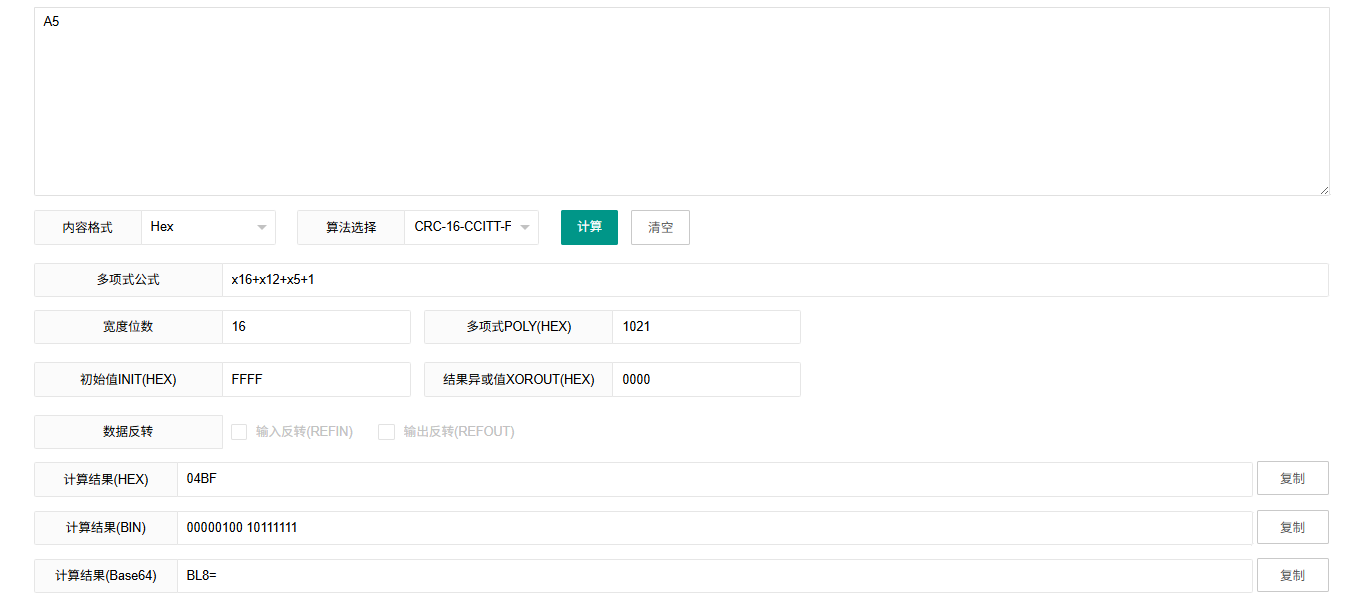

CRC-16-CCITT 生成 的 verilog 和 网页上 CRC-16-CCITT-FALSE 计算的结果一致!

浙公网安备 33010602011771号

浙公网安备 33010602011771号