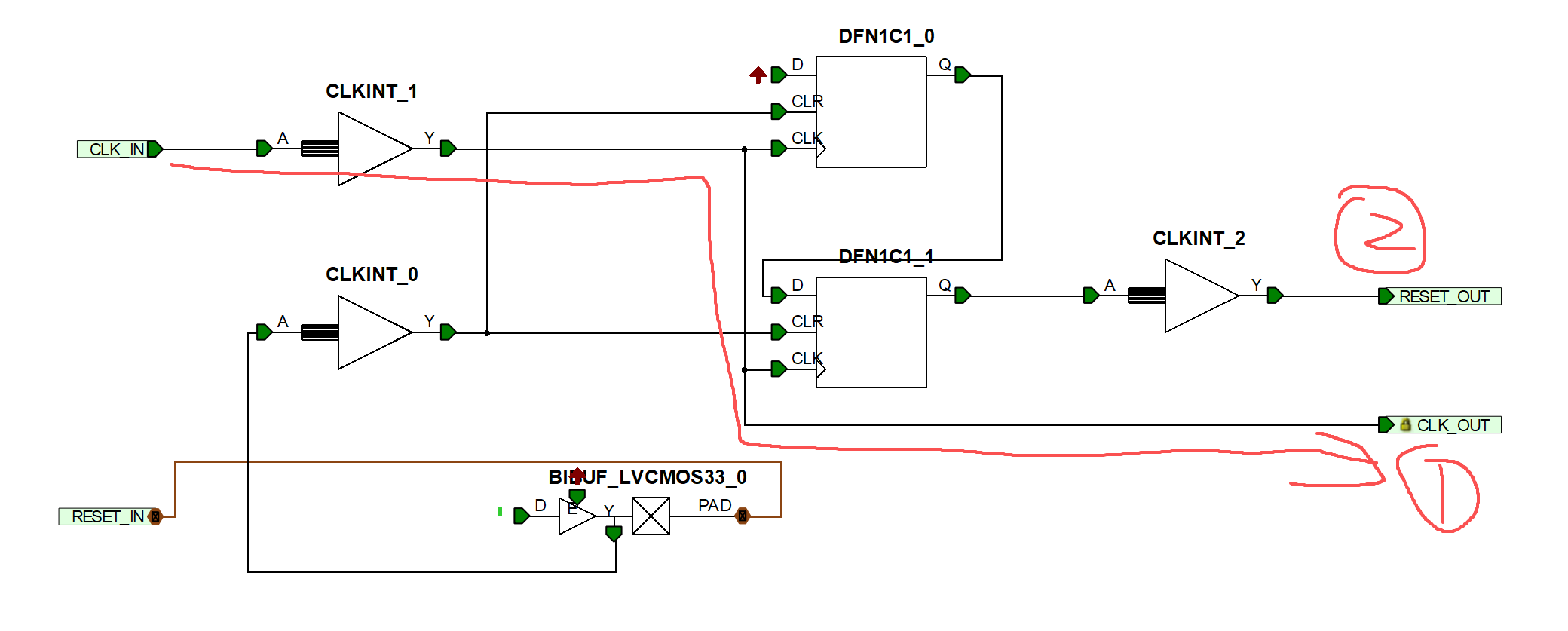

libero ProASIC3 A3P250 逻辑不正常

使用 双端口 RAM , 作为缓冲 , 实现 串口 回环时 , 发现 数据 可能 出错 , 经过查找 ,原因是 时钟 没有经过 CLKINT 强化 !

1、引脚 进来的时钟 没有使用 CLKINT 变成 全局时钟!

内置上电复位 电路设计, 输出 复位信号 和 时钟信号 , 使用 CLKINT 增强驱动能力!可以解决问题, 最终解决问题, 有源晶振信号 不能驱动 模块 ,应该 晶振输入信号 接入到 PLL 时钟信号输出 !

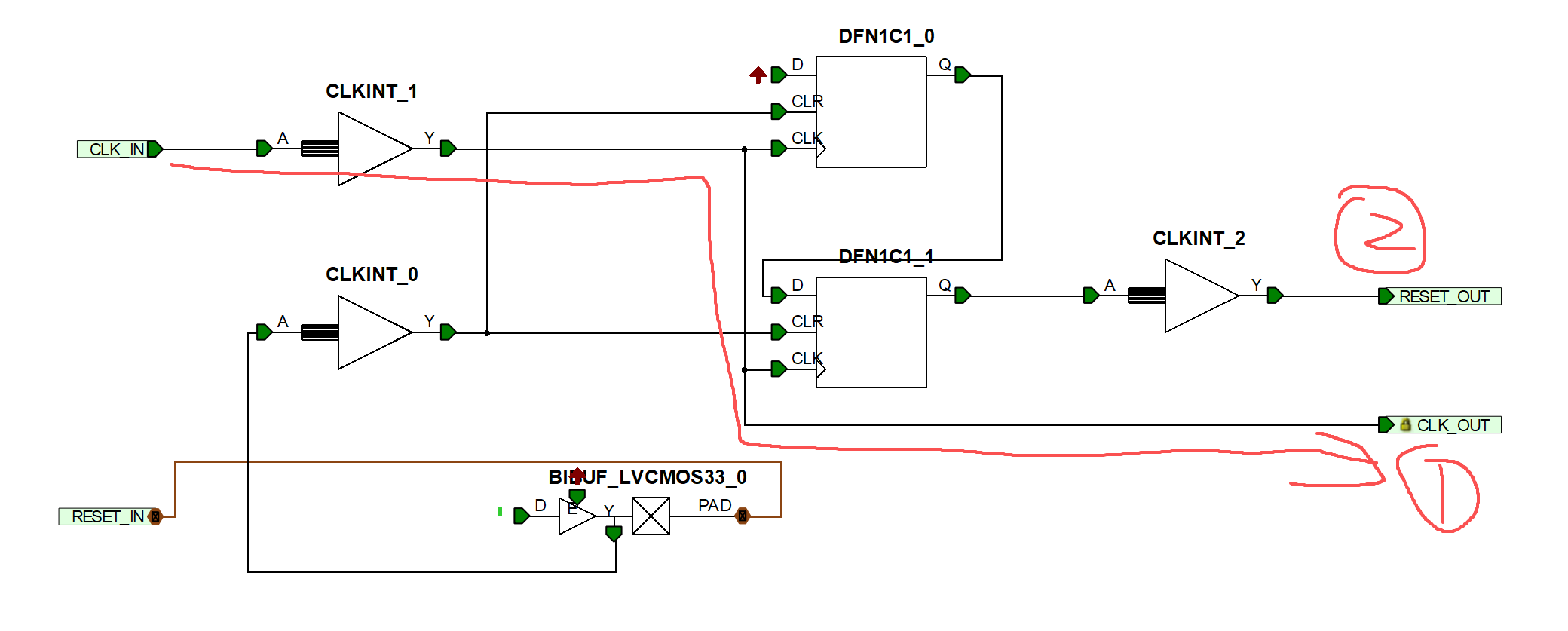

使用 双端口 RAM , 作为缓冲 , 实现 串口 回环时 , 发现 数据 可能 出错 , 经过查找 ,原因是 时钟 没有经过 CLKINT 强化 !

1、引脚 进来的时钟 没有使用 CLKINT 变成 全局时钟!

内置上电复位 电路设计, 输出 复位信号 和 时钟信号 , 使用 CLKINT 增强驱动能力!可以解决问题, 最终解决问题, 有源晶振信号 不能驱动 模块 ,应该 晶振输入信号 接入到 PLL 时钟信号输出 !