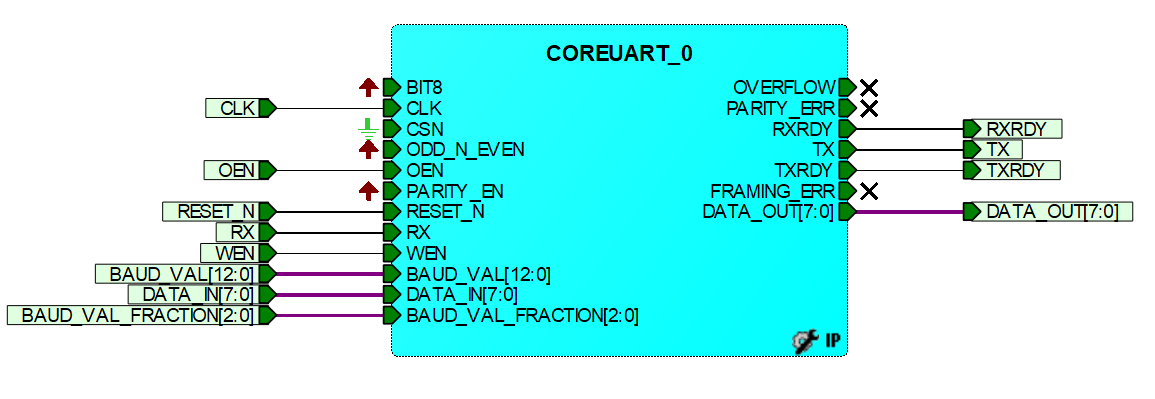

Libero MicroChip CoreUART v5.7 使用

官方参考手册, 2025年12月25日 V5.7.100

中文翻译

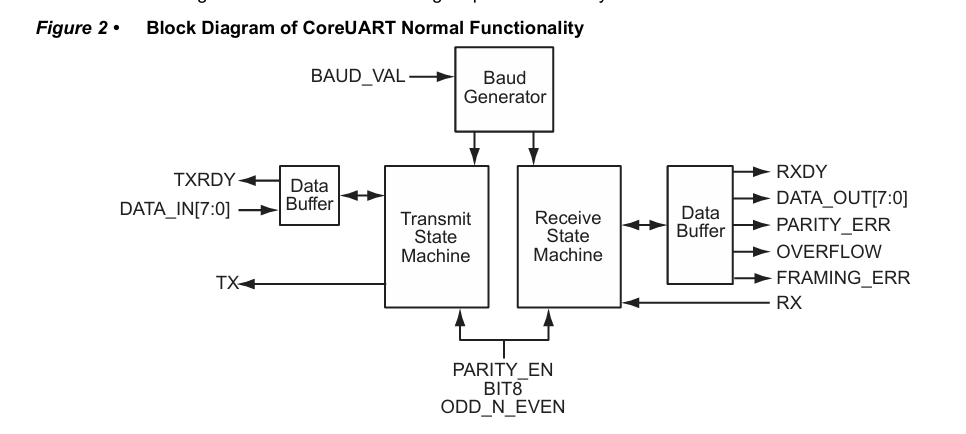

功能框图:

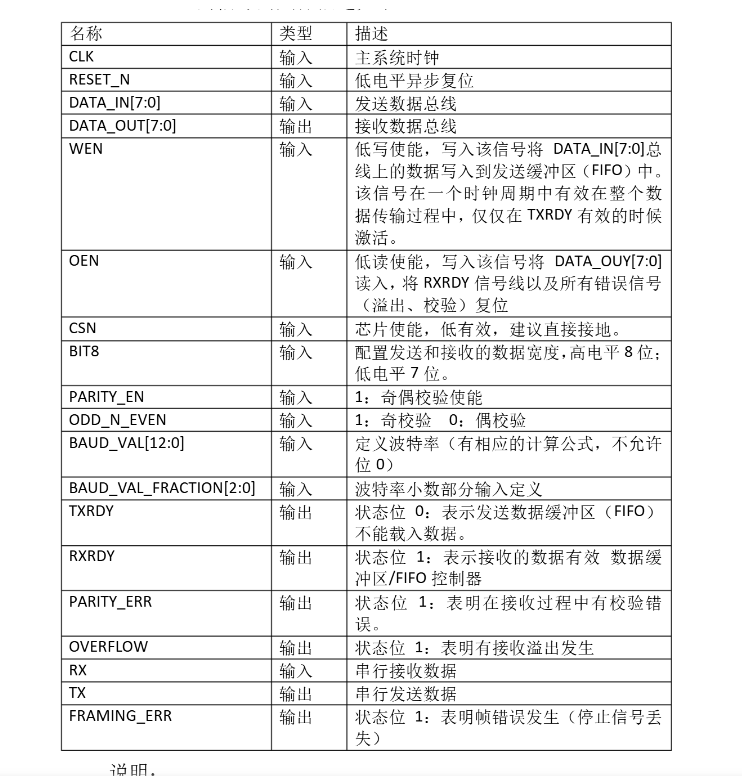

模块 配置 : 没有使用 FIFO , 启用 高精度 波特率计算

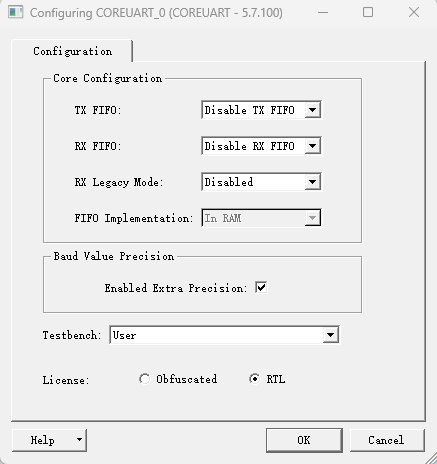

smartDesign 参数配置 , 数据长度是8位,因此拉高, 模块一直工作所以 CSN 拉低, 选择奇校验, 因此 ODD_N_EVEN 和 PARITY_EN 拉高!

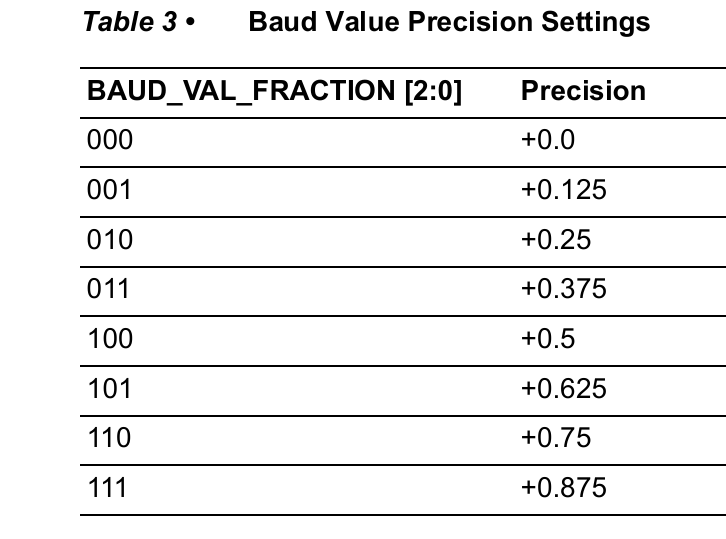

波特率计算 : 因为 enable extra precision 使能, 则 输入参数 有 三个 影响波特率, 分别是 BAUD_VAL,BAUD_VAL_FRACTION, CLK

计算公式: 波特率 = CLK / ( BAUD_VAL + BAUD_VAL_FRACTION / 8 + 1 ) *16

假如 输入时钟 是 40Mhz , 波特率 是 115200 , 则 :

// 115200 = 40MHz / ( BAUD_VAL + BAUD_VAL_FRACTION / 8 + 1 ) *16

// 解得 BAUD_VAL = 20 , BAUD_VAL_FRACTION = 6

// 波特率 误差 40MHz / 21.75*16 = 114942.53 , 误差 约 0.22%

文档里 有 关于 BAUD_VAL_FRACTION 的值 对应表

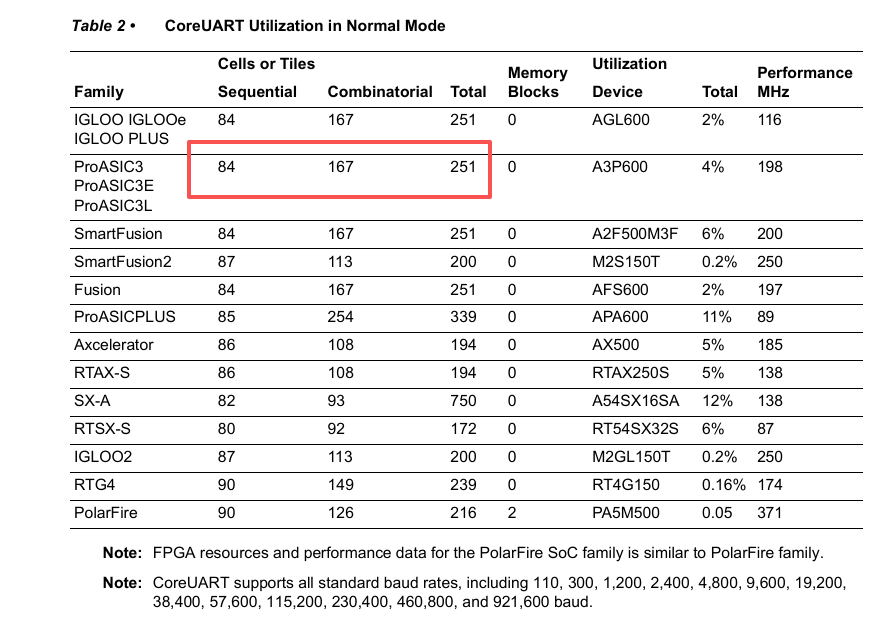

该 IP 资源占用情况:

数据回环 测试 verilog code :

///////////////////////////////////////////////////////////////////////////////////////////////////// Company: <Name>

// // File: uart_process.v // File history: // <Revision number>: <Date>: <Comments> // <Revision number>: <Date>: <Comments> // <Revision number>: <Date>: <Comments> // // Description: // // <Description here> // // Targeted device: <Family::ProASIC3> <Die::A3P250> <Package::100 VQFP> // Author: <Name> // /////////////////////////////////////////////////////////////////////////////////////////////////// //`timescale <time_units> / <precision> module uart_process( input clk_40mhz, input rst_n, input uart_rx, output uart_tx ); wire [7:0] rx_data; wire [7:0] tx_data; reg [7:0] tx_data_reg; assign tx_data = tx_data_reg; reg rx_oen_reg; reg tx_wen_reg; wire rx_ready; wire tx_ready; // 例化 uart 模块 uart uart_0_inst ( // Inputs // 波特率计算 // 使能 波特率 精细计算 enable extra precision // 115200 = 40MHz / ( BAUD_VAL + BAUD_VAL_FRACTION / 8 + 1 ) *16 // 解得 BAUD_VAL = 20 , BAUD_VAL_FRACTION = 6 // 波特率 误差 40MHz / 21.75*16 = 114942.53 , 误差 约 0.22% .BAUD_VAL(20), .BAUD_VAL_FRACTION(6), .CLK(clk_40mhz), .DATA_IN(tx_data), // 输入数据总线 位宽 [7:0] .OEN(rx_oen_reg), // 低电平将 DATA_OUT 读入, 将 RXRDY 和 所有错误复位 ,溢出和校验错误 .RESET_N(rst_n), .RX(uart_rx), .WEN(tx_wen_reg), // 低电平将 DATA_IN 写入 TX FIFO, 当 TXRDY 为高时可写入 // Outputs .DATA_OUT(rx_data), // 输出数据总线 位宽 [7:0] .RXRDY(rx_ready), // 0= RX FIFO 空, 1= 可读取 .TX(uart_tx), .TXRDY(tx_ready) // 0= TX FIFO 满, 1= 可写入 ); // 检测 串口是否有数据// 将数据写入发送寄存器,并 置发送使能

// 检测数据是否发送完毕,发送完成回到 空闲状态

reg [1:0] rx_state; parameter RX_IDLE = 2'd0; parameter TX_DATA = 2'd1; parameter TX_WAIT = 2'd2; always @(posedge clk_40mhz or negedge rst_n) begin if (!rst_n) begin rx_state <= RX_IDLE; rx_oen_reg <= 1'b1; // 高电平 不读数据 tx_wen_reg <= 1'b1; // 高电平 不写数据 end else if(rx_state==RX_IDLE)begin if(rx_ready)begin rx_state <= TX_DATA; tx_data_reg <= rx_data; // 将接收数据 写入 发送寄存器 rx_oen_reg <= 1'b0; // 清除 rx_ready 标志 tx_wen_reg <= 1'b0; // 写使能, 发送数据 end else begin rx_state <= RX_IDLE; end end else if(rx_state==TX_DATA)begin rx_oen_reg <= 1'b1; // 恢复 高电平 tx_wen_reg <= 1'b1; // 恢复 高电平 rx_state <= TX_WAIT; // 等待 发送完成 end else if(rx_state==TX_WAIT)begin if(tx_ready==1'b0)begin rx_state <= TX_WAIT; //这里可以添加 发送超时 处理 end else begin rx_state <= RX_IDLE; end end end endmodule

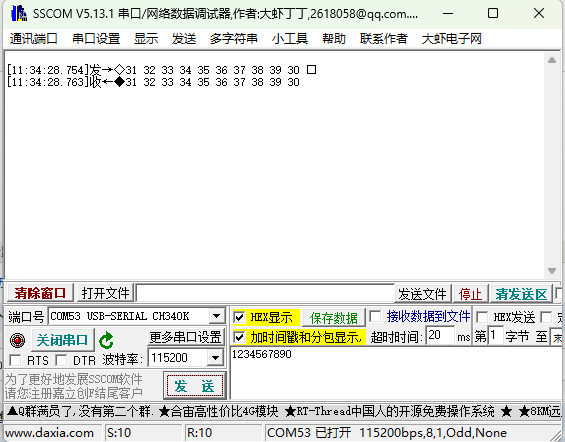

上位机工具打开奇校验(Odd ),测试结果 :

浙公网安备 33010602011771号

浙公网安备 33010602011771号