PolarFire® SoC MSS Configurator DDR 地址映射

硬件: PolarFire SoC Icicle Kit | Microchip Technology

- 5-core RISC-V CPU (1× E51, 4× U54)

- Low-power PolarFire FPGA fabric

- 4× 12.7 Gbps SERDES, PCIe Gen2, 2× GbE

- 2 GB LPDDR4, 8 GB eMMC, SD, SPI flash

- RPi header, mikroBUS™, UART/SPI/I²C/CAN

- 2 MB L2 cache or 1.875 MB LIM with ECC

- 128 KB eNVM

- RV64IMAC, 625 MHz, 16 KB L1 iCache or 8 KB ITIM, and 8 KB DTIM

- RV64GC, 625 MHz, 32 KB L1 iCache or 28 KB ITIM. 32 KB dCache

- PolarFire SoC MSS Technical Reference Manual 可以看 第十章节 “MSS Memory Map”

环境:Libero 2025.1 和 SoftConsole v2021.1

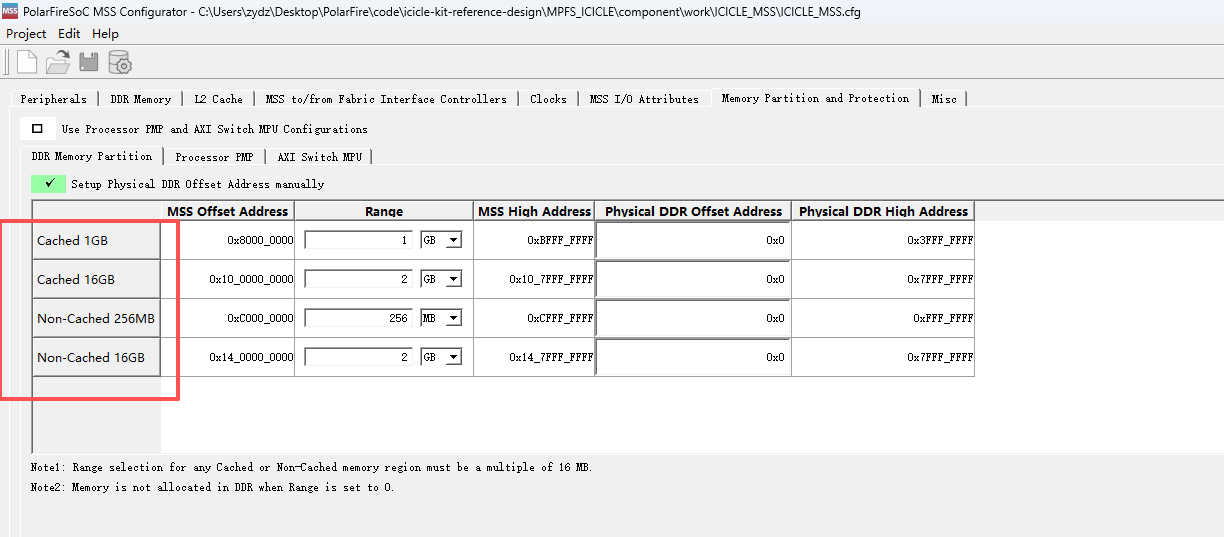

这四种地址映射什么意思?

- Cached 1GB 32位地址访问, 看宏定义,是按照地址区分?

- Cached 16GB 64位地址访问

- Non-Cached 256MB 32位地址访问

- Non-Cached 16GB 64位地址访问

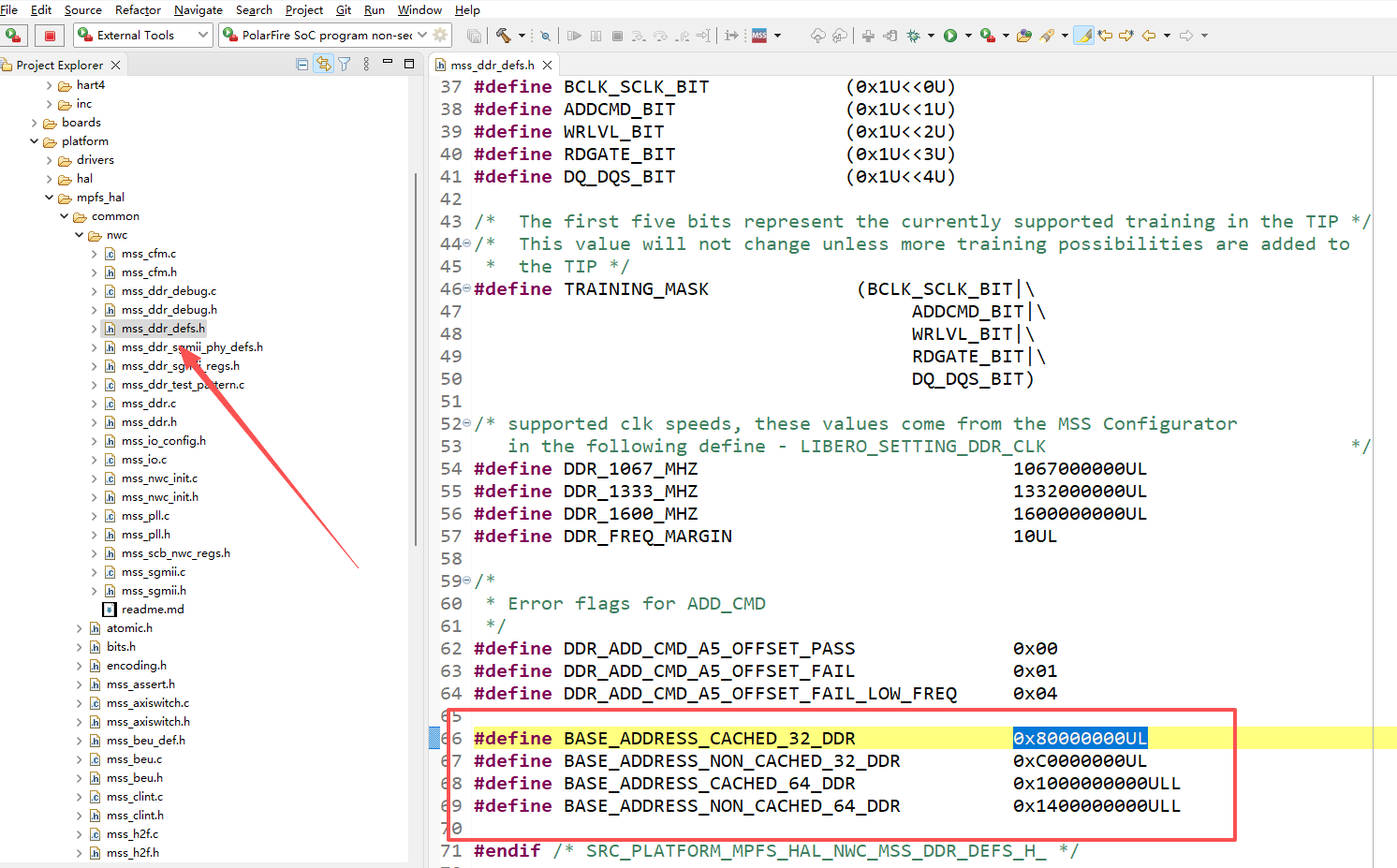

// @file mss_ddr_defs.h #define BASE_ADDRESS_CACHED_32_DDR 0x80000000UL #define BASE_ADDRESS_NON_CACHED_32_DDR 0xC0000000UL #define BASE_ADDRESS_CACHED_64_DDR 0x1000000000ULL #define BASE_ADDRESS_NON_CACHED_64_DDR 0x1400000000ULL

浙公网安备 33010602011771号

浙公网安备 33010602011771号