PolarFire® SoC mpfs-mmuart-interrupt 2 GB LPDDR4 测试日志

硬件: PolarFire SoC Icicle Kit | Microchip Technology

- 5-core RISC-V CPU (1× E51, 4× U54)

- Low-power PolarFire FPGA fabric

- 4× 12.7 Gbps SERDES, PCIe Gen2, 2× GbE

- 2 GB LPDDR4, 8 GB eMMC, SD, SPI flash

- RPi header, mikroBUS™, UART/SPI/I²C/CAN

- 2 MB L2 cache or 1.875 MB LIM with ECC

- 128 KB eNVM

- RV64IMAC, 625 MHz, 16 KB L1 iCache or 8 KB ITIM, and 8 KB DTIM

- RV64GC, 625 MHz, 32 KB L1 iCache or 28 KB ITIM. 32 KB dCache

- PolarFire SoC MSS Technical Reference Manual 可以看 第十章节 “MSS Memory Map”

软件:mpfs-mmuart-interrupt

环境:Libero 2025.1 和 SoftConsole v2021.1

1、工程激活为 LIM-Debug-IcicleKit , 打开对应配置文件

因此打开对应配置文件 : /mpfs-mmuart-interrupt/src/boards/icicle-kit/platform_config/lim-debug/mpfs_hal_config/mss_sw_config.h

如何对应:PolarFire® SoC mpfs-mmuart-interrupt demo 运行记录 - 所长 - 博客园

- #define DEBUG_DDR_INIT, 打开 DDR 测试日志,输出到串口1

- #define IMAGE_LOADED_BY_BOOTLOADER 0 , 此宏设定为0, 则在 main_first_hart 函数中 会调用 mss_nwc_init_ddr 函数

- mss_nwc_init_ddr 函数 会进行 DDR 初始化和测试, 测试会耗时 5秒的时间,这也是 为什么需要 5秒后 跳到 e51() 函数运行;

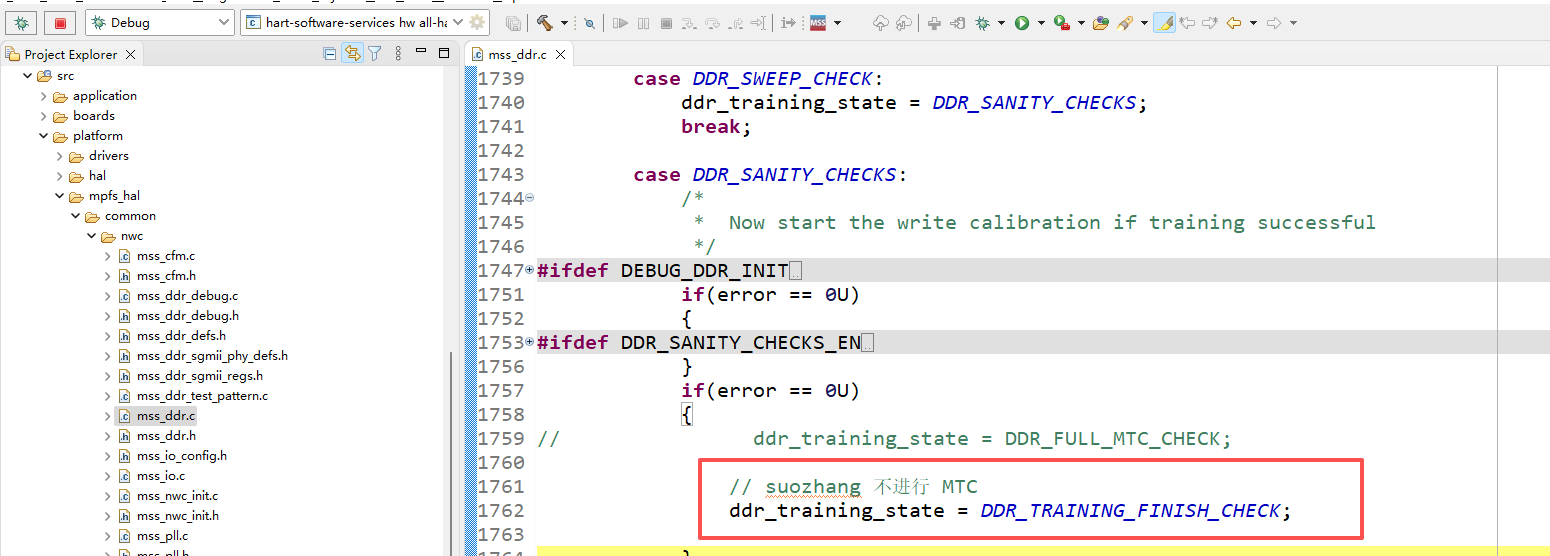

DDR初始化时,不进行测试的方法:

- DDR 初始化是状态机运行,因此 完整性检查(DDR_SANITY_CHECKS)执行里将状态改为 DDR_TRAINING_FINISH_CHECK 即可

- 这样 DDR 初始化完成 不进行MTC 以及以后 的测试,跳出初始化;

2、DDR Setup 总体流程

ddr_setup() 是一个状态机,按顺序执行以下步骤:

1. 初始化阶段(DDR_TRAINING_INIT)

-

记录训练开始时间戳。

-

初始化训练参数和校准数据结构。

-

设置重试计数器、错误计数器等。

2. 检查是否为 OFF_MODE(DDR_TRAINING_CHECK_FOR_OFFMODE)

-

若配置为 DDR_OFF_MODE,则关闭 DDR 相关功能并退出。

-

否则继续初始化流程。

3. 设置模式寄存器和 VS Bits(DDR_TRAINING_SET_MODE_VS_BITS)

-

根据 DDR 类型(DDR3/DDR4/LPDDR3/LPDDR4)设置模式寄存器。

-

配置电压选择(VS)和驱动强度等。

4. 刷新 RPC 寄存器(DDR_TRAINING_FLASH_REGS)

-

软复位解码器和 I/O 驱动器,重新加载 RPC 寄存器。

5. 校正 RPC 寄存器(DDR_TRAINING_CORRECT_RPC)

-

根据 DDR 类型覆盖某些 RPC 寄存器的默认值。

6. 软复位(DDR_TRAINING_SOFT_RESET)

-

复位 DDR 控制器和 PHY,加载新的 RPC 配置。

7. I/O 校准(DDR_TRAINING_CALIBRATE_IO)

-

执行 PVT(Process, Voltage, Temperature)校准。

8. 配置 PLL 并等待锁定(DDR_TRAINING_CONFIG_PLL → DDR_TRAINING_VERIFY_PLL_LOCK)

-

配置 DDR PLL 并等待其锁定。

9. 设置内存段(DDR_TRAINING_SETUP_SEGS)

-

配置内存地址映射和段寄存器。

10. 初始化 DDR 控制器(DDR_TRAINING_SETUP_DDRC)

-

配置 DDRC 的所有寄存器,使用 Libero 生成的设置。

11. 复位训练逻辑(DDR_TRAINING_RESET)

-

断言训练复位信号,准备开始训练。

12. 时钟旋转(DDR_TRAINING_ROTATE_CLK)

-

调整 BCLK 和 SCLK 相位。

13. 设置训练参数(DDR_TRAINING_SET_TRAINING_PARAMETERS)

-

配置训练所需的参数,如偏移量、延时等。

14. BCLK/SCLK 训练(DDR_TRAINING_IP_SM_BCLKSCLK_SW)

-

使用软件或硬件方式进行 BCLK/SCLK 偏移训练。

15. 手动地址命令训练(DDR_MANUAL_ADDCMD_TRAINING_SW)

-

对非 LPDDR4 类型进行手动地址命令训练。

16. 启动硬件训练状态机(DDR_TRAINING_IP_SM_START)

-

启动 DDRC 和 PHY 的硬件训练状态机。

17. 等待训练完成(DDR_TRAINING_IP_SM_START_CHECK → DDR_TRAINING_IP_SM_VERIFY)

-

等待 DFI 训练完成信号,检查各阶段状态(BCLK/ADDCMD/WRLVL/RDGATE/DQDQS)。

18. 设置最终模式(DDR_TRAINING_SET_FINAL_MODE)

-

配置最终的 DDR PHY 模式。

19. 写校准(DDR_TRAINING_WRITE_CALIBRATION)

-

使用 MTC(Memory Test Core)进行写延迟校准。

20. 完整性检查(DDR_SANITY_CHECKS)

-

执行基本读写测试,验证内存可用性。

21. 全面 MTC 测试(DDR_FULL_MTC_CHECK)

-

使用多种数据模式和地址模式进行内存测试。

22. 32 位和 64 位非缓存/缓存访问测试(DDR_FULL_32BIT_NC_CHECK → DDR_FULL_64BIT_WRC_CHECK)

-

分别测试非缓存和缓存模式下的读写功能。

23. VREFDQ 校准(可选)(DDR_TRAINING_VREFDQ_CALIB → DDR_TRAINING_FPGA_VREFDQ_CALIB)

-

进行 FPGA 端和内存端的 VREF 校准。

24. 初始化所有内存(DDR_TRAINING_INIT_ALL_MEMORY)

-

若启用 ECC,则初始化整个内存空间。

25. 完成检查(DDR_TRAINING_FINISH_CHECK)

-

记录训练时间、重试次数,清理缓存,返回成功或失败状态。

3、包含完整测试的日志记录(第二个串口)

[10:47:20.758]收←◆

Start training. TIP_CFG_PARAMS:07CFE02F

dpc_bits: 00050422

CFG_DDR_SGMII_PHY->rpc156.rpc156 = 00000001

Spare bit value: 0000A000

PCODE = 00000018

NCODE = 0000001E

addr_cmd_value: 00000000

bclk_sclk_offset_value: 00000000

dpc_vrgen_v_value: 00000000

dpc_vrgen_h_value: 00000000

dpc_vrgen_vs_value: 00000000

tip_cfg_params: 07CFE02F

bclk_phase 00000400

bclk_sclk_offset value 00000005

ca_indly 00000000 vref 00000005 a5_dly_max:00000000 a5_dly_min:00000080 a5_dly_min_last:00000080 range_a5:FFFFFF80 deltat:00000080 in_window:00000000 vref_answer:00000080

ca_indly 00000000 vref 00000006 a5_dly_max:00000000 a5_dly_min:00000080 a5_dly_min_last:00000080 range_a5:FFFFFF80 deltat:00000080 in_window:00000000 vref_answer:00000080

[10:47:20.820]收←◆

ca_indly 00000000 vref 00000007 a5_dly_max:00000000 a5_dly_min:00000080 a5_dly_min_last:00000080 range_a5:FFFFFF80 deltat:00000080 in_window:00000000 vref_answer:00000080

[10:47:20.885]收←◆

ca_indly 00000000 vref 00000008 a5_dly_max:0000006A a5_dly_min:00000030 a5_dly_min_last:00000080 range_a5:0000003A deltat:00000080 in_window:00000000 vref_answer:00000080

ca_indly 00000000 vref 00000009 a5_dly_max:00000038 a5_dly_min:00000001 a5_dly_min_last:00000030 range_a5:00000037 deltat:00000080 in_window:00000000 vref_answer:00000080

ca_indly 00000000 vref 0000000A a5_dly_max:00000003 a5_dly_min:00000002 a5_dly_min_last:00000001 range_a5:00000001 deltat:00000001 in_window:00000001 vref_answer:00000080

ca_indly 00000000 vref 0000000B a5_dly_max:00000005 a5_dly_min:00000004 a5_dly_min_last:00000002 range_a5:00000001 deltat:00000002 in_window:00000003 vref_answer:00000080

ca_indly 00000005 vref 00000005 a5_dly_max:00000000 a5_dly_min:00000080 a5_dly_min_last:00000002 range_a5:FFFFFF80 deltat:00000080 in_window:00000000 vref_answer:00000080

ca_indly 00000005 vref 00000006 a5_dly_max:00000000 a5_dly_min:00000080 a5_dly_min_last:00000080 range_a5:FFFFFF80 deltat:00000080 in_window:00000000 vref_answer:00000080

ca_indly 00000005 vref 00000007 a5_dly_max:00000000 a5_dly_min:00000080 a5_dly_min_last:00000080 range_a5:FFFFFF80 deltat:00000080 in_window:00000000 vref_answer:00000080

ca_indly 00000005 vref 00000008 a5_dly_max:00000066 a5_dly_min:0000002C a5_dly_min_last:00000080 range_a5:0000003A deltat:00000080 in_window:00000000 vref_answer:00000080

ca_indly 00000005 vref 00000009 a5_dly_max:00000033 a5_dly_min:00000031 a5_dly_min_last:0000002C range_a5:00000002 deltat:00000005 in_window:00000001 vref_answer:00000080

[10:47:20.999]收←◆

ca_indly 00000005 vref 0000000A a5_dly_max:00000034 a5_dly_min:00000034 a5_dly_min_last:00000031 range_a5:00000000 deltat:00000003 in_window:00000003 vref_answer:00000080

vref_answer found0000000A

Returning FPGA CA VREF & CA drive to user setting.

00000000

ADDCMD_OFFSET 00000005

pll_phadj_during_init_2_3 02030201

pll_phadj_during_init_0_1 04000207

Writing MR1 00000000

Writing MR2 00000000

Writing MR3 00000000

Writing MR4 00000000

Writing MR11 00000000

Writing MR16 00000000

Writing MR17 00000000

Writing MR22 00000000

Writing MR13 00000000

ca_indly 00000000 vref 00000005 a5_dly_max:0000002F a5_dly_min:0000002E a5_dly_min_last:00000080 range_a5:00000001 deltat:00000052 in_window:00000000 vref_answer:00000080

ca_indly 00000000 vref 00000006 a5_dly_max:00000030 a5_dly_min:00000030 a5_dly_min_last:0000002E range_a5:00000000 deltat:00000002 in_window:00000001 vref_answer:00000080

[10:47:21.333]收←◆

ca_indly 00000000 vref 00000007 a5_dly_max:00000031 a5_dly_min:00000030 a5_dly_min_last:00000030 range_a5:00000001 deltat:00000000 in_window:00000003 vref_answer:00000080

vref_answer found00000007

rx_a5 00000002 rx_ck 0000000A rx_ck_last 00000005 transition_a5 00000028 transition_ck 00000008 Iteration: 00000028 REFCLK_PHASE: 00000000

rx_a5 00000002 rx_ck 0000000A rx_ck_last 00000005 transition_a5 00000028 transition_ck 00000001 Iteration: 00000028 REFCLK_PHASE: 00000001

rx_a5 00000002 rx_ck 00000005 rx_ck_last 00000005 transition_a5 00000028 transition_ck 00000031 Iteration: 00000031 REFCLK_PHASE: 00000002

rx_a5 00000002 rx_ck 00000005 rx_ck_last 00000005 transition_a5 00000028 transition_ck 0000002A Iteration: 0000002A REFCLK_PHASE: 00000003

rx_a5 00000002 rx_ck 00000005 rx_ck_last 00000005 transition_a5 00000027 transition_ck 00000024 Iteration: 00000027 REFCLK_PHASE: 00000004

rx_a5 00000002 rx_ck 00000005 rx_ck_last 00000005 transition_a5 00000028 transition_ck 0000001C Iteration: 00000028 REFCLK_PHASE: 00000005

rx_a5 00000002 rx_ck 00000005 rx_ck_last 00000005 transition_a5 00000027 transition_ck 00000016 Iteration: 00000027 REFCLK_PHASE: 00000006

rx_a5 00000002 rx_ck 0000000F rx_ck_last 00000005 transition_a5 00000028 transition_ck 0000000F Iteration: 00000028 REFCLK_PHASE: 00000007

rx_a5 00000002 rx_ck 0000000A rx_ck_last 00000005 transition_a5 00000028 transition_ck 00000008 Iteration: 00000028 REFCLK_PHASE: 00000008

rx_a5 00000002 rx_ck 0000000A rx_ck_last 00000005 transition_a5 00000028 transition_ck 00000001 Iteration: 00000028 REFCLK_PHASE: 00000009

rx_a5 00000002 rx_ck 00000005 rx_ck_last 00000005 transition_a5 00000028 transition_ck 00000031 Iteration: 00000031 REFCLK_PHASE: 0000000A

rx_a5 00000002 rx_ck 00000005 rx_ck_last 00000005 transition_a5 00000027 transition_ck 0000002A Iteration: 0000002A REFCLK_PHASE: 0000000B

rx_a5 00000002 rx_ck 00000005 rx_ck_last 00000005 transition_a5 00000028 transition_ck 00000024 Iteration: 00000028 REFCLK_PHASE: 0000000C

rx_a5 00000002 rx_ck 00000005 rx_ck_last 00000005 transition_a5 00000028 transition_ck 0000001C Iteration: 00000028 REFCLK_PHASE: 0000000D

rx_a5 00000002 rx_ck 00000005 rx_ck_last 00000005 transition_a5 00000028 transition_ck 00000016 Iteration: 00000028 REFCLK_PHASE: 0000000E

rx_a5 00000002 rx_ck 0000000F rx_ck_last 00000005 transition_a5 00000027 transition_ck 0000000F Iteration: 00000027 REFCLK_PHASE: 0000000F

difference 00000020 REFCLK_PHASE 00000000

difference 00000027 REFCLK_PHASE 00000001

difference 000000FF REFCLK_PHASE 00000002

difference 000000FF REFCLK_PHASE

[10:47:21.502]收←◆ 00000003

difference 00000004 REFCLK_PHASE 00000004

difference 0000000C REFCLK_PHASE 00000005

difference 00000012 REFCLK_PHASE 00000006

difference 00000019 REFCLK_PHASE 00000007

CK_PUSH = 0 degrees00000000

MANUAL ADDCMD TRAINING Results:

PLL OFFSET: 00000003

transition_a5_max: 00000028

CA Output Delay: 00000004

CA Offset: 00000003

Writing MR1 00000000

Writing MR2 00000000

Writing MR3 00000000

Writing MR4 00000000

Writing MR11 00000000

Writing MR16 00000000

Writing MR17 00000000

Writing MR22 00000000

Writing MR13 00000000

pll_phadj_after_hw_training 01060104

pll_phadj_after_hw_training 02000106

DDR FINAL_MODE: 00014A24

training status = 0000001D

PCODE = 00000018

NCODE = 0000001E

WRCALIB_RESULT: 00005555

sro_ref_slewr = 0000000B

sro_ref_slewf = 0000000F

sro_slewr = 0000000B

sro_slewf = 0000000F

rank number00000000

lane_select gt_err_comb gt_txdly gt_steps_180 gt_state wl_delay_0 dqdqs_err_done dqdqs_state delta0 delta1

00000000 00000000 07150615 00000008 0000000B 00000019 00000008 00000008 02020200 01030303

00000001 00000000 07140515 00000008 0000000B 00000019 00000008 00000008 02010101 01000102

00000002 00000000 07160517 00000008 0000000B 0000001A 00000008 00000008 02010303 00030302

00000003 00000000 07140515 00000008 0000000B 0000001A 00000008 00000008 02020203 00020203

lane_select rdqdqs_status2 addcmd_status0 addcmd_status1 addcmd_answer1 dqdqs_status1

00000000 00000013 00000000 00000000 00000000 00000007

00000001 00000016 00000000 00000000 00000000 00000006

00000002 00000015 00000000 00000000 00000000 00000007

00000003 00000014 00000000 00000000 00000000 00000006

****************************************************00000000

Calibration offset used:00000000

Lane failed:00000000 All lanes status:00000000

Lane failed:00000001 All lanes status:00000000

Lane failed:00000002 All lanes status:00000000

Lane failed:00000003 All lanes status:00000000

Calibration offset used:00000001

Lane failed:00000000 All lanes status:00000000

Lane failed:00000001 All lanes status:00000000

Lane failed:00000002 All lanes status:00000000

Lane failed:00000003 All lanes status:00000000

Calibration offset used:00000002

Lane failed:00000000 All lanes status:00000000

Lane failed:00000001 All lanes status:00000000

Lane failed:00000002 All lanes status:00000000

Lane failed:00000003 All lanes status:00000000

Calibration offset used:00000003

Lane failed:00000000 All lanes status:00000000

Lane failed:00000001 All lanes status:00000000

Lane failed:00000002 All lanes status:00000000

Lane failed:00000003 All lanes status:00000000

Calibration offset used:00000004

Lane failed:00000000 All lanes status:00000000

Lane failed:00000001 All lanes status:00000000

Lane failed:00000002 All lanes status:00000000

Lane failed:00000003 All lanes status:00000000

Calibration offset used:00000005

Lane passed:00000000 All lanes status:00000001

Lane passed:00000001 All lanes status:00000003

Lane passed:00000002 All lanes status:00000007

[10:47:21.705]收←◆

Lane passed:00000003 All lanes status:0000000F

wr calib result 00005555

DDR SANITY_CHECKS: 00000000

[10:47:21.783]收←◆

Passed MTC full check 00000000

Pattern: 0x00000000w

[10:47:21.847]收←◆r

[10:47:21.974]收←◆w

[10:47:22.054]收←◆r

[10:47:22.182]收←◆

Pattern: 0x00000001w

[10:47:22.262]收←◆r

[10:47:22.391]收←◆w

[10:47:22.468]收←◆r

[10:47:22.612]收←◆

Pattern: 0x00000002w

[10:47:22.697]收←◆r

[10:47:22.851]收←◆w

[10:47:22.948]收←◆r

[10:47:23.092]收←◆

Pattern: 0x00000003w

[10:47:23.187]收←◆r

[10:47:23.460]收←◆w

[10:47:23.572]收←◆r

[10:47:23.859]收←◆

Pattern: 0x00000004w

[10:47:23.925]收←◆r

[10:47:24.057]收←◆w

[10:47:24.131]收←◆r

[10:47:24.259]收←◆

Pattern: 0x00000005w

[10:47:24.322]收←◆r

[10:47:24.451]收←◆w

[10:47:24.529]收←◆r

[10:47:24.675]收←◆

Loading test pattern

pattern size = 0000000002000000

pattern offset = 0000000C..........

Finished loading test pattern

Starting ddr test

[10:47:26.830]收←◆|

[10:47:27.038]收←◆ Iteration 00000001

Starting ddr test

[10:47:29.139]收←◆|

[10:47:29.351]收←◆ Iteration 00000001

Starting ddr test

[10:47:31.450]收←◆|

[10:47:31.767]收←◆ Iteration 00000001

wr write latency 00000003

rpc_166_fifo_offset: 00000002 Init memory, size = , 0x0000000080000000

ddr train time (ms): 00002ABE, DDR 初始化时间:10942 ms ,这里10秒是因为 日志打印耗时

Number of retrains: 00000000

training status = 0000001D

PCODE = 00000018

NCODE = 0000001E

WRCALIB_RESULT: 00005555

sro_ref_slewr = 0000000B

sro_ref_slewf = 0000000F

sro_slewr = 0000000B

sro_slewf = 0000000F

rank number00000000

lane_select gt_err_comb gt_txdly gt_steps_180 gt_state wl_delay_0 dqdqs_err_done dqdqs_state delta0 delta1

00000000 00000000 07150615 00000008 0000000B 00000019 00000008 00000008 02020200 01030303

00000001 00000000 07140515 00000008 0000000B 00000019 00000008 00000008 02010101 01000102

00000002 00000000 07160517 00000008 0000000B 0000001A 00000008 00000008 02010303 00030302

00000003 00000000 07140515 00000008 0000000B 0000001A 00000008 00000008 02020203 00020203

lane_select rdqdqs_status2 addcmd_status0 addcmd_status1 addcmd_answer1 dqdqs_status1

00000000 00000013 00000000 00000000 00000000 00000007

00000001 00000016 00000000 00000000 00000000 00000006

00000002 00000015 00000000 00000000 00000000 00000007

00000003 00000014 00000000 00000000 00000000 00000006

DDR_TRAINING_PASS:

Loading test pattern

pattern size = 0000000000800000

pattern offset = 00000000................................

Finished loading test pattern

[10:50:32.140]收←◆

---------------------------------------------------------------------

Application code executes from the U54_1.

Please observe its UART for application messages.

---------------------------------------------------------------------

\0

浙公网安备 33010602011771号

浙公网安备 33010602011771号