PolarFire® SoC 上电启动流程

PolarFire Family Power-Up and Resets User Guide

PolarFire SoC MSS Technical Reference Manual

PolarFire® SoC Software Development and Tool Flow User Guide

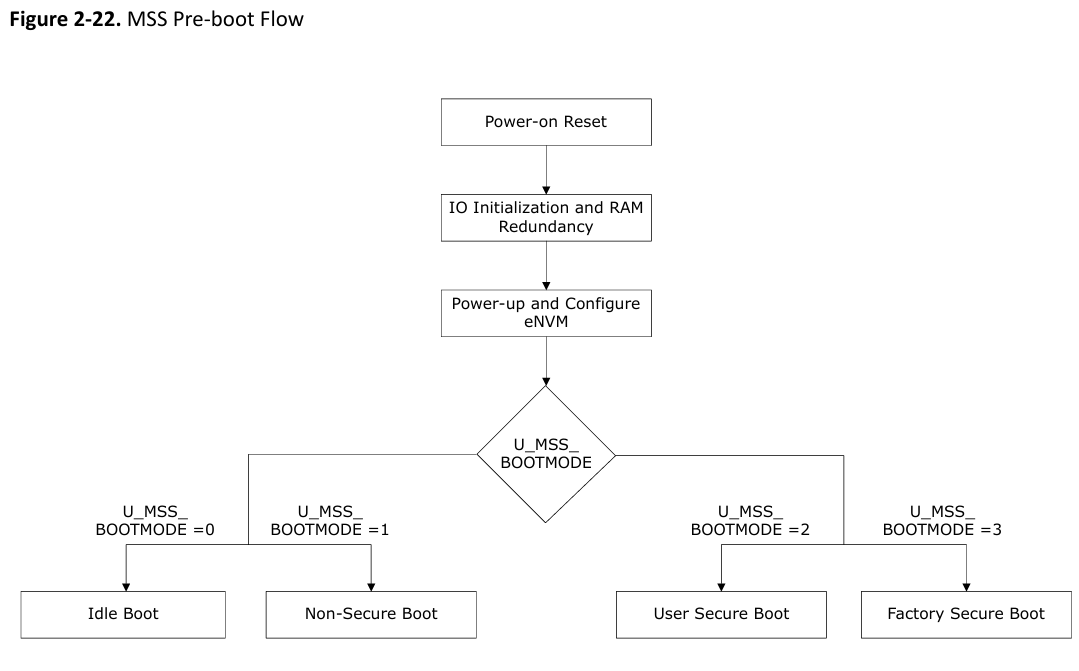

The MSS Core Complex can be booted in one of four modes. The following table lists the MSS pre-boot options, which can be configured and programmed into the sNVM. The boot mode is defined by the user parameter U_MSS_BOOTMODE[1:0]. Additional boot configuration data is mode-dependent and is defined by the user parameter U_MSS_BOOTCFG (see Table 3, page 4 and Table 5, page 6).

MSS Core Complex 可在四种模式中的任意一种下启动。下表列出了可在 sNVM 中配置并烧录的 MSS 预启动选项。启动模式由用户参数 U_MSS_BOOTMODE[1:0] 定义。其余的启动配置数据则取决于所选模式,并由用户参数 U_MSS_BOOTCFG 定义(参见第 4 页的表 3 和第 6 页的表 5)。

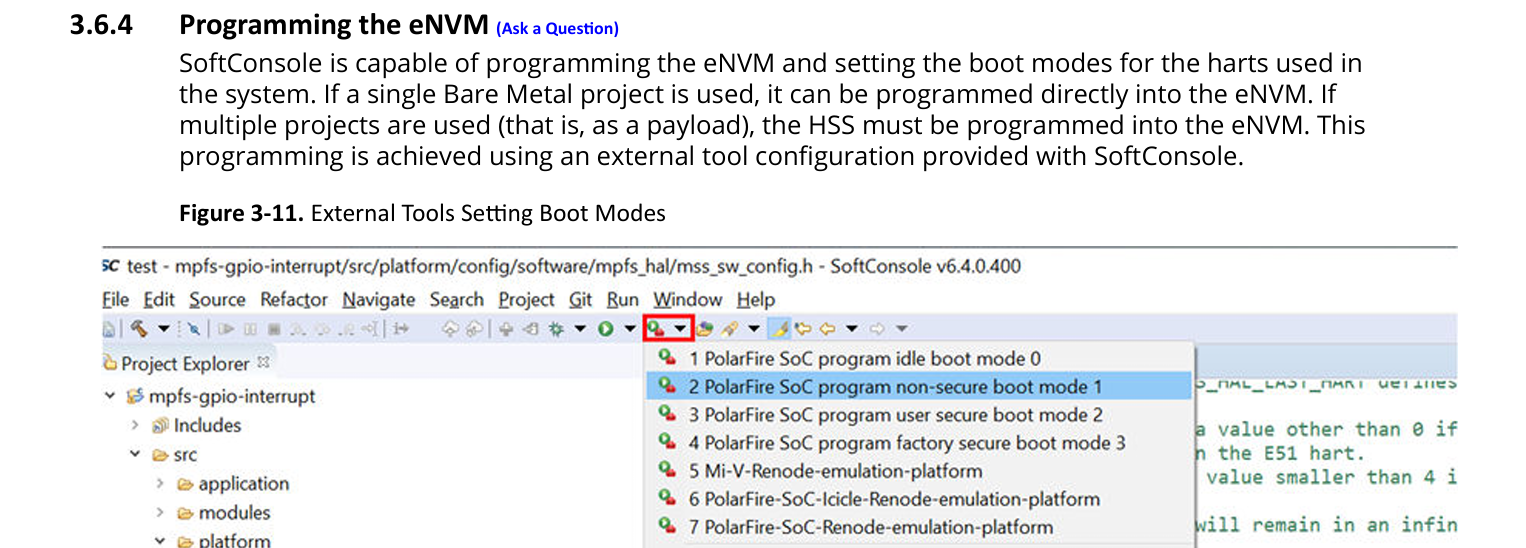

查了半天,也没找到 U_MSS_BOOTMODE 在哪里配置? 问题解决是在 softconsole → run → Extern tools , 来自文档:PolarFire® SoC Software Development and Tool Flow User Guide

操作记录:

PolarFire® SoC softconsole fpgenprog.exe 路径错误 导致 无法更改 启动模式 - 所长 - 博客园

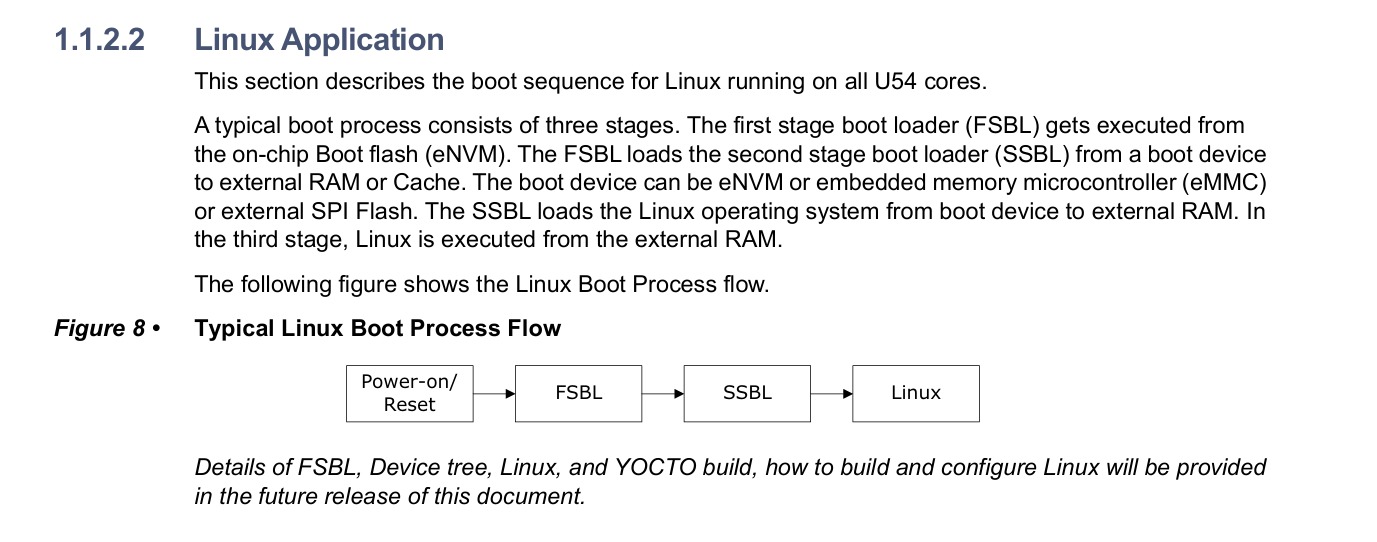

linux 启动方式

这份名为 《Microchip PolarFire FPGA and PolarFire SoC FPGA Power-Up and Reset User Guide》 的文档详细阐述了 PolarFire 芯片从上电到稳定运行的整个过程。以下是其核心内容的总结,并特别突出了与 SoC 启动相关的细节。

文档核心内容总结

该文档主要描述了 PolarFire FPGA 和 PolarFire SoC FPGA 的电源序列要求、各种复位类型以及整个器件从断电到进入用户模式的完整启动流程。

1. 电源序列 (Power-Up Sequencing)

这是启动的物理基础,要求非常严格。

-

核心电压 (VCC):

-

PolarFire SoC: 要求 VCC 和 VCCPLL 必须先于所有其他电源上电。

-

PolarFire FPGA: 要求相对宽松,VCC 可以在其他电源之前、之后或同时上电。

-

-

辅助电压 (VCCAUX, VCCIOS, etc.): 必须在核心电压 VCC 稳定后上电。

-

电池备份电压 (VBAT_BKUPS): 如果使用,必须在 VCCAUX 之前或同时上电。

-

关键点: 不正确的上电顺序可能导致器件无法启动或损坏。建议使用 Microchip 推荐的电源管理芯片(PMIC)来实现正确的时序。

2. 复位类型 (Reset Types)

文档定义了多种复位信号,它们在不同层级和条件下触发:

-

上电复位 (Power-On Reset, POR):

-

由电源监控电路产生,是所有复位信号的根源。

-

当检测到核心电压 VCC 达到有效电平时,POR 信号会被释放。

-

-

硬件复位 (HW_RST):

-

由外部

HRESET_N引脚触发,产生一个全局复位。

-

-

** fabric 复位 (FABRIC_POR_N)**:

-

源自 POR 和 HW_RST,用于复位 FPGA 架构逻辑。

-

-

系统控制器复位 (SYS_CONTROLLER_RST):

-

SoC 特有。复位整个微控制器子系统(MSS),包括 E51 和 U54 核心。

-

-

调试复位 (DEBUG_RST):

-

由调试器通过 JTAG 发起,用于复位调试逻辑。

-

3. 启动流程 (Boot Flow)

这是文档中最关键的部分,详细描述了复位释放后芯片内部的操作序列。

Phase 0: 电源稳定与 POR

-

电源按要求序列上电并稳定。

-

芯片内部的 POR 电路监控电压,一旦 VCC 有效,POR 信号被释放。

Phase 1: 硬件初始化与启动源选择

-

器件解除复位,开始内部初始化。

-

采样配置引脚 (MODE[4:0]): 器件根据这些引脚的电平状态,锁定启动源(如 SPI Flash, eNVM, SD卡等)和其他关键配置(如调试是否启用、安全启动模式等)。此采样仅在 POR 之后进行一次。

Phase 2: BootROM 执行 (Stage 0)

-

SoC 特有。E51 作为启动核心(Boot Hart)开始执行固化在芯片内部 ROM 中的代码。

-

主要任务:

-

初始化: 配置 MSS 的基础环境(如指令缓存)。

-

认证: 如果启用了安全启动(Fabric Authentication),它会验证 FPGA 比特流和 FSBL 代码的完整性和真实性。

-

加载 FSBL: 从选定的启动源中加载第一级引导程序(FSBL) 的镜像到芯片的紧耦合存储器(LIM)或 L2 Scratchpad 中。

-

跳转: 验证通过后,将执行权交给 FSBL。

-

Phase 3: 用户模式启动 (Stage 1 and Beyond)

-

FSBL 执行: E51 核心执行用户提供的 FSBL 代码。

-

初始化关键硬件: 如系统时钟 PLL、DDR 内存控制器、必要的外设(如 UART)。

-

加载后续镜像: 从非易失性存储器加载更大的第二级引导程序(SSBL)或裸机应用程序到已初始化的 DDR 内存中。

-

唤醒应用核心: 通过写寄存器,释放 U54 核心的复位,使其从指定的地址(在 DDR 中)开始执行。

-

跳转: E51 最终跳转到 DDR 中的主应用程序代码。

-

-

应用程序执行: 所有核心(E51 和 U54s)开始在 DDR 中运行用户代码(裸机或操作系统)。

总结与关键要点

-

电源是根基: 严格的电源序列是成功启动的绝对前提,错误的序列会导致无法预知的行为。

-

配置采样是关键一刻: 器件在 POR 释放后立即采样

MODE[4:0]等引脚,并锁定配置。一旦进入用户模式,这些配置就无法再更改,除非再次发生 POR。 -

BootROM 是信任根: SoC 的启动流程由硬件和不可更改的 BootROM 固件主导。它建立了最初的安全信任链(如果启用)并加载了用户的第一段代码(FSBL)。

-

E51 是启动核心: 在整个启动过程中,E51 核心是唯一从上电开始就活动的处理器核心,它负责初始化环境并唤醒其他 U54 核心。

-

清晰的阶段划分: 启动流程清晰地分为:

-

硬件控制阶段 (Phase 0-2): 由 POR, 配置采样, BootROM 执行组成。

-

软件控制阶段 (Phase 3): 从 FSBL 开始,后续所有代码均由用户提供。

-

这份文档是理解 PolarFire SoC 底层硬件行为、排查启动失败问题和设计可靠电源电路的权威参考。

浙公网安备 33010602011771号

浙公网安备 33010602011771号