PolarFire® SoC softconsole 裸机工程中 ICICLE_MSS_eMMC_cfg.xml 文件的作用

PolarFire SoC MSS Configurator User Guide

文档分析与 .xml 文件作用解析

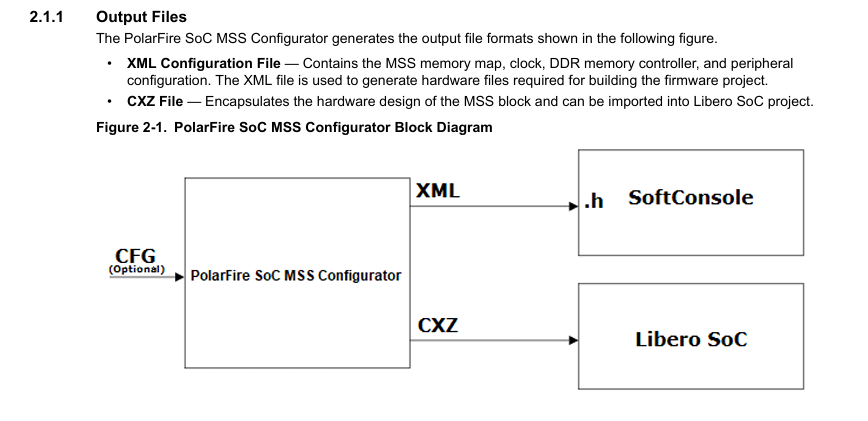

根据您提供的上下文,该文档描述的是一个针对Microchip PolarFire SoC FPGA的裸机示例项目的结构和构建流程。其核心是建立FPGA硬件设计(在Libero软件中完成)与软件应用程序(在SoftConsole IDE中开发)之间的桥梁,而.xml文件正是这座桥梁的“设计蓝图”。

.xml 文件的角色与作用

.xml文件是硬件设计的机器可读描述文件。它由Microchip的Libero SoC设计工具在您配置FPGA上的微处理器子系统(MSS)时自动生成。

它的主要作用体现在以下两个层面:

-

作为自动生成代码的输入源 (Input Source)

这是其最核心的作用。项目中的Python脚本(如mpfs_configuration_generator.py)会解析这个.xml文件。-

输入什么? 脚本接收

.xml文件作为输入。 -

输出什么? 脚本根据

.xml文件中的硬件描述,自动生成C语言头文件(位于fpga_design_config文件夹)。 -

生成什么内容? 这些自动生成的头文件包含了软件工程所需的所有硬件特定配置,例如:

-

外设基地址:每个硬件模块(如UART, I2C, GPIO等)在内存中的地址。

-

中断编号:每个外设所对应的中断请求号。

-

时钟频率:各个时钟域的配置频率。

-

引脚复用配置:IO引脚的功能定义。

-

内存布局:片上存储器、紧密耦合存储器(TCM)、外部内存等的地址范围。

-

-

-

作为确保软硬件匹配的“单一事实来源” (Single Source of Truth)

-

文档中强调 “必须确保示例项目中的配置与实际Libero设计的配置相匹配”,

.xml文件就是实现这一点的关键。 -

软件工程师不需要也不应该手动去修改那些自动生成的头文件。任何硬件设计的更改(例如在Libero中增加一个UART外设或更改某个时钟频率),只需重新导出

.xml和.cfg文件,并将其替换到项目的design_description文件夹中。 -

在下一次构建时,预构建步骤会自动运行脚本,读取新的.xml文件,并重新生成新的、与当前硬件设计完全匹配的头文件。这从根本上避免了手动修改可能带来的错误和不一致,保证了软件访问硬件的底层代码永远与硬件设计同步。

-

工作流程总结

整个流程可以清晰地概括为以下几步:

-

硬件设计 (Libero SoC):

-

工程师在Libero中配置PolarFire SoC的MSS(选择外设、设置时钟、分配引脚等)。

-

Libero工具链综合、布局布线并生成最终设计。

-

Libero导出该设计的配置数据,即

.xml和.cfg文件。

-

-

配置导入 (SoftConsole Project):

-

工程师将Libero导出的

.xml和.cfg文件手动复制到裸机示例项目的对应目录(.../design_description/和.../mss_configuration/)。

-

-

预构建自动化 (Pre-build Step):

-

在SoftConsole中构建项目时,会自动执行一个预定义命令(调用

mpfs_configuration_generator.py)。 -

该脚本读取

design_description文件夹中的.xml文件。

-

-

代码生成 (Auto-generation):

-

脚本解析

.xml,并自动生成出包含所有硬件地址、中断号等信息的C头文件。 -

这些头文件被放置在

fpga_design_config文件夹中。此文件夹由脚本创建,不应手动创建或修改。

-

-

编译与链接 (Compilation):

-

项目的C源代码(如

main.c)#include这些自动生成的头文件,从而能够以正确的地址和配置访问硬件外设。 -

编译器将应用程序代码与硬件配置代码一起编译,生成最终可执行文件。

-

结论

简而言之,.xml文件是连接FPGA硬件世界和嵌入式软件世界的核心纽带。它将Libero设计工具中的图形化配置转换成了软件工程可直接使用的具体数值定义,并通过自动化的流程确保了软硬件之间绝对的同步性,极大地提高了开发效率和可靠性。

因此,文档中反复强调的操作要点——用您实际Libero设计生成的.xml文件替换项目中的.xml文件——是成功定制和运行项目的最关键一步。

浙公网安备 33010602011771号

浙公网安备 33010602011771号