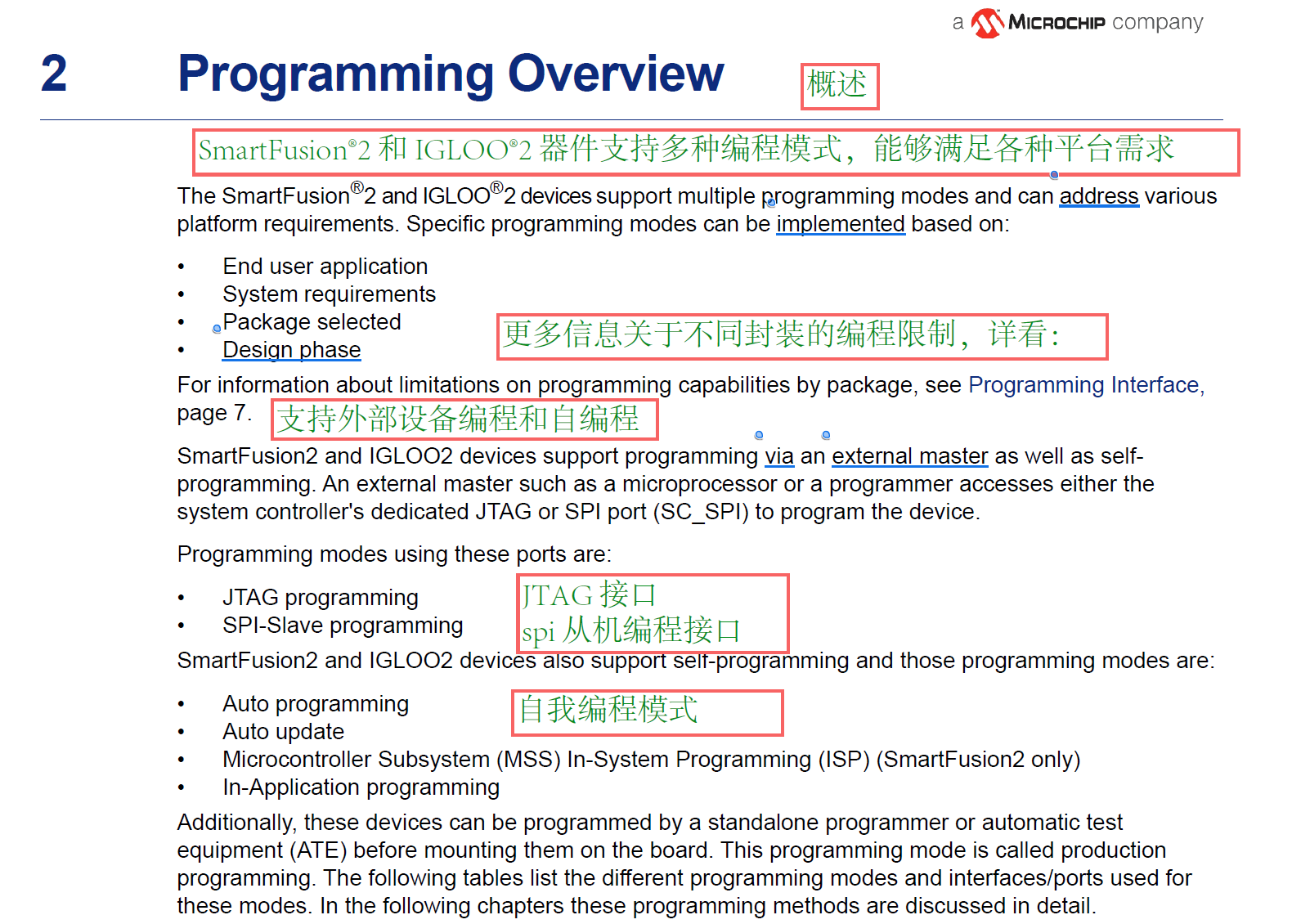

SmartFusion2 and IGLOO2 Programming

UG0451: SmartFusion2 and IGLOO2 Programming User Guide

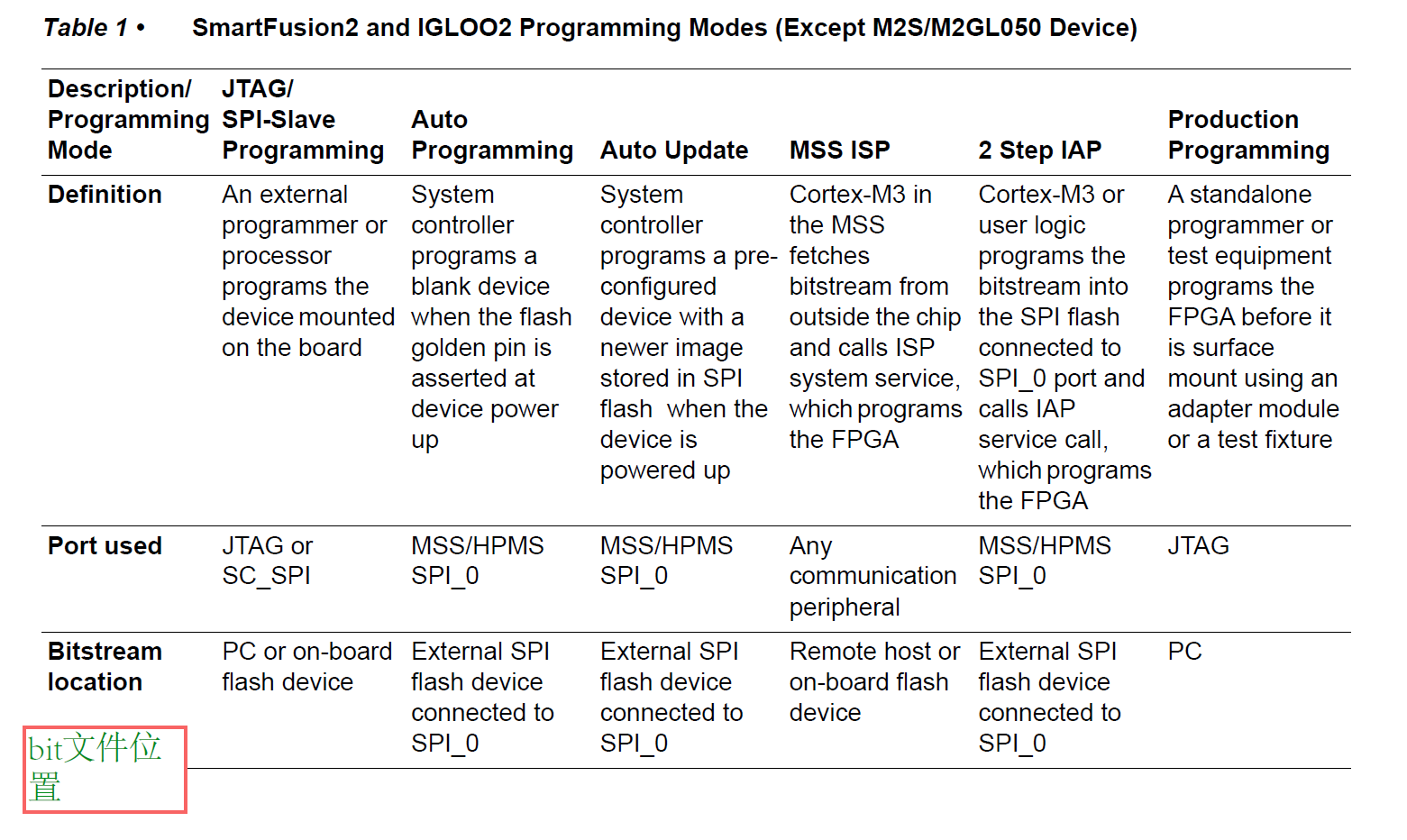

1、JTAG 编程

- 使用外部编程器,JTAG协议, 对设备编程; 比如 FLASH PRO5

- 使用外部MCU运行 DirectC 代码, 模拟 JTAG 协议,对设备进行编程, DirectC v4.0 User Guide

2、SPI Slave Programming

-

模式定义 (Mode Definition):

-

SPI 从编程模式 是一种配置方式,其中 SmartFusion2/IGLOO2 器件 扮演 从设备 的角色。

-

一个 外部的 SPI 主设备 负责发起和控制整个编程过程,向作为从设备的 SmartFusion2 发送编程数据和指令。

-

-

谁是主设备?(Who is the Master?):

-

主设备可以是两类东西:

-

外部微处理器: 例如,一块 Arduino、一颗 ARM Cortex-M 系列的 MCU、或者是您系统板上另一个现成的处理器。

-

专用编程器: 文中 specifically 提到了 FlashPro5,这是 Microsemi(现 Microchip)官方推荐的编程器之一。

-

-

-

硬件接口 (Hardware Interface):

-

物理连接必须通过芯片上一个 专用的 SC_SPI 端口。

-

SC_SPI 代表 系统控制器的 SPI,这个端口是系统控制器专门用于编程和配置的接口。

-

这个端口 默认就是 SPI 从模式,所以一旦您将外部主设备的 SPI 线连接到这些引脚上,芯片就准备好了接受来自主设备的指令。

-

-

通信协议配置 (Communication Protocol Settings):

-

通信的 SPI 模式 是 固定不变的。系统控制器只使用 SPI 模式 3。

-

模式 3 的定义是:

-

CPOL/SPO = 1: 时钟空闲状态为高电平。

-

CPHA/SPH = 1: 数据在时钟的第二个边沿(即从高电平跳变到低电平的下降沿)被采样。

-

-

这意味着外部主设备在通信时也必须配置为使用 SPI 模式 3,否则双方无法正常通信。

-

-

重要限制与兼容性 (Important Limitations & Compatibility):

-

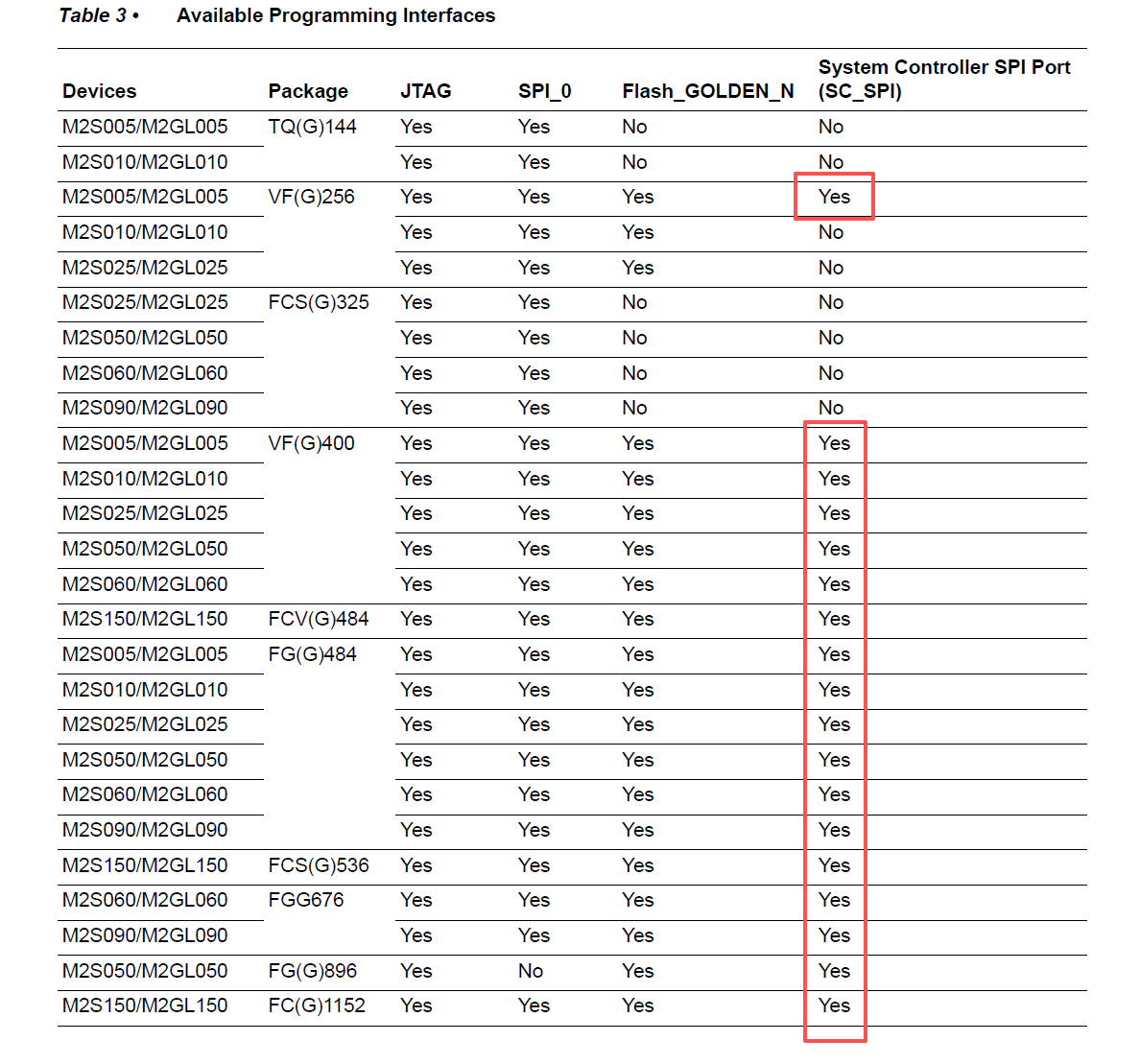

并非所有芯片封装都支持此功能! 由于引脚数量的限制,某些较小的封装可能没有引出专用的 SC_SPI 端口。

-

在进行硬件设计之前,必须查阅文档中的 Table 3 on page 7,以确认您选择的特定型号和封装支持 SC_SPI 编程。

-

-

两种主设备方案的细微差别 (Two Master Options):

-

当使用 专用编程器(如 FlashPro5) 时,编程器内部已经集成了所有必要的协议和逻辑,可以直接连接并编程。

-

当使用一个 通用的外部微处理器 作为主设备时,您需要在这个处理器上实现 Microsemi 的 DirectC-SPI 编程协议。这意味着您需要在微处理器上编写或运行特定的代码,让它能够正确地生成和发送符合规范的 JBC 或 STAPL 命令流。具体的实现方法需要参考 《SPI-DirectC Solution User Guide》 这份文档。

-

3、Auto Programming

-

触发条件:

-

当系统重启(上电或复位)时,如果专用的 FLASH_GOLDEN_N 引脚被拉低(asserted low),就会触发自动编程模式。

-

这个引脚就像一个“模式选择开关”,告诉芯片:“这次启动不要等别人来配置你,请自己去外部Flash里读取配置。”

-

-

主从角色切换:

-

一旦触发,芯片内部的 系统控制器 会自动将其 MSS 或 HPMS 模块上的 SPI_0 端口 配置为 SPI 主模式。

-

这意味着,芯片从通常的“从设备”变成了“主设备”,而外部的SPI Flash则成为了“从设备”。芯片现在主动发起通信来读取数据。

-

-

硬件连接要求:

-

必须将一个已经 预先编程好.bit/.jbc 比特流文件的 外部 SPI Flash 存储器 连接到芯片的 SPI_0 端口上。

-

这个SPI Flash不是芯片内部的eNVM,而是一个独立的外部芯片。

-

-

兼容的Flash类型:

-

外部SPI Flash必须支持特定的指令集,系统控制器才能与之正确通信:

-

RDID (0x9F): 读取芯片ID命令。用于识别Flash制造商和设备型号。

-

24-bit read (0x0B): 标准读取命令,使用24位地址线,最多可寻址 16MB (2^24) 的存储空间。

-

32-bit read (0x0C): 扩展读取命令,使用32位地址线,用于寻址大于16MB的存储空间。

-

-

智能切换机制: 系统控制器非常智能。它会先发送 RDID 命令来查询Flash的容量。

-

如果查询到的容量 大于 16MB,控制器就会自动切换并使用 0x0C 命令来读取。

-

如果容量 小于或等于 16MB,它就使用 0x0B 命令。

-

这确保了与不同容量SPI Flash的兼容性。

-

-

重要注意事项

-

封装限制: 和之前的SC_SPI端口一样,FLASH_GOLDEN_N 这个引脚并不是在所有芯片封装上都可用。通常只有引脚数量足够多的封装才会引出这个特殊功能的引脚。

-

必须查阅手册: 在选择芯片封装进行硬件设计之前,必须参考文档中的 Table 3 on page 7,以确认您选择的封装是否支持此功能(即是否有 FLASH_GOLDEN_N 引脚)。如果选错了封装,将无法使用这种自动编程模式。

应用场景

这种模式非常适合以下情况:

-

量产: 可以在生产线上预先将程序烧录到SPI Flash中,然后将Flash和FPGA一起焊接到板子上。产品到达用户手中后,一通电就能自动配置,无需任何外部干预。

-

独立工作: 产品不需要连接编程器或外部处理器,上电即可运行,非常可靠。

-

固件恢复: 可以设计一个“黄金镜像”,当主系统升级失败时,通过触发这个引脚来从备份的SPI Flash中恢复原始设计。

总结

自动编程模式 是一种“自力更生”的配置方式。通过一个专用引脚触发,让FP芯片在启动时扮演主设备角色,主动从外部SPI Flash中读取配置程序来完成自我编程,是实现产品独立运行和量产化的关键技术。

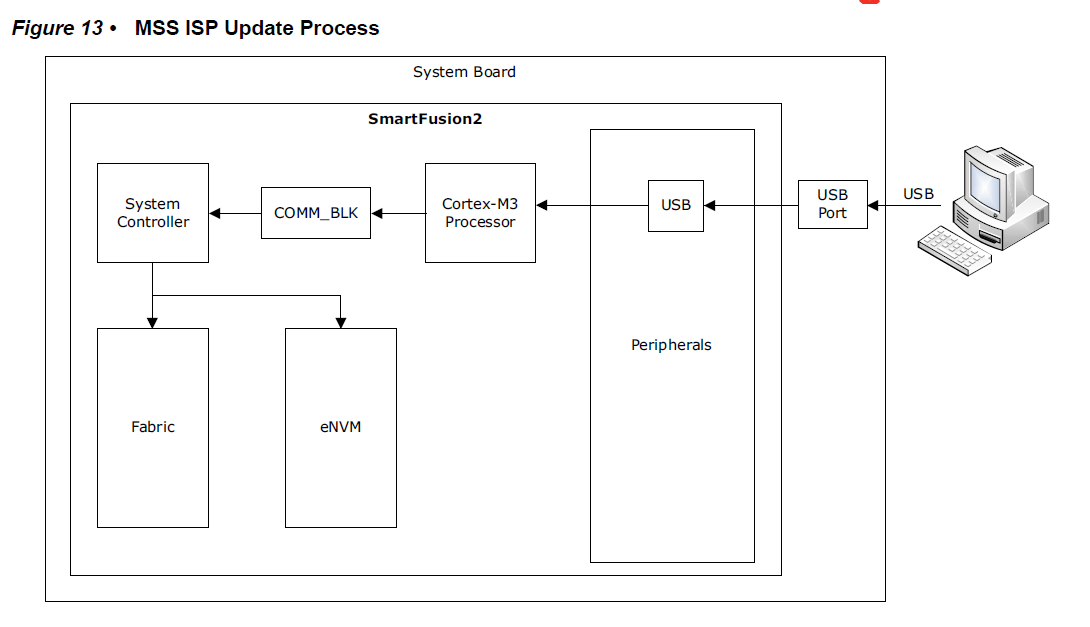

4、MSS ISP (SmartFusion2 Only)

-

控制主体:

-

编程过程不再由外部编程器或 SPI Flash 主导,而是由芯片内部的 Cortex-M3 处理器 上运行的 用户固件 所控制。

-

-

数据来源:

-

Cortex-M3 固件通过一个或多个 通信端口 主动地 获取 编程比特流。这些端口包括:

-

USB、MMUART (通用异步串口)、SPI、I2C 等。

-

-

这意味着编程数据可以来自几乎任何地方:一台通过USB连接的电脑、一个通过串口发送数据的模块、网络上的某个服务器(通过以太网转换)等。

-

-

数据传输路径:

-

Cortex-M3 从通信端口收到数据后,并不会直接处理编程操作,而是通过一个叫做 COMM_BLK 的硬件模块,将数据转发给 系统控制器。

-

系统控制器 才是最终执行擦除、编程、验证等底层硬件操作的“专家”。

-

-

芯片状态 during Programming:

-

在编程和验证过程中,FPGA 逻辑单元是停止工作的。这意味着您设计的数字逻辑电路会暂时功能中断。

-

注意: 但 Cortex-M3 处理器本身还在运行!正是它在执行固件代码来管理这个编程流程。

-

-

“单步”完成:

-

整个过程是连续的:“下载” 和 “编程” 是同一个步骤。Cortex-M3 一边接收数据,系统控制器就一边进行编程。它不是先把整个文件下载到某个缓存再开始编程。

-

-

重要前提条件:

-

这是最关键的一点:要使用这种模式,SmartFusion2 器件必须已经被预先编程好一段特殊的“用户固件”到它的 Cortex-M3 或 eNVM 中。

-

这段固件包含了调用系统控制器 ISP服务 的代码。ISP 代表 在系统编程。

-

简单说:你必须先有一种方式(比如JTAG或之前的SPI模式)把这段管理程序“烧”进去,之后才能享受这种灵活的在线编程能力。

-

核心概念解释

MSS ISP 指的是通过芯片内部的 微控制器子系统(Microcontroller Subsystem, MSS),即 Cortex-M3 处理器,进行 在系统编程(In-System Programming) 的一种服务。

这种模式允许用户通过运行在 Cortex-M3 上的自定义固件,调用系统控制器提供的编程功能,从而灵活地更新器件本身。

详细要点解析

-

工作流程:

-

数据路径: 编程比特流从一个 远程PC 通过 USB 连接发送到 SmartFusion2 芯片。MSS(Cortex-M3)的固件负责接收这些数据。

-

“单步”完成: 数据的“下载”和“编程”动作是连续、同步进行的,无需中间存储。

-

Fabric 状态: 在编程过程中,FPGA 逻辑单元进入 F*F 模式,即 Flash*Freeze 模式。在此模式下,逻辑单元被冻结(非工作状态),其 I/O 引脚处于高阻态,从而避免对板级其他电路造成干扰。

-

-

关键前提与配置:

-

通信端口使能: 用于接收比特流的通信端口(本例中是 USB)必须在编程期间保持启用状态。这个配置是在 Libero SoC 设计软件中完成的:

-

具体路径:I/O Attributes 菜单中设置。

-

相关机制:Use of Flash Freeze Mechanism。这确保了在逻辑单元冻结时,MSS 所需的通信 I/O 仍能正常工作。

-

-

MSS 必须持续供电: 整个编程过程中,Cortex-M3 处理器必须保持运行,因为它是指挥官。任何导致 MSS 断电或复位的情况都会使编程失败。

-

-

编程恢复机制:

-

这是一个重要的安全功能。如果编程过程中发生 电源故障,可能导致器件“变砖”。编程恢复功能 可以作为一种补救机制(例如,在下次上电时尝试从备份源恢复)。

-

-

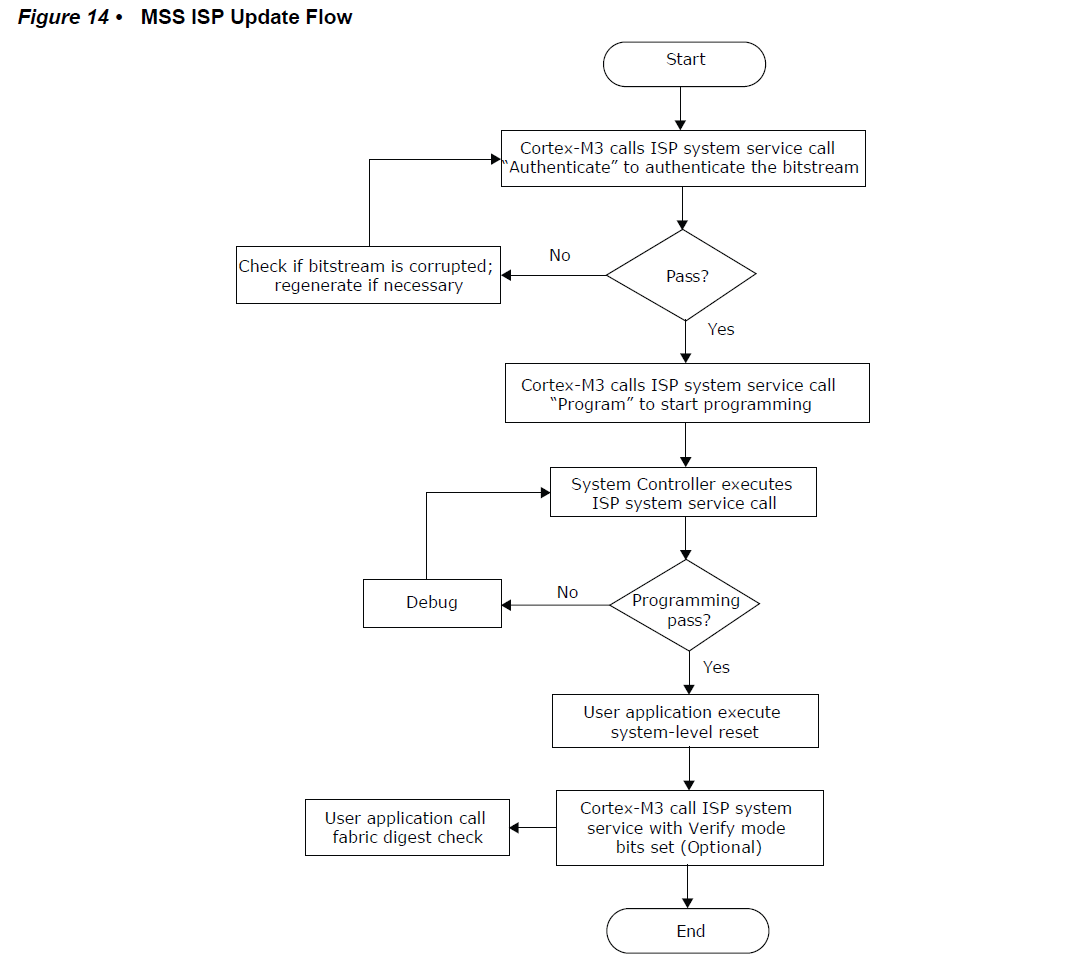

MSS ISP 服务的三种模式:

该服务调用包含三个可选的子功能,通常按顺序执行:-

认证: 验证接收到的比特流是否经过授权,与器件本身的安全设置是否匹配。这是安全编程的第一步。

-

编程: 执行实际的擦除和编程操作,将比特流写入目标区域。

-

验证: 在编程完成后,读取已编程的内容并与原始比特流进行比较,确保数据正确无误。

-

-

硬件设计关键要求:

-

电源供应: 编程期间,目标板必须为所有相关电源引脚提供稳定供电:

-

VDD: 芯片核心电压。

-

VDDIOx: 用于通信端口的 I/O 组电压。

x必须是对应通信端口(如USB)所在的 Bank 编号。这是硬件设计极易出错的地方! -

VPP & VPPNVM: 用于编程过程的专用编程电压。必须严格参考数据手册提供的推荐电压范围,否则可能损坏芯片!

-

-

引脚查询: 所有这些电源引脚的具体位置因封装而异,必须查阅 《SmartFusion2 and IGLOO2 Datasheet》 和对应的 封装引脚分配表 来确定。

-

-

I/O 状态:

-

编程期间各引脚的行为(是高阻、拉低还是保持弱上拉等)是系统级设计的重要考量。需要参考文档中 “编程期间器件组件状态” 章节来确保编程行为不会意外影响板上其他器件。

-

核心流程总结

这段描述的是:用户应用程序(运行在 Cortex-M3 上)如何通过调用系统控制器的 ISP 服务,来对自己所在的 SmartFusion2 芯片进行重新编程。这是一个“自我更新”的过程,涉及复杂的硬件协作。

详细要点解析

1. 角色与数据流

-

Cortex-M3 Processor: 执行用户应用程序。该应用程序负责通过某个通信接口(如 USB, UART)从外部(如远程服务器)获取新的编程比特流,并管理整个编程流程。

-

System Controller: 真正的“编程执行者”。它通过 COMM_BLK 硬件模块从 Cortex-M3 那里接收比特流(连续字节流),并执行认证、编程和验证等底层操作。

2. 关键风险与解决方案:eNVM 编程死锁

这是最精妙也是最关键的一点,解释了如何安全地更新正在运行的代码所在的内存。

-

风险场景: 如果 Cortex-M3 正在从 eNVM 中执行代码,而系统控制器接收到的比特流命令恰好要擦写/编程 eNVM 的同一块区域,就会发生冲突和死锁。这好比试图在飞机飞行途中更换它的发动机。

-

解决方案:

-

机制一(细粒度解锁): 系统控制器固件通过在原子操作之间释放 eNVM 的 HMASTLOCK 来避免死锁。HMASTLOCK 是一个硬件主锁信号,用于保证对存储器的原子性访问。暂时释放它允许 Cortex-M3 在编程间隙继续访问 eNVM 获取指令,从而避免了系统卡死。

-

机制二(代码搬迁 - 更安全的方法): 如果新比特流要更新 Cortex-M3 当前正在执行的代码区域,必须先将这段代码复制到 eSRAM 中,然后让 Cortex-M3 从 eSRAM 继续执行。这样,系统控制器就可以毫无冲突地重新编程整个 eNVM 区域。

-

3. 编程完成后的关键操作:双重复位

这是一个极易被忽略但至关重要的步骤,否则可能导致系统功能异常。

-

第一步 - 系统控制器复位: 编程完成后,系统控制器会自动复位整个器件,以使新的配置生效。

-

第二步 - 额外的系统复位(用户应用程序负责): 仅靠系统控制器的复位是不够的! 用户应用程序在 ISP 服务完成后,必须立即再触发一次完整的系统复位。否则,LSRAM 可能无法被正常访问。

-

如何实现第二次复位:

-

使用 Tamper Macro。这是一个可以从 Libero SoC 目录中实例化的硬件宏单元。

-

实现逻辑:

-

在用户逻辑(例如一个小的 FSM 状态机)中,在 ISP 完成后立即尝试访问 LSRAM。

-

如果访问被拒绝,则让该逻辑产生一个复位信号。

-

将这个复位信号连接到 Tamper Macro 的输入,从而触发一次可靠的系统级复位。

-

-

配置: 必须在 Tamper Macro 的配置窗口中启用 RESET 功能

-

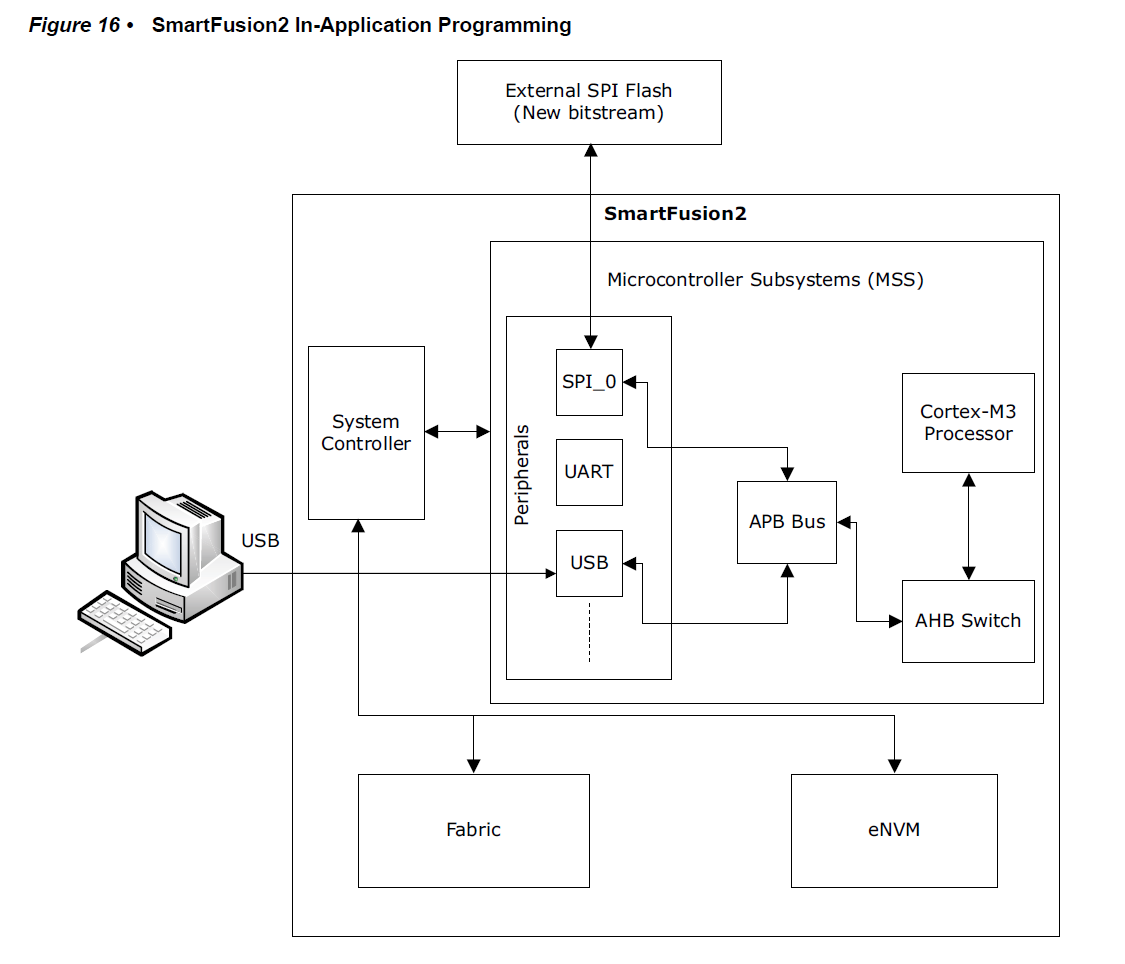

5、In-Application Programming

核心概念解释

在应用编程 (IAP) 是一种高级的编程方法,允许设备在保持一定程度运行的同时,为下一次启动准备一个新的编程映像。它是一个 “两步走” 的过程:

-

第一步(本文重点): 将新的比特流文件传输并存储到一个非易失性的中间存储区域(通常是外部SPI Flash)。在此阶段,当前的硬件设计仍在运行。

-

第二步(文中未提及,但可推断): 在后续的系统重启中,触发自动编程模式(即之前讨论的

FLASH_GOLDEN_N引脚被拉低的模式)。系统控制器会从那个外部SPI Flash中读取刚刚存放的新比特流,并用它来重新配置整个芯片。

第一步的详细区别:SmartFusion2 vs. IGLOO2

1. SmartFusion2 的实现方式

-

执行主体: Cortex-M3 处理器上运行的用户应用程序。

-

数据来源: 从任意的专用通信端口(如USB, UART, Ethernet等)接收新的比特流文件。例如,通过网络从远程服务器下载更新包。

-

存储动作: Cortex-M3 程序将接收到的比特流写入到连接在 MSS SPI_0 端口上的外部SPI Flash 存储器中。

-

关键限制: 系统控制器本身不具备直接写外部SPI Flash的能力。 这个写操作必须由Cortex-M3来完成。这解释了为什么SmartFusion2的IAP第一步离不开其内部的微控制器。

简单总结:SmartFusion2是靠“软件”(Cortex-M3固件)来完成新文件的下载和转存。

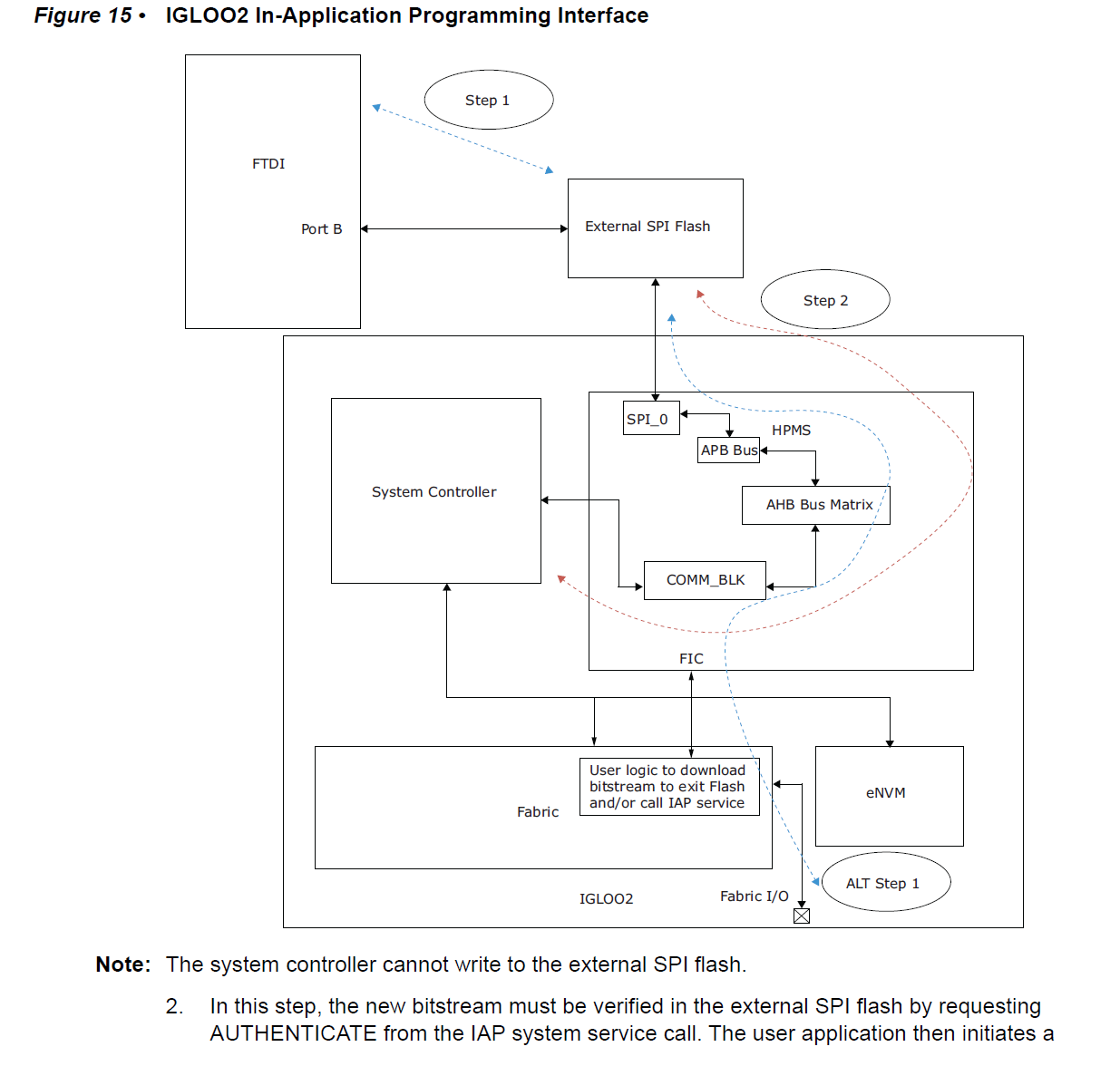

2. IGLOO2 的实现方式

IGLOO2 器件没有内部的Cortex-M3硬核处理器,因此它提供了两种替代方案来完成第一步:

-

方式一:通过外部编程器

-

执行主体: 外部编程器(如 FTDI 芯片提供的USB转SPI桥接功能)。

-

存储动作: 外部编程器直接通过SPI接口,将比特流文件写入到连接在 HPMS SPI_0 端口上的外部SPI Flash中。

-

特点: 此过程无需FPGA内部逻辑参与,甚至可以在FPGA未配置或部分功能运行的情况下进行。

-

-

方式二:通过FPGA逻辑(软核)

-

执行主体: FPGA 逻辑单元内部实现的软核微控制器(如 Microsemi 提供的 CoreABC 或其他用户自定义逻辑)。

-

数据来源: 新比特流通过FPGA的普通I/O引脚输入。例如,从一个SD卡接口、串口或其他自定义接口接收数据。

-

存储动作: 软核控制器接收数据后,通过逻辑控制,将数据推送到 HPMS SPI_0 主控制器,再由该控制器执行写入外部SPI Flash的操作。

-

特点: 这种方式更加“自力更生”,完全依靠FPGA自身的可编程逻辑能力来管理更新过程,无需外部编程工具。

-

简单总结:IGLOO2是靠“外部工具”或“硬件逻辑”来完成新文件的转存。

总结与应用场景

-

IAP的优势: 实现了“后台更新”。设备可以正常运作,同时在后台接收并保存一个新的设计版本。更新过程只有在设备下次重启时才会生效,大大提高了系统的可用性和可靠性。

-

选择依据:

-

SmartFusion2 利用其强大的内置Cortex-M3,非常适合处理复杂的通信协议(如TCP/IP)来获取更新包,是实现远程网络升级的理想选择。

-

IGLOO2 的方案则更灵活。方式一适合通过本地连接(如USB)进行更新;方式二则展现了FPGA的灵活性,可以用逻辑资源“模拟”出一个处理器来完成特定任务,适合成本敏感或接口特殊的应用。

-

总而言之,IAP的第一步是关于如何安全地将新数据送达外部SPI Flash,而两种器件的不同架构决定了实现这一目标的不同路径。

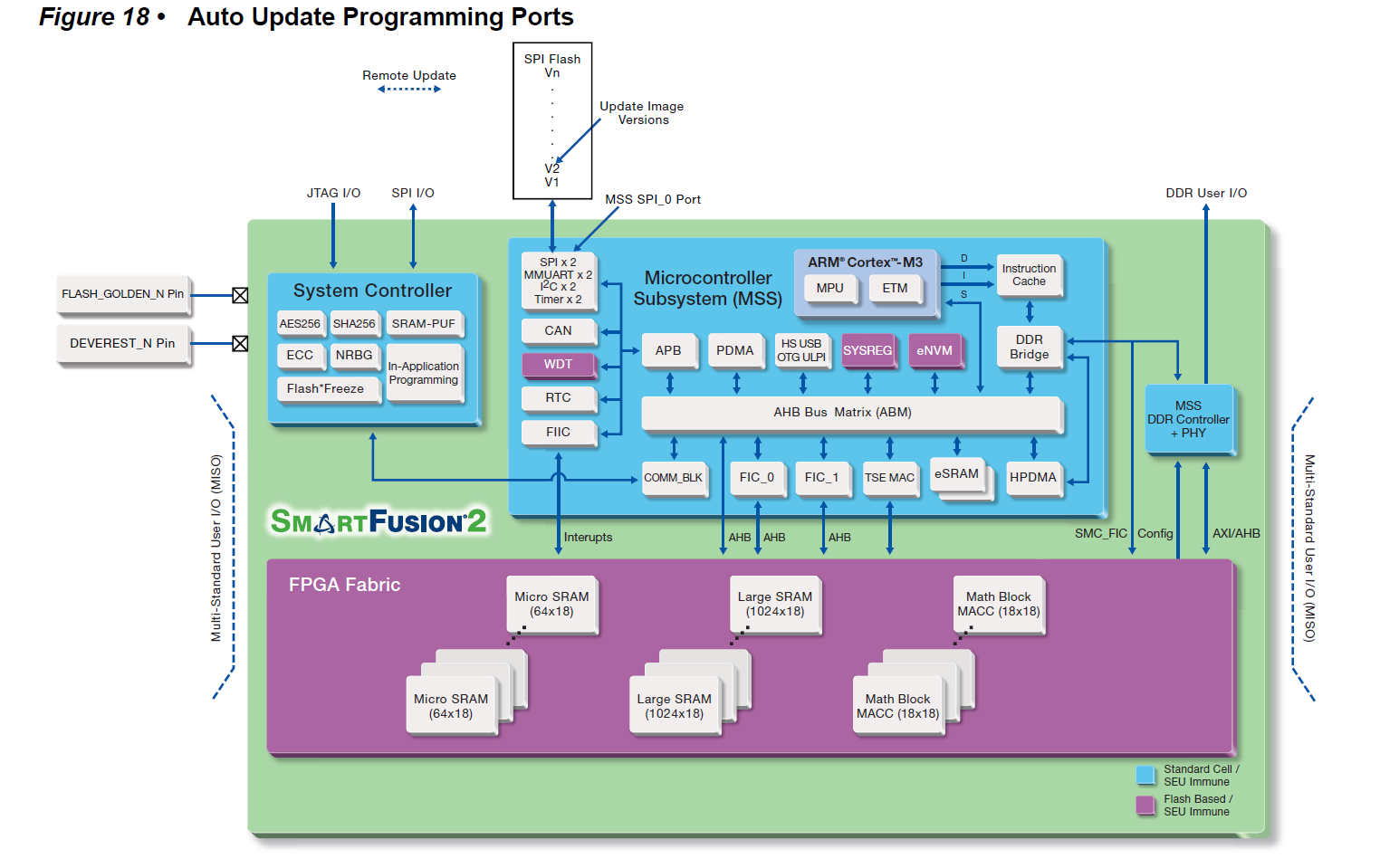

6、 Auto Update

核心概念解释

自动更新编程模式 是一种机制,允许 SmartFusion2 或 IGLOO2 器件在上电或复位时,自动检查连接在 SPI_0 端口上的外部Flash中是否存有版本更新的编程映像。如果有,则用这个新映像对自己进行编程。

简单比喻: 就像你的手机开机时,会自动检查是否有新版本的系统软件,并提示你升级。

工作流程与关键特性

-

触发条件:

-

系统 上电 或 复位引脚被触发。

-

-

更新源:

-

新的编程映像(比特流文件)必须预先存储在连接到器件 MSS/HPMS SPI_0 端口的外部SPI Flash中。

-

-

核心机制:版本控制

-

这是该模式与基本“自动编程模式”的关键区别。

-

器件会比较外部Flash中的“更新映像”版本与当前器件内已编程的“旧映像”版本。

-

只有在外部映像的版本号 > 内部映像的版本号时,自动更新过程才会继续执行。

-

这防止了意外的版本回退,并允许在Flash中存储多个版本的映像,由器件智能地选择最新的一个。

-

-

高级特性:SPI_0 端口共享

-

在通常的设计中,SPI_0 端口要么专用于自动编程,要么专用于用户逻辑。此模式支持共享。

-

如何实现: 可以在 FPGA 逻辑单元中设计一个多路复用器。

-

工作方式:

-

在启动和编程阶段,SPI_0 引脚由 MSS/HPMS 控制,用于读取外部Flash中的更新映像。

-

在正常操作阶段,一旦编程完成并进入用户模式,多路复用器可以将 SPI_0 引脚切换给用户逻辑中实现的SPI控制器使用(例如,用来连接另一个SPI外设)。

-

-

优势: 极大地提高了硬件资源的利用率,节省了宝贵的I/O引脚。

-

-

器件限制:

-

重要提示: 此 自动更新功能在 M2S/M2GL050 系列的器件中不受支持。这意味着如果您使用的是这些特定型号的芯片,将无法使用上述的版本检查和自动更新功能。

-

总结与应用场景

-

功能定位: 这是“自动编程模式”的增强版,增加了版本管理的智能性。

-

典型应用:

-

现场产品升级: 技术人员只需将存有新版本比特流的SPI Flash芯片替换到设备上,下次设备重启时就会自动完成升级,无需任何编程器。

-

双映像备份与恢复: 可以在Flash中存储一个“黄金”备份映像和一个更新的工作映像。如果工作映像损坏,可以通过某种方式(如按钮)触发复位,让器件自动回退到已知稳定的备份版本。

-

节省引脚: 通过SPI_0端口共享,可以在不增加芯片引脚的情况下,让系统既支持自动更新又能连接额外的SPI外设。

-

-

给工程师的建议:

-

实现参考: 文中提到的文档 DG0636 是极其重要的实践指南。它提供了一个完整的演示方案,详细说明了如何在设计中实现多路复用器、版本比较逻辑以及编程恢复等高级功能。

-

器件选型: 如果自动更新是项目的核心需求,避免选择 M2S/M2GL050 系列的器件。

-

硬件设计: 计划使用此功能时,在原理图设计阶段就需要规划好 SPI_0 端口共享的硬件电路,并在 Libero SoC 项目中编写相应的HDL代码来实现引脚复用逻辑。

-

核心要点解释

这段文字详细说明了使用 自动更新模式 的 前提条件 和 操作流程。

-

初始配置(一次性工作):

-

软件启用: 必须在 Libero SoC 软件的项目设置中明确启用自动更新功能。

-

首次编程: 必须将一个包含了自动更新配置信息的比特流文件通过常规方式(如JTAG)编程到 FPGA 中。这个初始编程让 FPGA 具备了检查自动更新的“能力”。

-

-

更新流程(每次更新时重复):

-

自动更新并非一劳永逸。每次想要更新时,都需要准备外部 SPI Flash。

-

两步编程 SPI Flash:

-

a. 将新的比特流文件(

.bin/.jbc)写入 SPI Flash。 -

b. 将一个称为 “SPI 目录” 的元数据文件写入 SPI Flash 的特定位置。这个目录至关重要,它告诉系统控制器:“新的比特流在哪里”以及“它的版本号是多少”。

-

-

系统控制器在上电时,会先读取这个 SPI 目录来获取信息,而不是盲目地读取整个Flash。

-

-

版本控制与安全认证:

-

系统控制器会比较 SPI 目录中的版本号与芯片内部当前的版本号。只有发现新版本时,才会启动编程。

-

整个流程包含认证步骤。如果 SPI Flash 是空的,或者里面的数据不是合法的比特流(例如缺少目录或认证失败),更新过程会安全地中止,从而防止对芯片进行错误或恶意的编程。

-

总结与给工程师的建议

-

这不是一个全自动的过程: 虽然名为“自动”,但它指的是检测和编程过程的自动,而更新映像和目录的准备与烧录仍需人工或外部系统干预。

-

SPI 目录是关键: 忘记烧录 SPI 目录或目录信息错误是导致自动更新失败的常见原因。

-

安全机制: 认证失败后中止编程是一种保护机制,意味着如果你的更新文件准备不正确,最坏的情况就是更新失败,而不会把器件“变砖”。

-

后续步骤: 文中提到的 “Configuring the Device for Auto Update” 部分是 Libero SoC 软件中的具体操作指南,是实现此功能必须遵循的步骤。

核心内容解释

1. 更新失败时的行为(安全机制)

-

原文: "...the device is not changed, therefore the device boot sequence continues, and the existing user design powers up."

-

解释: 这是一个非常重要的安全特性。如果自动更新过程因任何原因失败(例如,SPI Flash为空、比特流认证失败、版本不更高),器件内部已有的编程内容不会被改变或破坏。

-

结果: 器件会终止更新尝试,继续正常的启动流程,最终正常启动并运行原有的、未被更改的用户设计。这确保了系统不会因为一次失败的更新尝试而“变砖”,提高了可靠性。

2. 自动更新期间的特定I/O引脚行为(硬件设计关键!)

-

原文: "Four SPI slave select pins... drive high during auto programming... The remaining SPI_0 pins are tristated with weak pull up."

-

解释: 在自动更新过程中,芯片系统控制器会强制控制 SPI_0 端口引脚的状态,这与用户设计中的设置无关。

-

SS4, SS5, SS6, SS7: 这四个专用的从选择引脚(除005和010小封装器件外)会被驱动为高电平。

-

其他 SPI_0 引脚: 如 MOSI, MISO, SCLK 等,会处于高阻态(三态),并使能内部弱上拉。

-

-

重要设计约束:

-

"These four pins... must not be used as control pins."

-

这意味着,在您的硬件电路设计中,绝对不可以将

SS4至SS7这四个引脚用于控制其他外部芯片(如作为使能、复位或中断信号)。 -

因为它们在每次上电/复位后的短暂自动更新检查期间都会被强制拉高,这可能会意外地使您的外设使能或复位,导致系统行为异常。

-

3. I/O 电平的参考基准

-

原文: "The I/O level and drive strength are based on the previous settings programmed into the device."

-

解释: 虽然引脚状态(驱动高、高阻)由系统控制器强制决定,但这些信号的电压电平(例如是3.3V还是1.8V)和驱动强度(驱动电流大小)则取决于之前成功编程到器件中的配置。这些配置是在 Libero SoC 中为I/O Bank设置的

VDDIOx电压和驱动强度参数。

4. 电源要求(硬件设计关键!)

-

原文: "The target board must provide power to the VPP, VPPNVM, VDD, and VDDIOx (where x = SPI_0 interface bank number) pins."

-

解释: 要让自动更新功能正常工作,目标板(您的电路板)必须为以下引脚提供稳定、符合规范的电源:

-

VDD: 芯片核心电压。

-

VDDIOx: 特别重要! 这里的

x必须是 SPI_0 端口所在的那个 I/O Bank 的编号。必须为这个Bank供电,SPI_0 端口才能正常工作。 -

VPP & VPPNVM: 芯片内部编程电压。必须严格遵循数据手册的电压值要求,否则可能永久损坏芯片!

-

5. 必须查阅的文档

-

电压和引脚位置: 所有电源引脚的具体电压要求和物理位置(引脚号)因器件型号和封装而异。必须查阅 《SmartFusion2 and IGLOO2 Datasheet》 和对应的 封装引脚分配表。

-

I/O 状态详情: 关于编程期间所有引脚(而不仅仅是SPI_0)的详细状态(高阻、拉低、输出高),需要参考文档中 “编程期间器件组件状态” 这一节。这对于保证编程期间整个电路板的稳定至关重要。

总结与给工程师的强烈建议

-

可靠性设计: 自动更新模式具有内置的失败保护机制,更新失败不会影响现有功能。

-

硬件设计禁忌: 切勿将

SS4至SS7引脚用于任何关键的控制信号线。它们在上电期间的行为不受用户设计控制。 -

电源设计是重中之重:

-

确保 VDDIOx(x 为 SPI_0 所在的 Bank)在编程期间持续稳定供电。

-

绝对确保 VPP/VPPNVM 的电压值完全、绝对符合数据手册的规定范围,这是防止硬件损坏的关键。

-

-

养成查阅官方文档的习惯: 在进行任何硬件设计或调试之前,必须仔细阅读数据手册和用户指南中的相关章节。引脚分配、电压值和I/O状态都是不可凭猜测确定的参数。

重点:Use of Flash Freeze Mechanism in Device Programming

核心概念解释

1. F*F 模式概述

-

触发模式: 当使用 SPI 从模式、IAP、自动更新 和 MSS ISP 对这些器件进行编程时,芯片会自动进入 FlashFreeze (FF) 模式。

-

模式行为:

-

I/Os 被禁用: 用户逻辑单元控制的普通I/O引脚不再受你的设计控制。

-

逻辑单元断电: FPGA 的可编程逻辑部分被断电以节省功耗并确保编程安全。

-

-

目的: 冻结用户逻辑,使其在编程过程中不会产生任何意外的信号输出,从而避免对板上其他器件造成干扰。

2. I/O 引脚状态配置(Libero SoC 设置)

这是硬件工程师必须关注的重点,它决定了编程期间引脚的电平状态,直接影响电路板行为。

-

配置工具: 在 Libero SoC 软件的 I/O Editor 中,可以为每个引脚或每组引脚设置其在 F*F 模式下的状态。

-

两种选项:

-

Tristate (三态): 引脚处于高阻态,并启用弱上拉电阻。这是最常用、最安全的选项,避免引脚悬空。

-

Last known value (最后已知值): 这是一个“智能”选项。系统会记住该引脚在进入 F*F 模式之前的状态,并据此为其附加一个弱保持力。

-

如果之前是输出高电平,则在 F*F 模式下变为高阻态 + 弱上拉。

-

如果之前是输出低电平,则在 F*F 模式下变为高阻态 + 弱下拉。

-

-

设计意义: 你必须根据外部电路的需求来谨慎选择。例如,如果一个引脚连接到一个需要被禁用的外设的使能端,你就需要设置一个能确保该外设被禁用的状态(通常是高阻加上拉或下拉)。

-

3. 时钟管理(固件工程师必须注意)

这是针对 SmartFusion2 器件在 IAP/MSS ISP 模式下的重要细节,关系到编程性能和可靠性。

-

自动切换: 一旦进入 F*F 模式,系统控制器会自动将 MSS 的时钟源切换到一个 待机时钟。

-

待机时钟选项: 在 Libero SoC 的 Configure Flash Freeze 菜单中,待机时钟可以配置为 1 MHz 或 50 MHz。这通常是为了在低功耗和基本性能之间做权衡。

-

关键要求: 然而,为了确保 IAP/MSS ISP 编程过程高效可靠(尤其是通过通信端口接收数据时),Cortex-M3 需要更快的时钟速度。

-

固件职责: 因此,在用户固件请求系统服务(即调用编程功能)之前,它必须手动地将 MSS 的时钟源从 1 MHz 切换回 50 MHz(前提是 Libero 中配置的待机时钟是 1 MHz)。

-

目的: 这确保了在接下来的编程数据流传输和处理过程中,Cortex-M3 有足够的处理能力,避免因时钟过慢而导致通信超时或编程失败。

总结与给工程师的建议

-

硬件设计 (I/O 状态):

-

在 Libero SoC 中完成引脚分配后,必须仔细检查并配置 I/O Editor 中的 Flash Freeze 设置。

-

评估每个引脚在编程期间的状态对板级电路的影响。默认使用“Tristate”通常是最安全的选择,除非有特殊理由需要保持某个电平。

-

-

固件开发 (时钟管理):

-

如果为 SmartFusion2 开发支持 IAP/MSS ISP 功能的固件,必须在调用编程服务前添加切换时钟的代码。

-

检查 Libero 项目中的 Configure Flash Freeze 设置。如果待机时钟设为 1 MHz,则固件需在发起编程前将时钟提速至 50 MHz 以保证性能。

-

-

系统可靠性:

-

正确配置这些选项是保证编程过程稳定、不干扰板卡其他部分、并成功完成的关键。忽略这些细节可能导致编程失败或系统行为异常。

-

简而言之,F*F 模式 是一种受控的“休眠”状态,而 Libero 中的配置和用户的固件需要共同协作,以确保在这种状态下,芯片的行为符合整个系统的要求。

浙公网安备 33010602011771号

浙公网安备 33010602011771号