A3P250 复位信号测试

测试 OK!

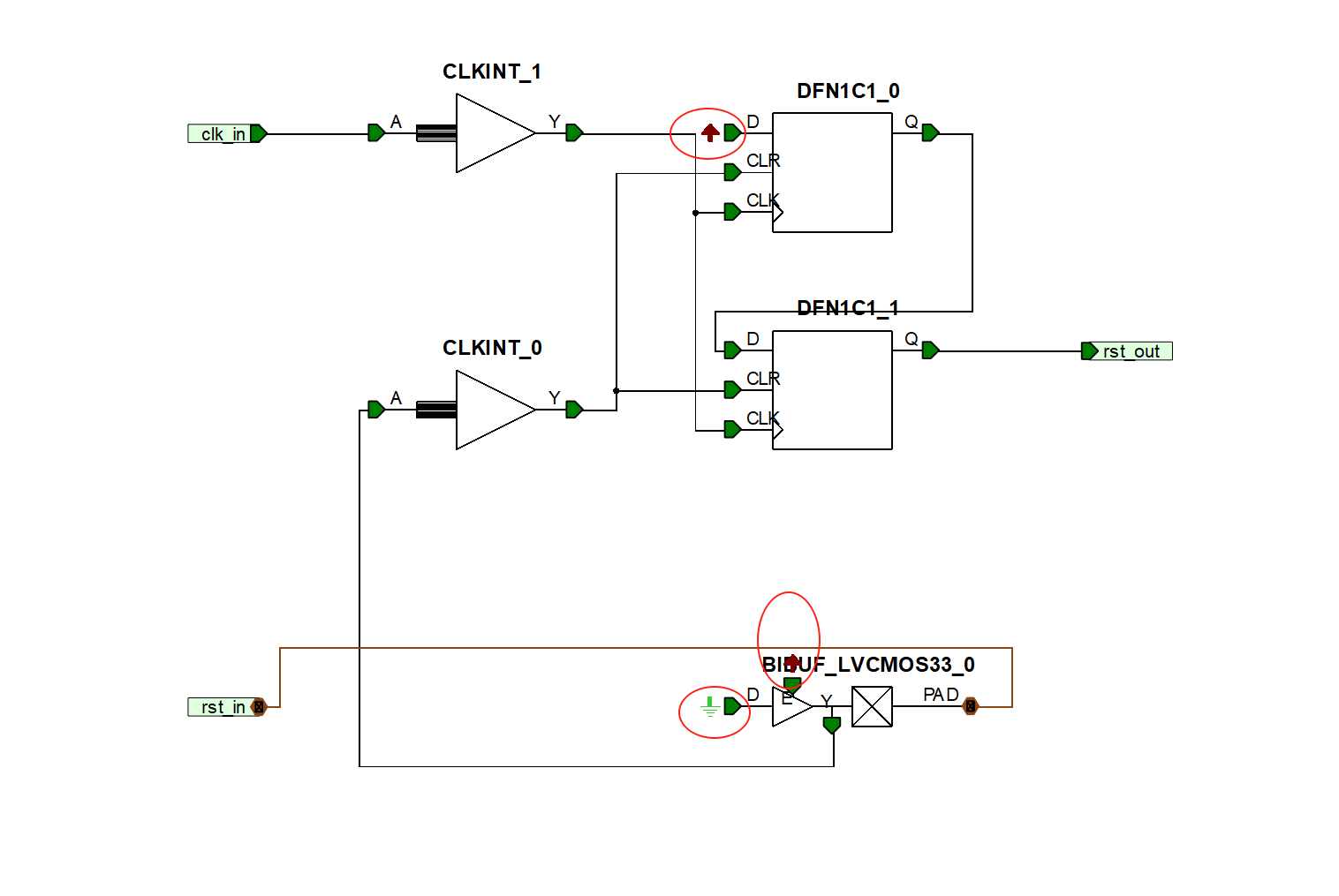

module led( clk_40mhz, rst_n, led_1 ); input clk_40mhz; // pin62 input rst_n; // pin64 output led_1; // pin13 reg led_reg; reg [31:0] tick_cnt = 32'd0; always @(posedge clk_40mhz or negedge rst_n) begin if(!rst_n) begin tick_cnt <= 32'd0; led_reg <= 1'd0; end else begin tick_cnt <= tick_cnt + 32'd1; if(tick_cnt>=32'd40000000) begin //tick_cnt <= 32'd0; led_reg <= 1'd1; end end end assign led_1 = led_reg; endmodule

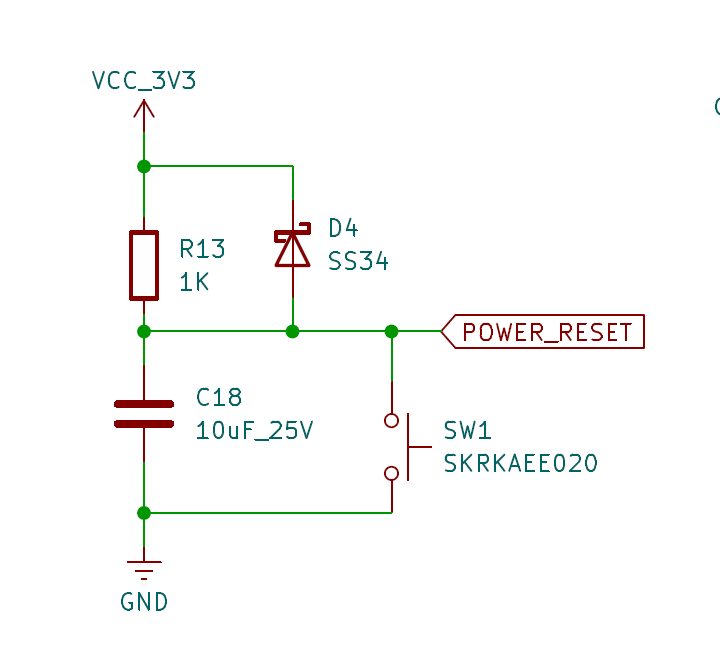

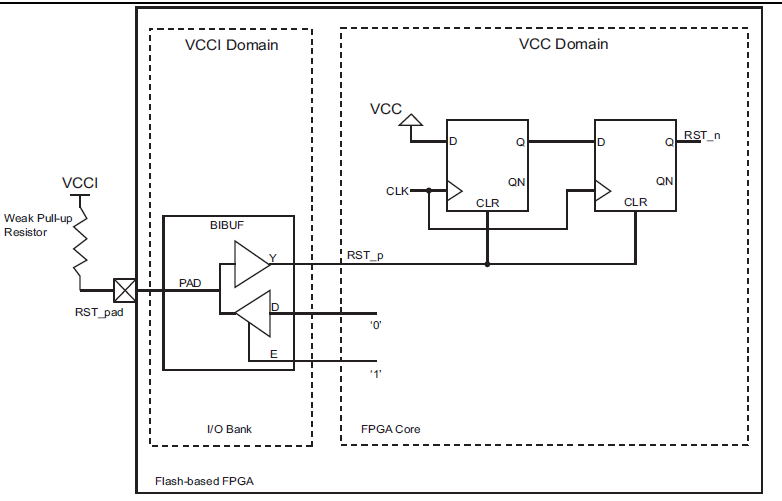

上面的复位信号不稳定,使用官方 上电复位信号,比较稳定:

https://ww1.microchip.com/downloads/aemDocuments/documents/FPGA/ApplicationNotes/ApplicationNotes/lpf_ac380_an.pdf

浙公网安备 33010602011771号

浙公网安备 33010602011771号