verilog spi slave 错误记录三

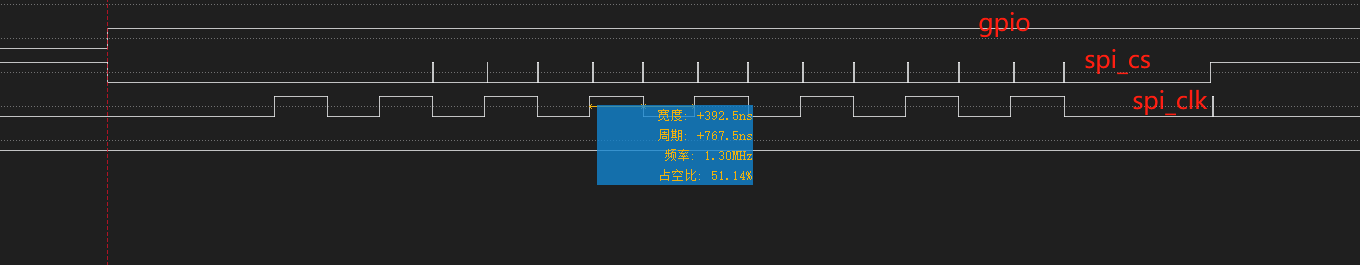

加上 spi_clk , 使用 gpio 观察 代码 执行逻辑 !!!

/////////////////////////////////////////////////////////////////////////////////////////////////// // Company: <Name> // // File: spi_slave.v // File history: // <Revision number>: <Date>: <Comments> // <Revision number>: <Date>: <Comments> // <Revision number>: <Date>: <Comments> // // Description: // // <Description here> // // Targeted device: <Family::SmartFusion2> <Die::M2S010S> <Package::144 TQ> // Author: <Name> // /////////////////////////////////////////////////////////////////////////////////////////////////// `timescale 1ns / 1ps module spi_slave( output wire led_1, // pin_129 / 2.5V output wire mod1_gpio_0, // pin_93 / 3.3V input wire spi_cs, // spi_cs / pin_90 / MOD1-4 input wire spi_clk, // spi_clk / pin_83 / MOD1-2 input wire spi_mosi, output wire spi_miso ); // spi_miso / pin_82 / MOD1-7 reg spi_miso_reg; reg led_reg = 1'b0; always @( posedge spi_clk or negedge spi_cs) begin if(!spi_cs) begin led_reg <= 1'd1; end else begin led_reg <= 1'd0; end end assign spi_miso = spi_miso_reg; assign led_1 = led_reg; assign mod1_gpio_0 = led_reg; endmodule

不得不说, FLASH FPGA 编程,怎么这么慢!!!,,,波形抓取如下:

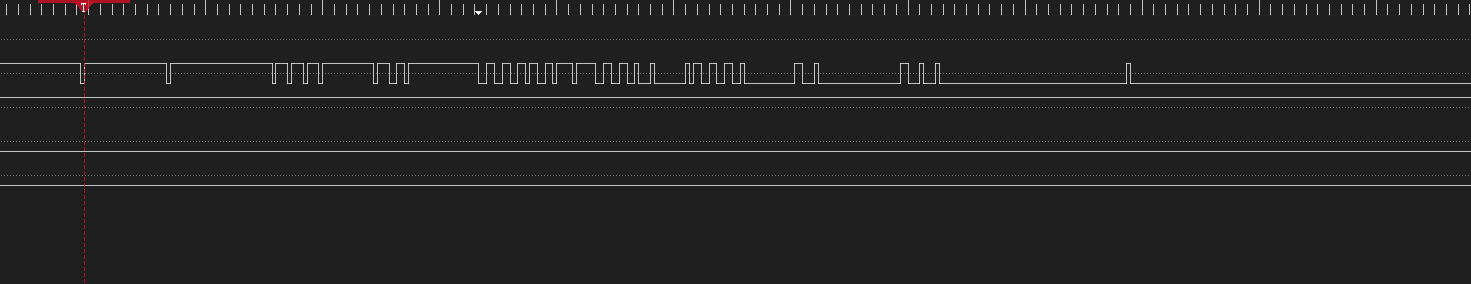

尝试理解 : 这样 只执行了一次, 因为 SPI_CLK 触发时 和 SPI_CS 下降沿触发时, cs 永远是 low ,因此只执行 第一个分支代码, gpio0 输出永远是 高!!

现在更改代码, if 判断 不是 spi_cs 而是 spi_clk 信号, 看看 结果如何?

/////////////////////////////////////////////////////////////////////////////////////////////////// // Company: <Name> // // File: spi_slave.v // File history: // <Revision number>: <Date>: <Comments> // <Revision number>: <Date>: <Comments> // <Revision number>: <Date>: <Comments> // // Description: // // <Description here> // // Targeted device: <Family::SmartFusion2> <Die::M2S010S> <Package::144 TQ> // Author: <Name> // /////////////////////////////////////////////////////////////////////////////////////////////////// `timescale 1ns / 1ps module spi_slave( output wire led_1, // pin_129 / 2.5V output wire mod1_gpio_0, // pin_93 / 3.3V input wire spi_cs, // spi_cs / pin_90 / MOD1-4 input wire spi_clk, // spi_clk / pin_83 / MOD1-2 input wire spi_mosi, output wire spi_miso ); // spi_miso / pin_82 / MOD1-7 reg spi_miso_reg; reg led_reg = 1'b0; always @( posedge spi_clk or negedge spi_cs) begin if(spi_clk) begin // 修改了 这里 led_reg <= 1'd1; end else begin led_reg <= 1'd0; end end assign spi_miso = spi_miso_reg; assign led_1 = led_reg; assign mod1_gpio_0 = led_reg; endmodule

这次很奇怪 , LED 上电就是灭的, 上电应该 亮灯才对, 因为 LED1 是低电平点亮!!!

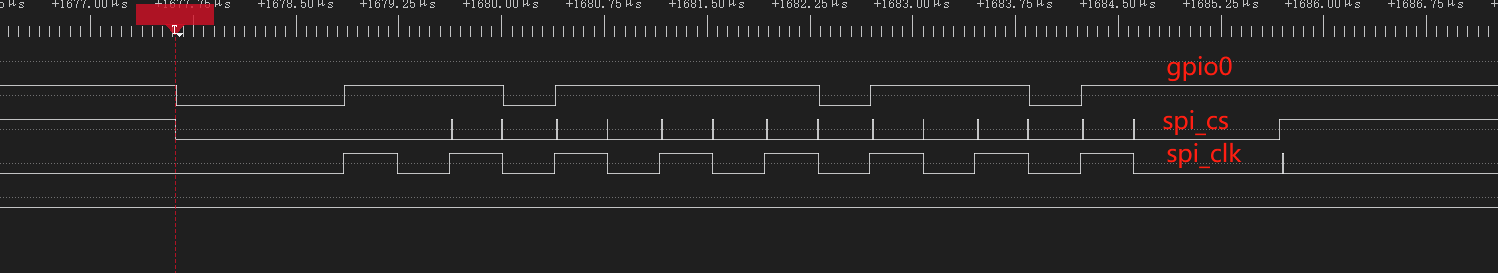

复位抓取波形: GPIO0 输出 乱糟糟!!!

SPI 抓取波形;

spi_cs 下降沿信号, 为什么 执行 led_reg <= 1'd0,这个语句 ??????????

spi_clk 上升沿信号, 为什么执行 led_reg <= 1'd1; 这个语句 ????????????

上面这么写代码,可能不符合逻辑, 因此 换一种写法:

`timescale 1ns / 1ps module spi_slave( output wire led_1, // pin_129 / 2.5V output wire mod1_gpio_0, // pin_93 / 3.3V input wire spi_cs, // spi_cs / pin_90 / MOD1-4 input wire spi_clk, // spi_clk / pin_83 / MOD1-2 input wire spi_mosi, output wire spi_miso ); // spi_miso / pin_82 / MOD1-7 reg spi_miso_reg; reg led_reg = 1'b0; always @( posedge spi_clk or negedge spi_cs) begin if(!spi_cs) begin led_reg <= ~led_reg; // 修改了 这里 end else begin led_reg <= 1'd0; end end assign spi_miso = spi_miso_reg; assign led_1 = led_reg; assign mod1_gpio_0 = led_reg; endmodule

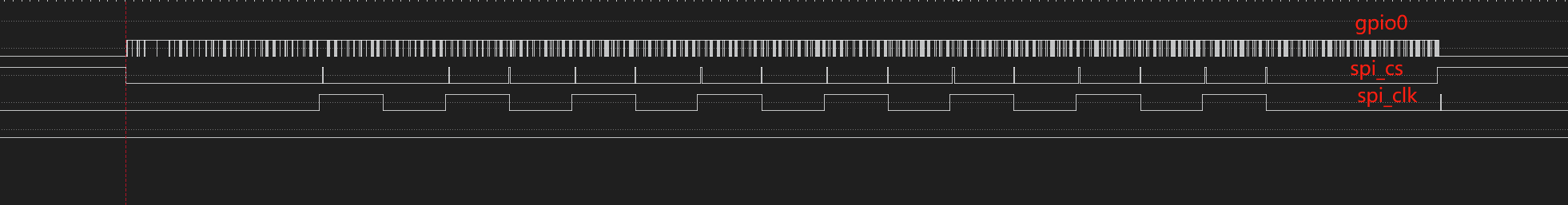

波形抓取如下:

这个感觉逻辑也不对,因为 led_reg <= ~led_reg; 这句代码 应该只是 在 spi_cs 下降沿 或者 spi_clk 上升沿的时候触发, 现在 是 触发很多次!!!

浙公网安备 33010602011771号

浙公网安备 33010602011771号