verilog spi slave 错误记录二

使用 cs 引脚 触发 , 使用 gpio0 输出触发信号,使用 逻辑分析仪 观察输出信号, 了解 FPGA 工作逻辑!!! 我觉得这个功能 ,类似 C代码的 printf 啊 !!!

/////////////////////////////////////////////////////////////////////////////////////////////////// // Company: <Name> // // File: spi_slave.v // File history: // <Revision number>: <Date>: <Comments> // <Revision number>: <Date>: <Comments> // <Revision number>: <Date>: <Comments> // // Description: // // <Description here> // // Targeted device: <Family::SmartFusion2> <Die::M2S010S> <Package::144 TQ> // Author: <Name> // /////////////////////////////////////////////////////////////////////////////////////////////////// `timescale 1ns / 1ps module spi_slave( output wire led_1, // pin_129 / 2.5V output wire mod1_gpio_0, // pin_93 / 3.3V input wire spi_cs, // spi_cs / pin_90 / MOD1-4 input wire spi_clk, // spi_clk / pin_83 / MOD1-2 input wire spi_mosi, output wire spi_miso ); // spi_miso / pin_82 / MOD1-7 reg spi_miso_reg; reg led_reg = 1'b0; always @( negedge spi_cs) begin if(!spi_cs) begin led_reg <= ~led_reg; end end assign spi_miso = spi_miso_reg; assign led_1 = led_reg; assign mod1_gpio_0 = led_reg; endmodule

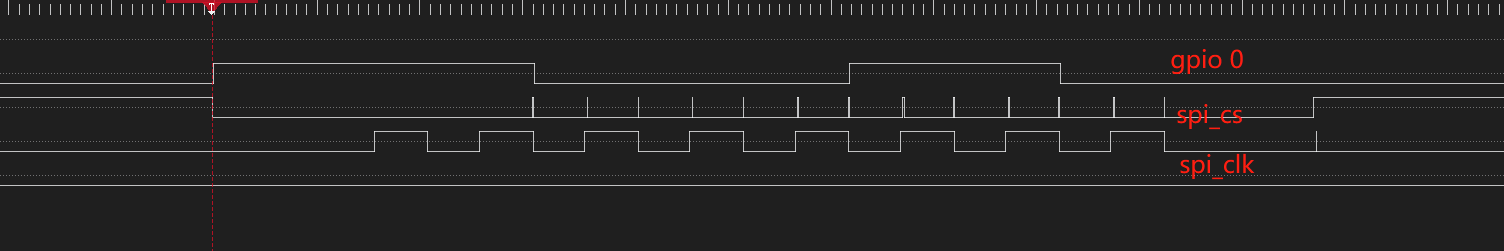

波形抓取如下:

分析 不理解,没有按照逻辑执行, 逻辑分析仪增加 spi_clk 监视后发现:

发现 SPI_CS 在传输时,存在毛刺, 我使用 杜邦线连接,难道影响了信号完整性???

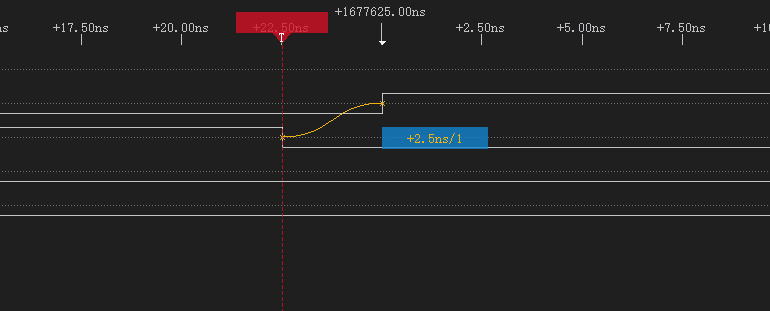

如何在代码里, 消除这些毛刺 ?

可通过逻辑分析仪发现, spi_cs 引脚下拉2.5ns 后, gpio0 有动作,如下图:

浙公网安备 33010602011771号

浙公网安备 33010602011771号