zynq verilog 编写 spi slave 代码 错误记录 一

`timescale 1ns / 1ps module spi_slave( input wire spi_clk_0, // spi_cs input wire spi_clk_1, // spi_clk input wire spi_mosi, output wire spi_miso, output version_reg, output tx_cnt ); // 定义一个寄存器变量 reg spi_miso_reg; // 定义一个寄存器 版本号 reg [7:0] version_reg; // 定义一个变量,用于计算传输数据的长度 reg [2:0] tx_cnt; // spi_clk_0 拉低时 version_reg 设置为 8'h55 // spi_clk_0 拉低时 tx_cnt 清零 always @(posedge spi_clk_1 or negedge spi_clk_0) begin if(!spi_clk_0) begin if(!spi_clk_1) begin version_reg <= 8'h55; tx_cnt <= 3'd0; end else begin spi_miso_reg <= version_reg[7-tx_cnt]; tx_cnt <= tx_cnt + 3'd1; end end else begin spi_miso_reg <= 1'b1; end end assign spi_miso = spi_miso_reg; endmodule

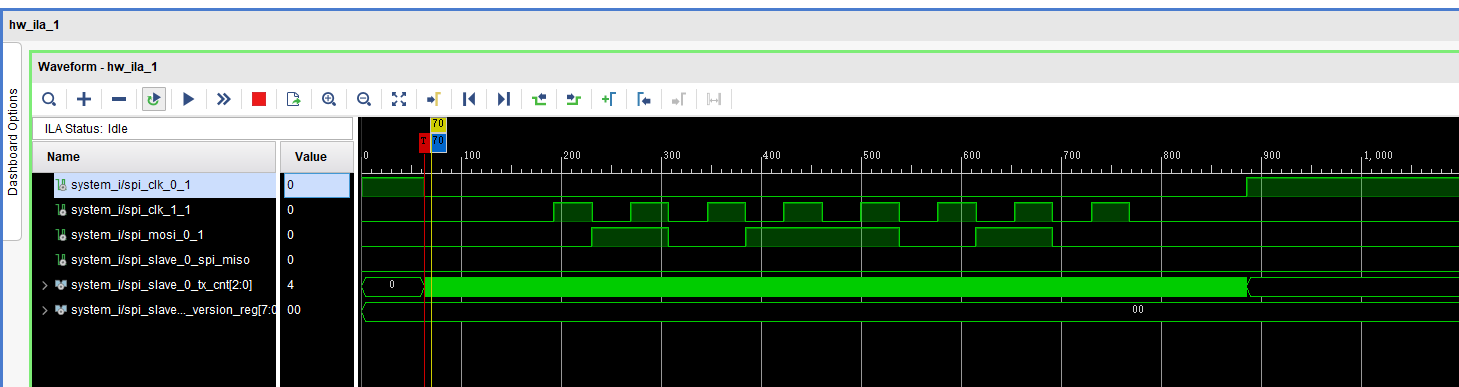

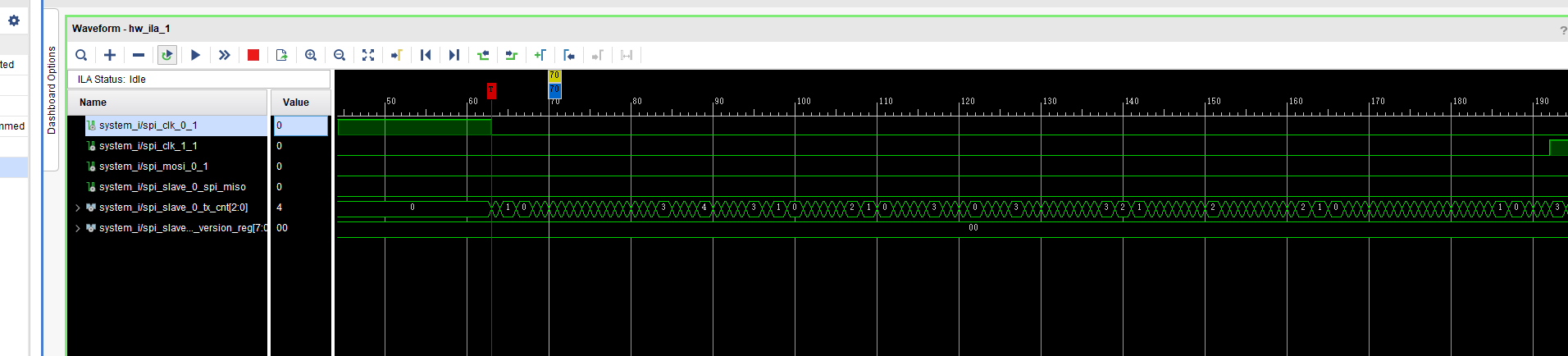

tx_cnt 放大后, 波形乱码, 奶奶腿

是什么问题 那

浙公网安备 33010602011771号

浙公网安备 33010602011771号