ZYNQ AXI UARTLite v2.0 中断触发逻辑

1、 使用 官方 提供的 库, 太繁琐了;

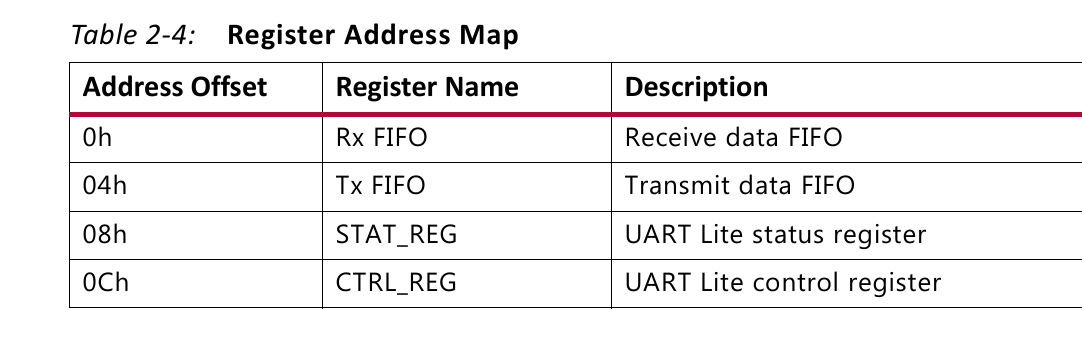

2、手写寄存器 ,编程 , 发现 就 4个寄存器,非常简单 ,定义如下 :

官方手册:https://docs.amd.com/v/u/en-US/pg142-axi-uartlite

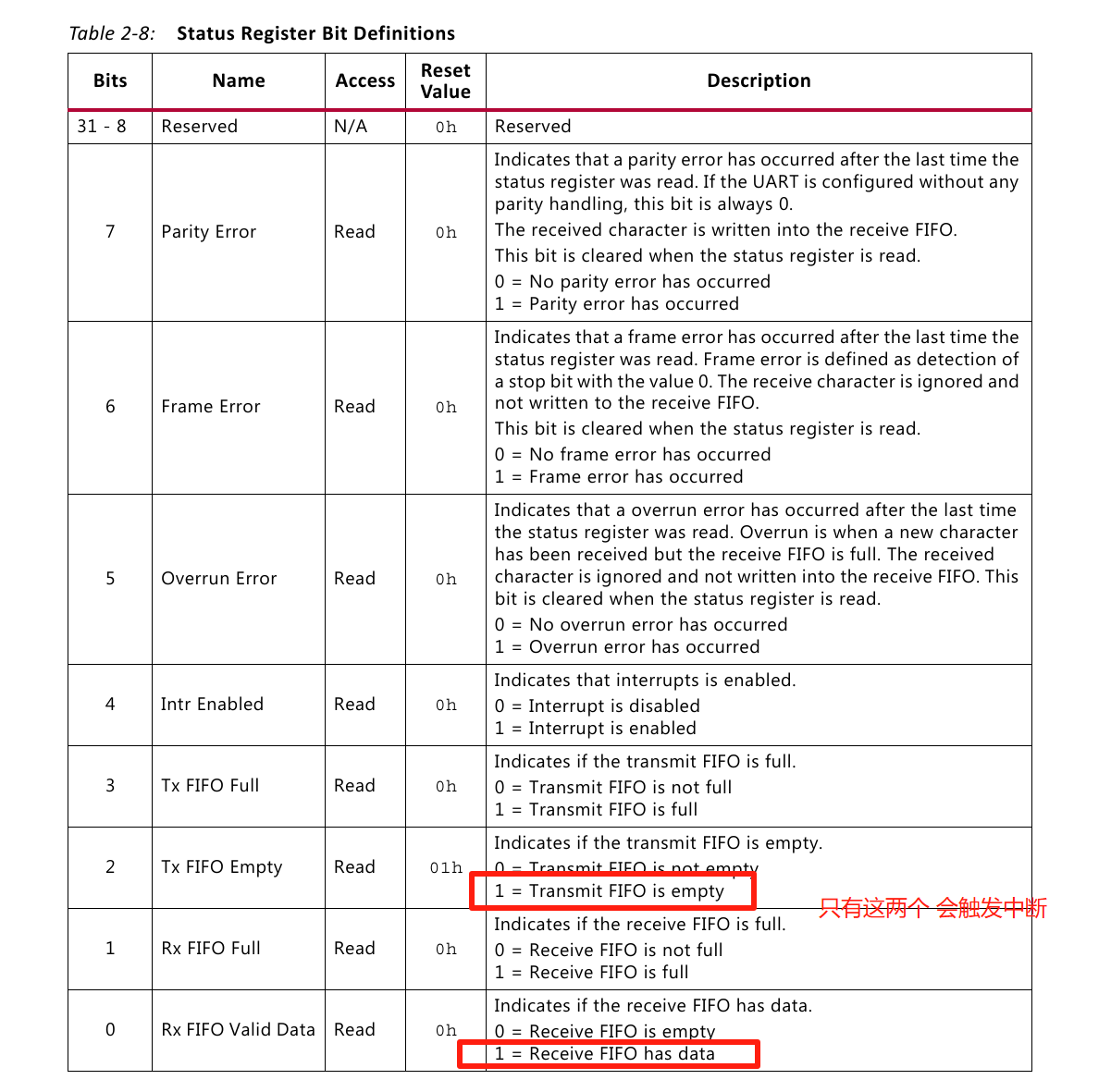

3、 什么情况下 会触发中断

Interrupt Control - The AXI UART Lite core provides interrupt enable/disable control. If interrupts are enabled, a rising-edge sensitive interrupt is generated when the receive FIFO becomes non-empty or when the transmit FIFO becomes empty.

实际测试 :

当接收完成1个字节, 在中断里读取状态寄存器值 = 0x15;

当发送完成1个字节,在中断里读取状态寄存器值 = 0x14;

浙公网安备 33010602011771号

浙公网安备 33010602011771号