ESD原理以及射频防护设计

1、ESD概念

ESD(Electro-Static discharge )是广泛存在于你我身边的自然现象,小时候上自然课就学过摩擦生电。而静电对于工业界来说有时候是很头疼的东西,世界上最大的飞艇兴登堡号就是因为静电原因坠毁的。随着IC的规模越来越大,线宽越来越小,芯片也越来越娇贵,EOS(Electrical Over Stress )失效问题也日益严重,而ESD是EOS失效的主要原因,ESD防护也成为ICdesigner需要考虑的问题,而其中模拟IC因为其自身特性,需要更加注重ESD防护。

ESD防护在模拟IC设计中是很重要的一环,但是国内IC企业很少有专人去负责,所以本文将对ESD的原理和分类进行由浅入深的总结,希望无论是IC设计人员还是硬件工程师都不需要去翻阅大量的资料,而对ESD有一个认知。

2、ESD的分类

- 1.发生在芯片上PCB板前的过程中(生产 、封装、运输、销售、上板)这类ESD事件完全需要由芯片自己承受。业界对于这类ESD事件进行了分类主要分为三种模型:HBM(Human body Model),MM(Machine Model),CDM(Charged Device Model),SDM(socket device Model),顾名思义HBM模型是仿真人体接触模型(就是憨憨用手直接摸芯片),MM模型仿真机械接触,CDM模型是仿真芯片因为摩擦或者热等原因内部集聚了电荷,然后通过探针或者封装等途径从芯片内部放电到外部,起初CDM模型有两种分类,其中一种是non-socket device Model,是在测试的时候探针直接扎入PAD,而另一种socket device Model是测试的时候把芯片放入一个基座然后探针扎入基座,后来这两种方式的结果差距有些大,就把SDM单独拎出来了。目前还是以MIL-883作为主流标准。

- 2.芯片已经在PCB上电工作后发生的ESD事件。这类ESD事件主要包含:接触放电,空气放电,热插拔,浪涌这几种。这类ESD事件普遍能量大,时间久。但是与前一类最大的区别,这类PCB上电后的ESD事件,芯片可以靠外援,通过TVS或者ESD阵列芯片进行泄放,芯片本身在外界的帮助下可以不需要承受静电流。而这类ESD事件的详规主要在IEC61000-4-2和IEC61000-4-5中,目前国内硬件工程师主要解决这方面的ESD事件。

3、ESD的原理

- 1.HBM模型。

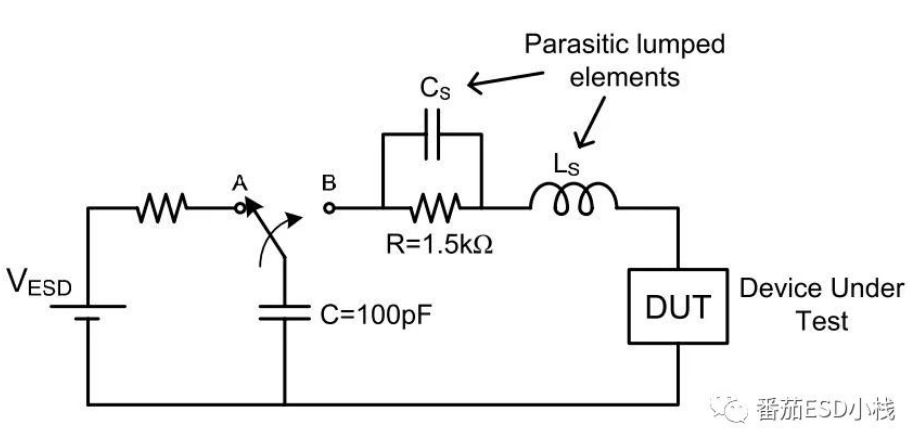

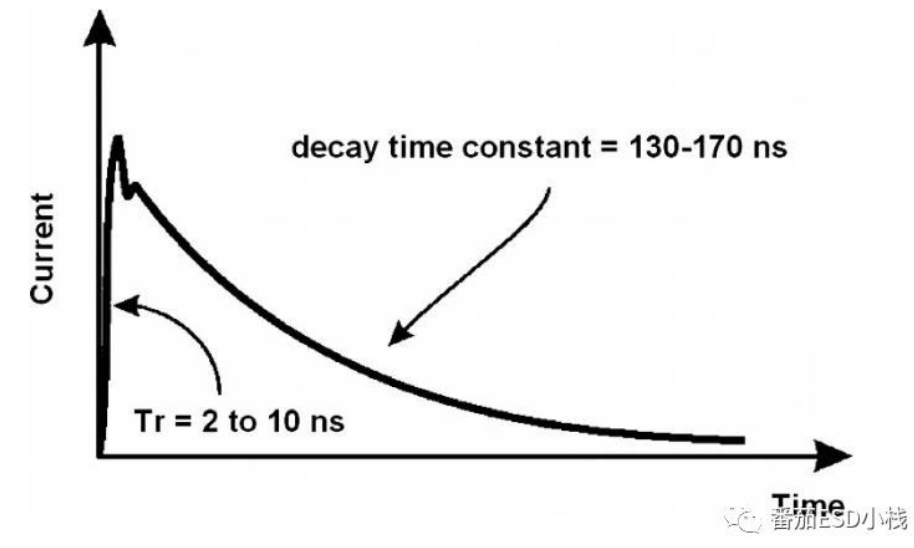

图1.HBM放电模型

图2.HBM放电波形

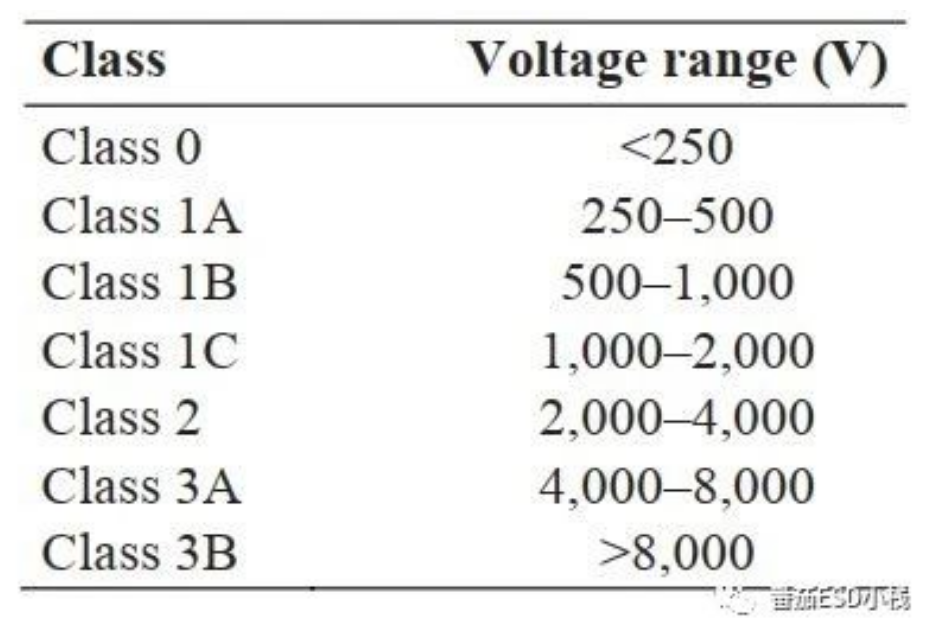

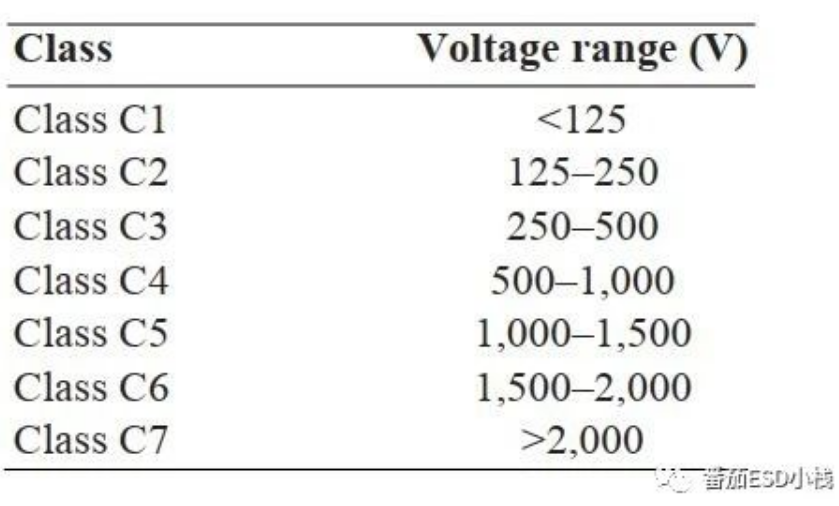

图3.HBM等级

一般以电压来表达HBM等级,不同的IC根据使用场景对于HBM等级有不同的要求。而随着越来越规范的生产制度,HBM模型造成的失效比例在一步步的降低。

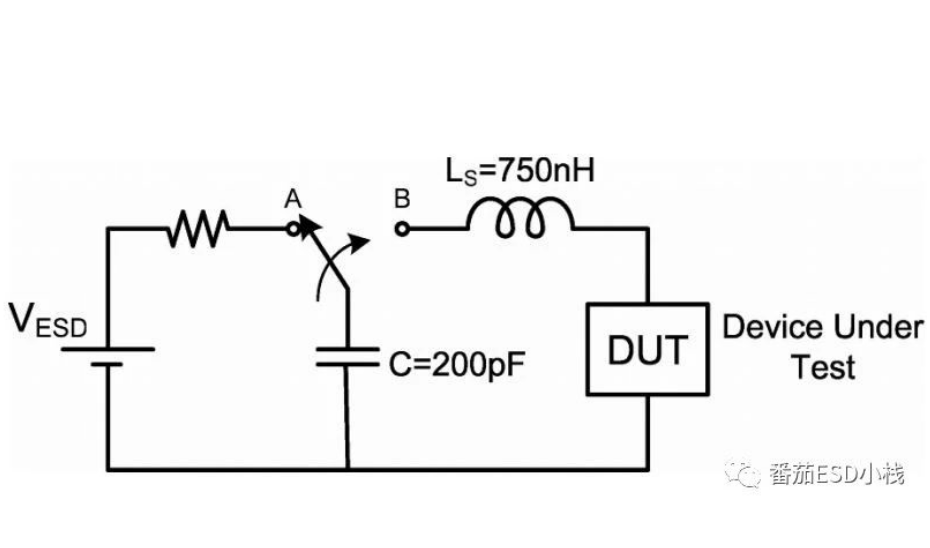

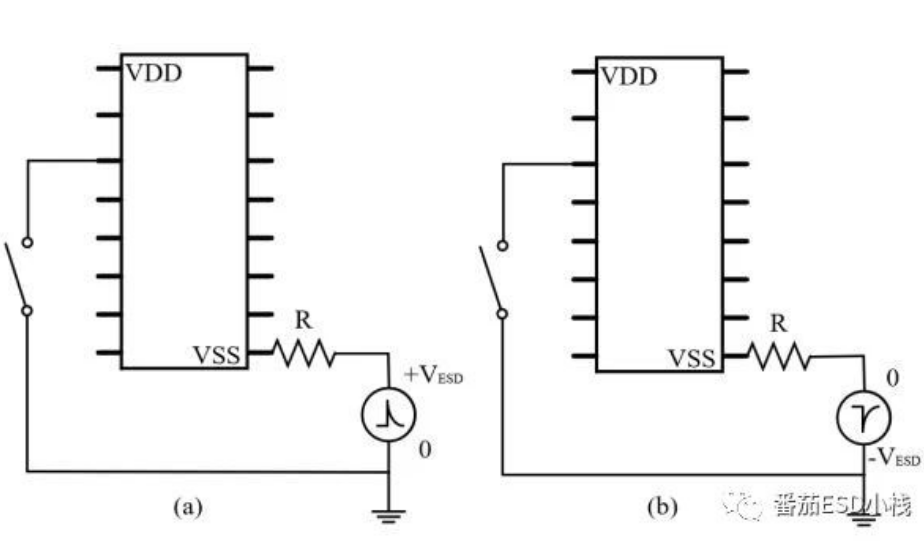

图4.HBM测试模型

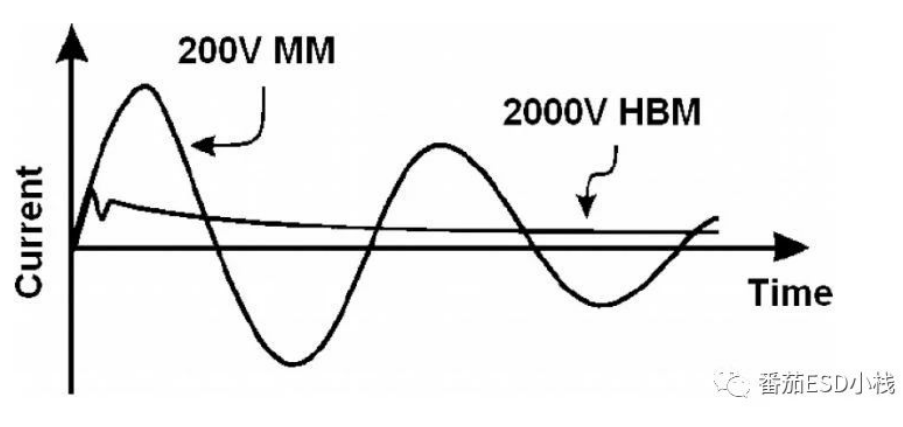

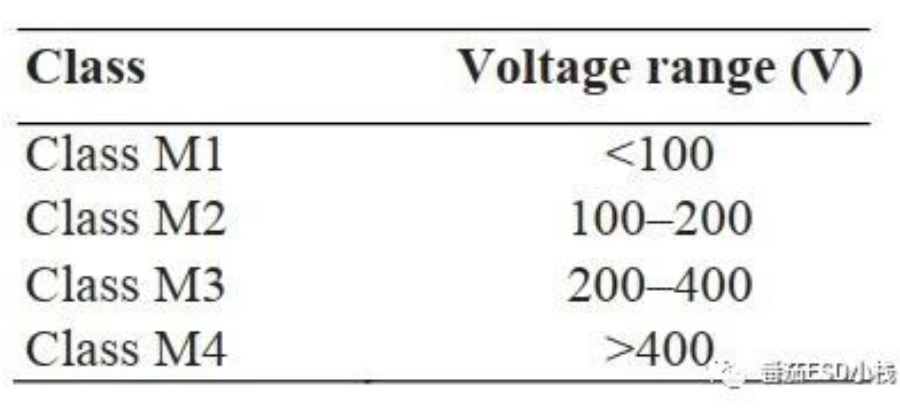

- 2.MM模型

MM与HBM模型相似,仿真的是机械设备接触芯片的情况。

图5.MM放电模型

图6.MM放电波形

图7.MM放电等级

MM放电模型也随着高度规范的生产流程,慢慢淡出人们的视线。现在业界将HBM与MM进行整合,制定了HMM模型。

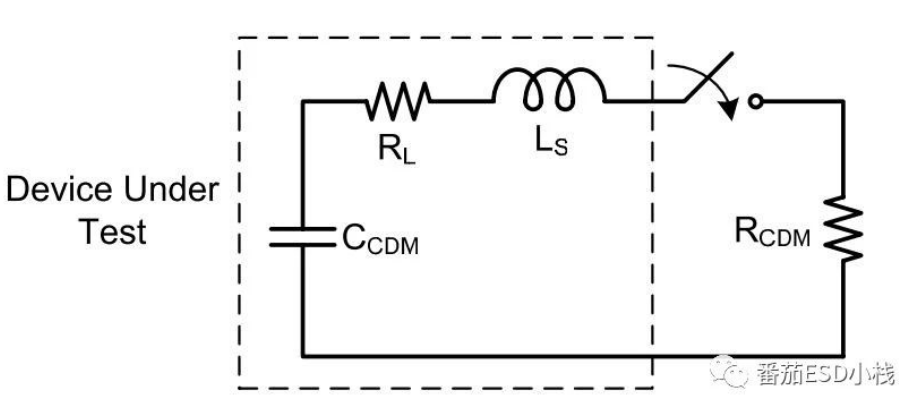

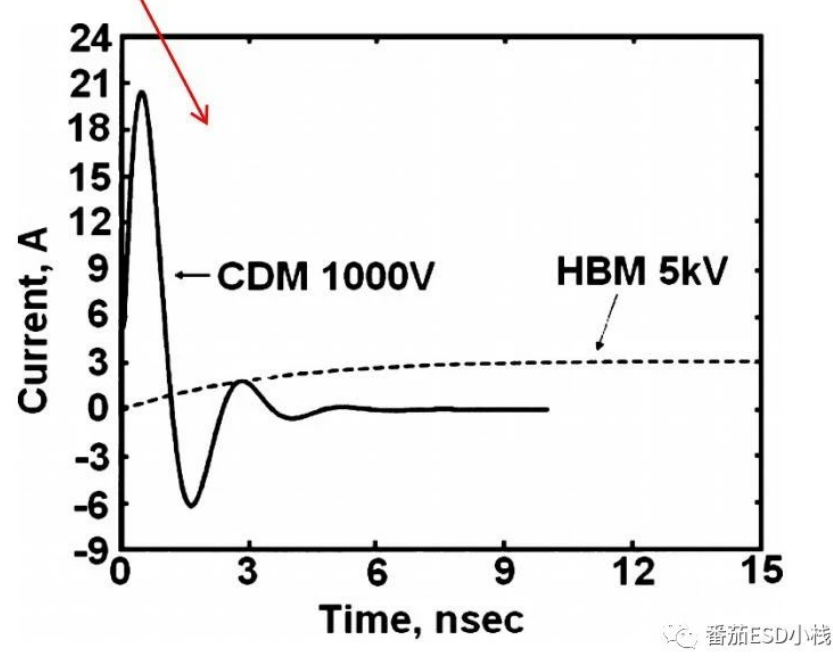

- 3.CDM模型

图8.CDM放电模型

图9.CDM放电模型

图10.CDM放电等级

CDM模型500V折算电流是10.4A。而且CDM的脉冲时间极短,大约~0.3ns达到电流最大值。

图11.CDM放电测试模型

4、射频IC ESD防护

射频芯片因其工作频率高,任何不受欢迎的寄生参数,在高频下都会加剧其负面影响,所以射频芯片对IO端口以及ESD防护单元有更加严苛的要求,且射频IC还会使用SiGe工艺,这进一步加大了ESD防护的设计难度。目前射频芯片的ESD防护有三种常见形式:

- 1.无缘器件

很多射频芯片在信号进入核心电路前需要在输入级/输出级利用无源RLC进行预处理,之后才会进入有源器件。

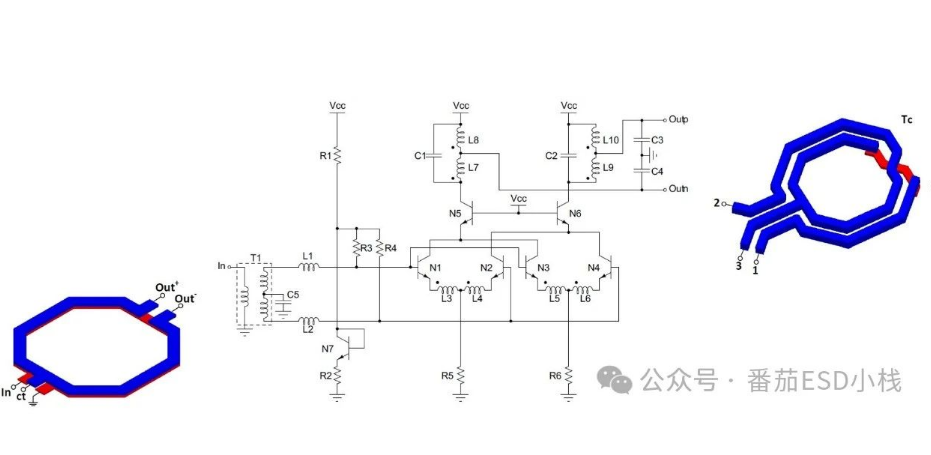

图12.LNA电路图

如图一所示,该电路的输入级采用Balun线圈。因为HBM的频谱集中在0.2GHZ~1GHZ范围内,其频率远低于信号频率,所以当ESD进入输入级后,会通过线圈泄放到GND,无法与内部电路产生感应。

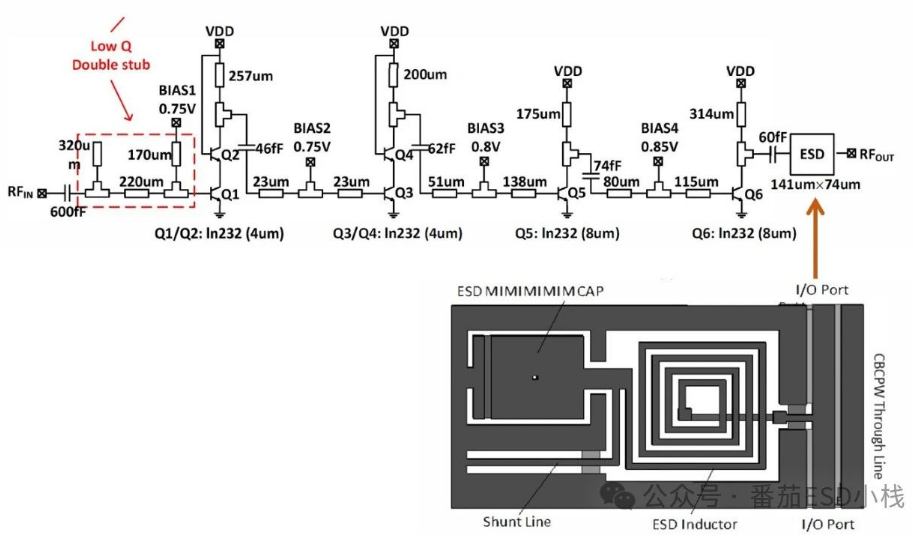

图13.PA电路图

如图二所示,该PA的输出级采用ESD Inductor + ESD MIM电容构成高通滤波电路,频率较低的ESD电流直接通过电感泄放到GND,该芯片利用无源器件构成的高通/带通滤波电路可以有效把ESD滤掉,避免ESD对内部电路产生破坏。

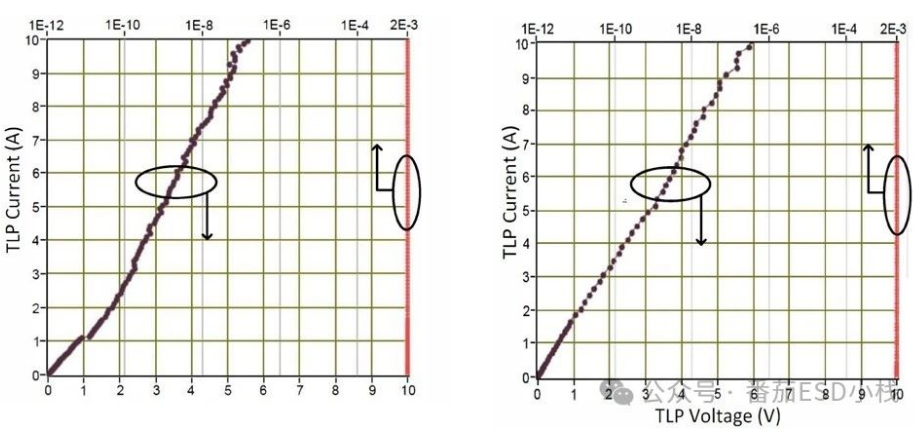

图14.电感TLP曲线

其TLP曲线如图三所示,在16KV HBM时压降不到6V。无源器件虽然很占面积,但是其ESD防护能力优异,同时还能与其它功能集成。

- 2.常规防护器件

在CMOS工艺下,寄生参数最为理想的器件当属SCR,其能满足部分射频芯片的需求,且面积远小于无源器件,泄放效率也较为优异,但是SCR Trigger Voltage过高的问题一直无法避免,即便是LVTSCR 其适用场景还是有限,完全无法针对SiGe HBT进行防护。而如果采用Diode + GCNMOS的方案,又会对信号频率产生限制。

- 3.ESD HBT器件

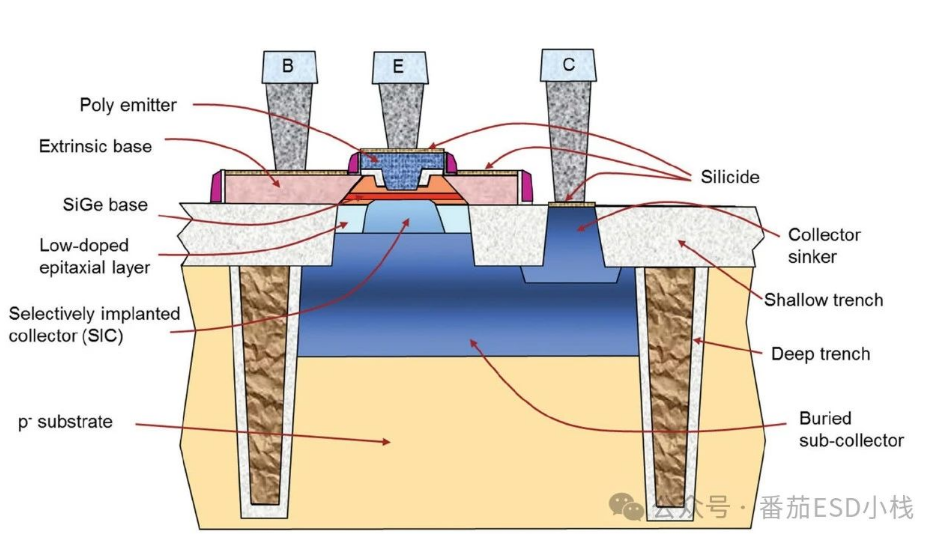

随着对更高频率的追求,射频芯片开始大规模使用SiGe工艺。SiGe工艺中最具代表性的器件便是HBT(Heterojunction bipolar transistor)异质结型三极管。HBT相较于MOSFET具有更大的集电极电流;更高的截止频率;更优异的噪声特性;更出色的高温特性等。如图四所示为HBT的结构示意图,其是由n-单晶Si/p+ 单晶SiGe/n+多晶Si 构成的异质结三极管,所以该器件的ESD特征与MOS、Bipolar都有差异。

图15.HBT器件结构图

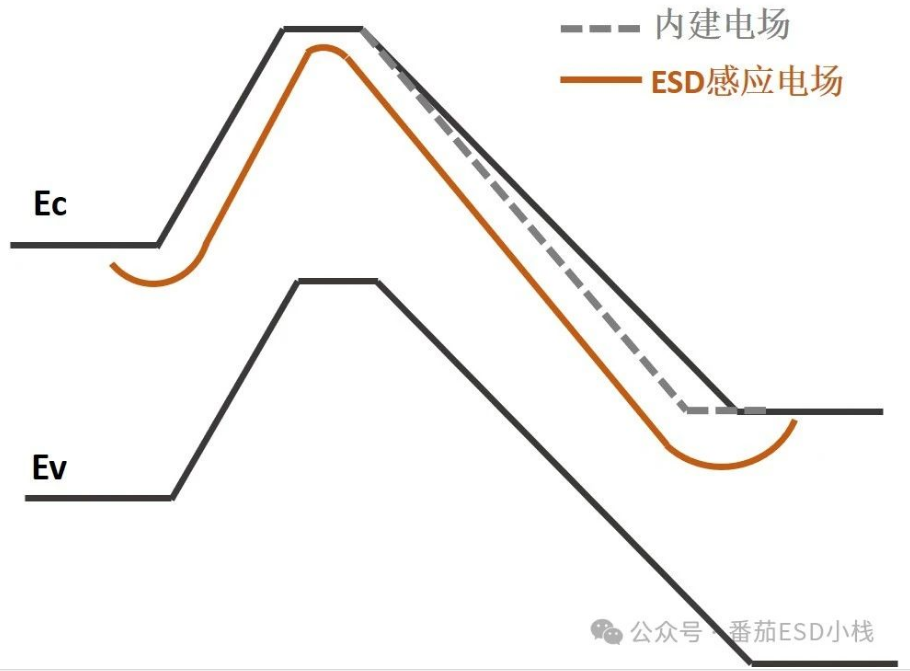

因为SiGe的扩散系数和迁移率与Si有所差异,所以HBT可以在维持高电流增益倍数的同时对基级进行高浓度掺杂,HBT器件拥有更大的集电极电流和更优异的频率特性。但是这些特性都是在小注入模型下实现的,如果面临ESD/EOS非常规模型时,SiGe HBT的鲁棒性较弱。如图五所示,SiGe与Si的界面处会产生一个自建电场,这个电场在ESD下会降低击穿势垒,但是也让器件更容易失效(器件承受内建电场+反偏电压的能量和)。

图16.HBT在ESD下的能带变化

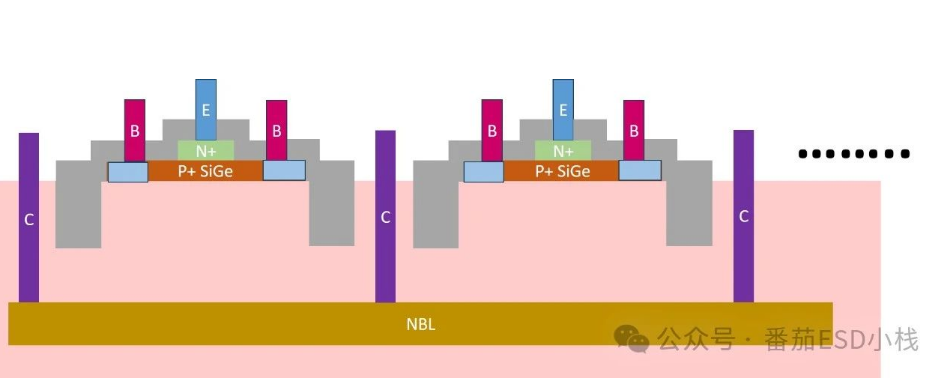

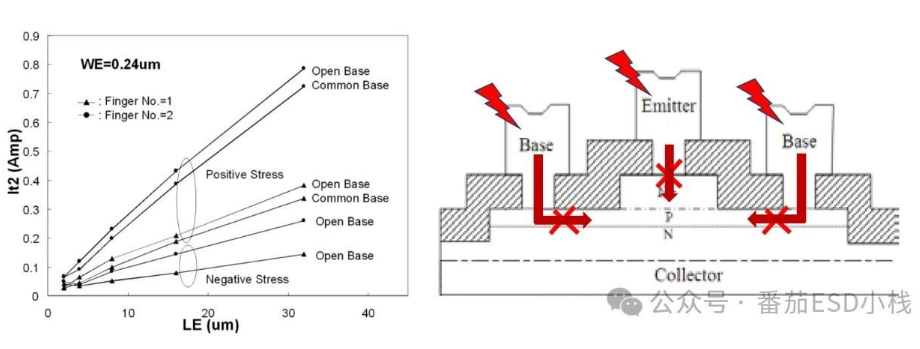

- 1.增加Finger数目

因为单个器件的泄放效率有限,就需要增加Finger数目来提高总效率。

图17.HBT 多Finger数目

- 2.采用Open Base结构

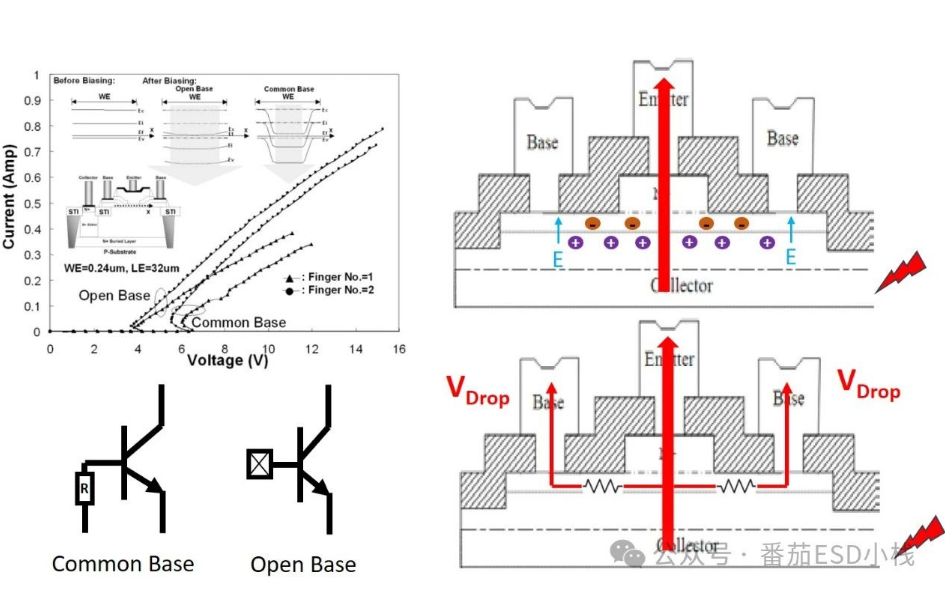

如图18所示,Open Base是将HBT的Base浮空,Common Base是将 HBT的基级接地。当基级浮空,集电极与基级发生雪崩击穿后,大量载流子聚集在异质结界面处形成感应电场,感应电场能进一步降低势垒,让更多的载流子到达射电极,使三极管导通,发生Snap Back,所以Open Base的Trigger Voltage较低。反之Common Base是将基级接地,在集电极与基级发生雪崩击穿后,大量载流子通过基级流出体系,在基级产生一个压降VDrop,从而开启三极管,发生Snap Back,但是Common Base的Trigger Voltage相对较高。两种连接方式都能发生Snap Back,但是机理不一样,所以Trigger Voltage会产生差异。因为HBT本身就存在内建电场,所以Floating Base与Ground Base的区别比较显著,而传统BJT因为没有内建电场,Floating Base与Ground Base的差异不会这么明显。

图18.HBT采用Open Base与Common Base的区别

Open Base基级不会有大电流经过,器件的ESD防护能力要优于Common Base。Common Base中会有大电流从Base流出体系,会削弱器件的防护能力。

- 3.单独建立反向ESD通道

如图19所示,HBT器件中SiGe做为基级的横向电阻率很高,过ESD电流的能力欠佳。射电极作为高掺杂多晶硅其热电性能欠佳,这两种因素造成了HBT面对负向ESD的性能很差。所以需要另外建立负向ESD泄放通道。

图19.HBT的负向ESD性能

浙公网安备 33010602011771号

浙公网安备 33010602011771号