JESD204B(1)——总体概要

1. 简介

JESD204是一种连接数据转换器(ADC和DAC)和逻辑器件的高速串行接口,该标准的 B 修订版支持高达 12.5 Gbps串行数据速率(目前C修订版已经发布,即JESD204C),并可确保 JESD204 链路具有可重复的确定性延迟。随着高速ADC跨入GSPS范围,与FPGA(定制ASIC)进行数据传输的首选接口协议是JESD204B。

在上一篇有关SerDes的博客《SerDes基础知识总结》中提到,JESD204B的物理层是基于SerDes的,所以JESD204B理所当然的继承了SerDes的优点,即:

- 更小的封装尺寸与更低的封装成本

- 简化的 PCB 布局与布线

- 高灵活布局

- 扩展能力强:该接口能够自适应不同数据转换器分辨率。

那么JESD204B有什么缺点呢?第一个缺点就是:复杂!真要对接口理解透彻的话,需要阅读很多资料。第二个缺点:有一定的时延,不适用于实时性要求高的场合,因为数据从发送到接收有一定的延迟。

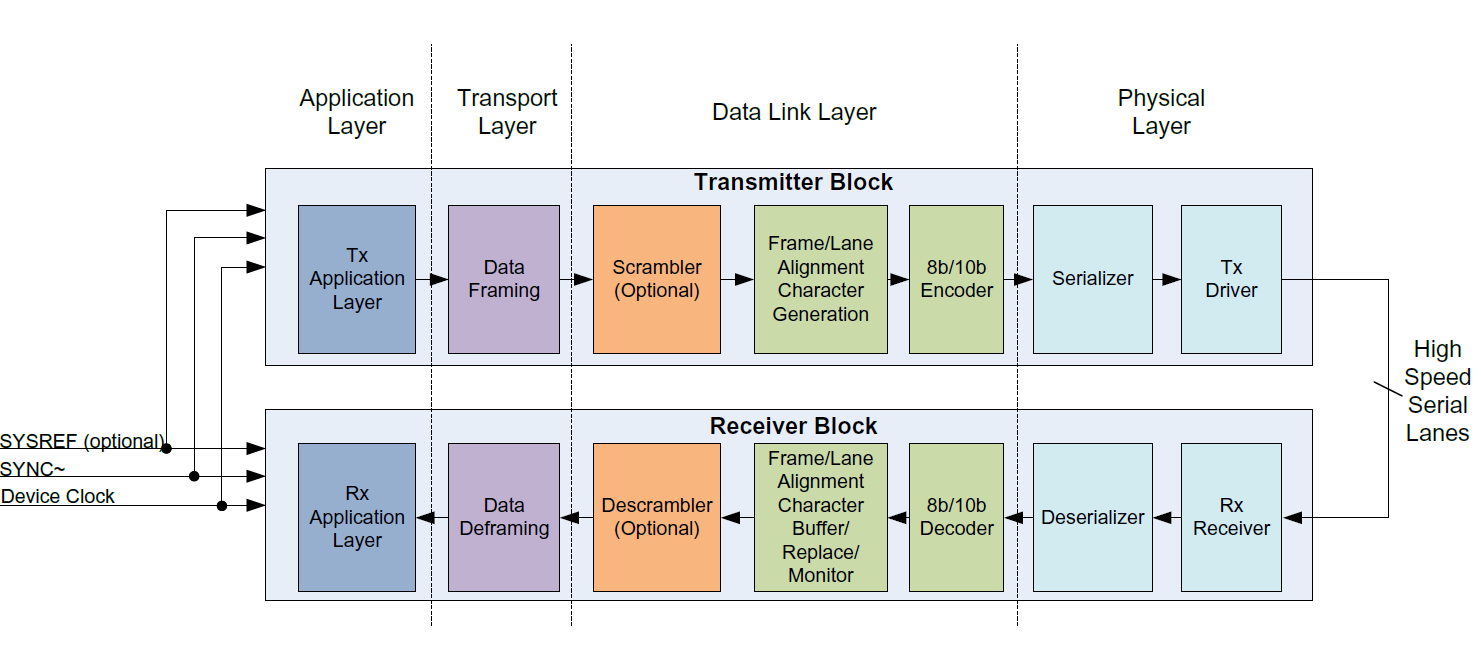

JESD204B与PCIE类似,其标准是一种分层规范,规范中的各层都有自己的功能要完成。如下图所示为JESD204B的分层框图。

下面就一一介绍各层完成的基本功能。

2. 分层简介

2.1 应用层(Application Layer)

通过应用层可以实现特殊用户配置。参考文献1中提到:

对于需要以不同于N'(每个样本传输的位数)的样本大小传输数据的ADC,以独特方式配置应用层可能有利。可以将多个样本重新包装,从而降低通道速率,提高链路整体效率。

我的理解是:当多个发送器模块和一个接收器模块连接时,如果发送器(ADC)的样本大小不一致,在接收端可以进行特殊配置,通过补位或者合包的方式,使每一个接受的数据包大小都相同?(PS:待实际调试接口后再来理解这一个功能)

2.2 传输层(Transport Layer)

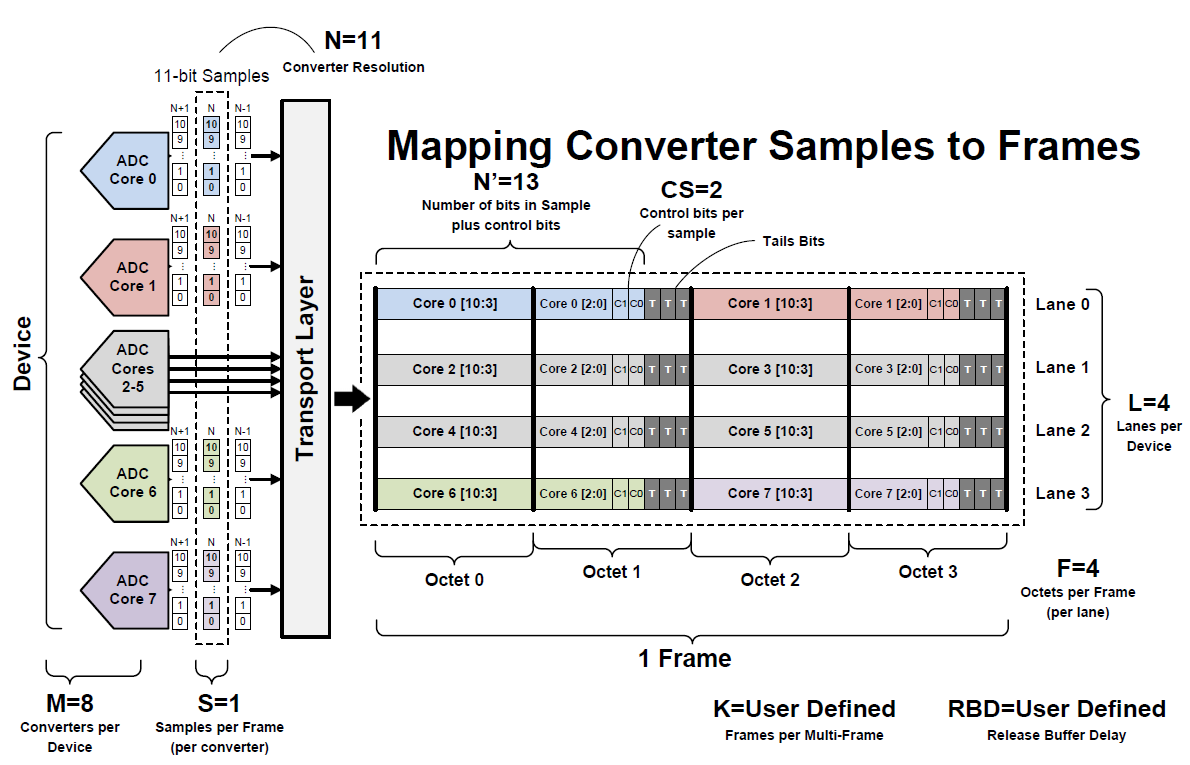

传输层根据给定器件已定义的链路配置参数,决定如何包装来自ADC的数据,即LMFS参数配置,四个字母代表最主要的四个参数,收发两端协商好之后(ADC会将参数发给FPGA,双方会进行校验),就按规则进行组包和解包。在下一篇博客JESD204B(2)——理解链路配置参数中,着重说明了配置参数的含义以及参数是如何影响链路组包以及传输速率的,这是理解JESD204B的重点之一。用下图来大概说明一下传输层的作用,8个ADC通过一定的方式组合在4条链路中进行传输。

2.3 数据链路层(Data Link Layer)

数据链路层主要是完成链路建立和数据编码(编码有的时候有划分在物理层中)。数据编码主要是加扰(可选)和8B/10B编码,其主要作用在《SerDes基础知识总结》中有介绍,这里就不再赘述。链路建立是也是JESD204B重点掌握的知识之一。

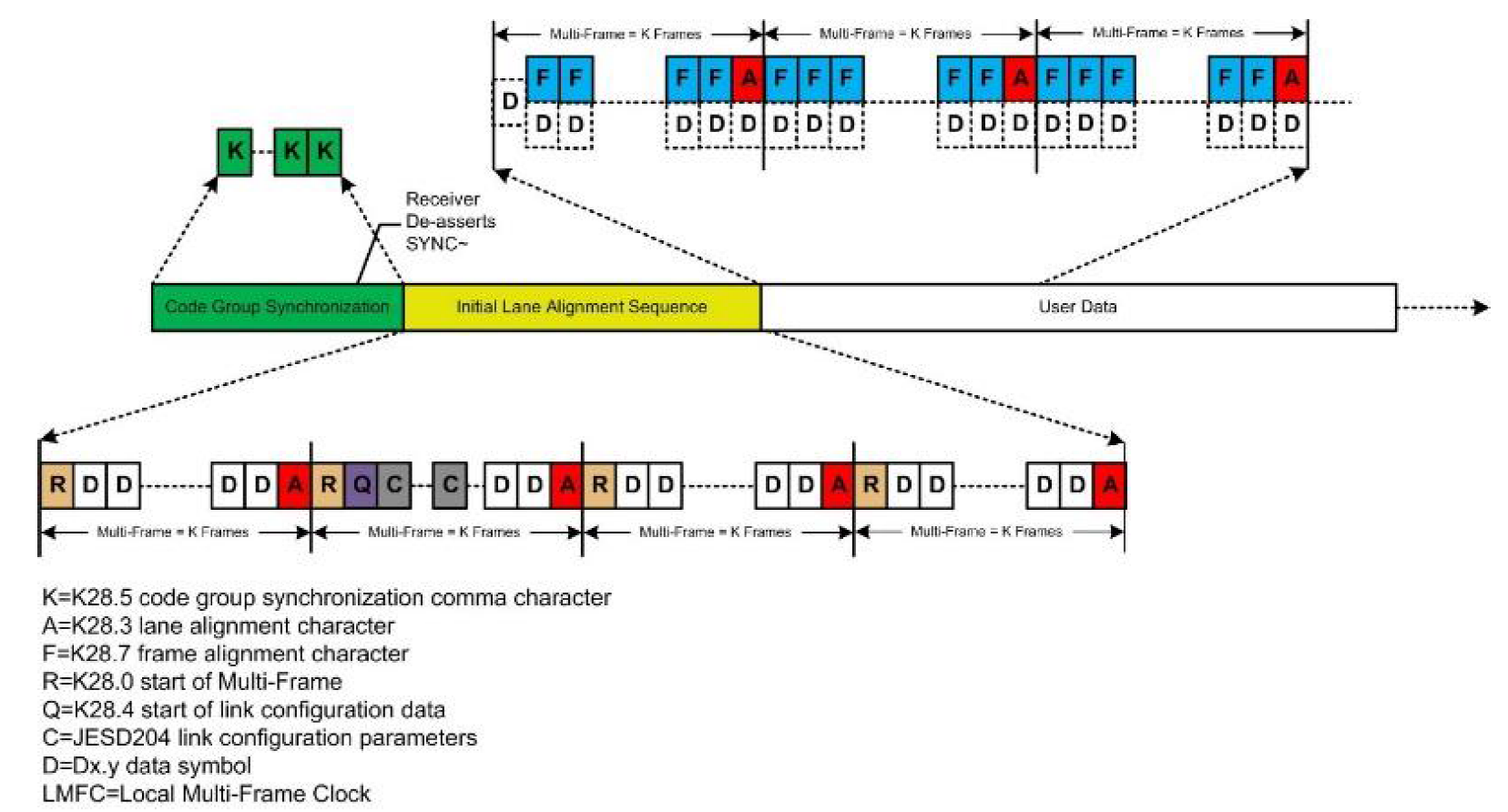

数据链路层通过链路建立过程同步JESD204B链路。链路建立包括三个不同阶段:

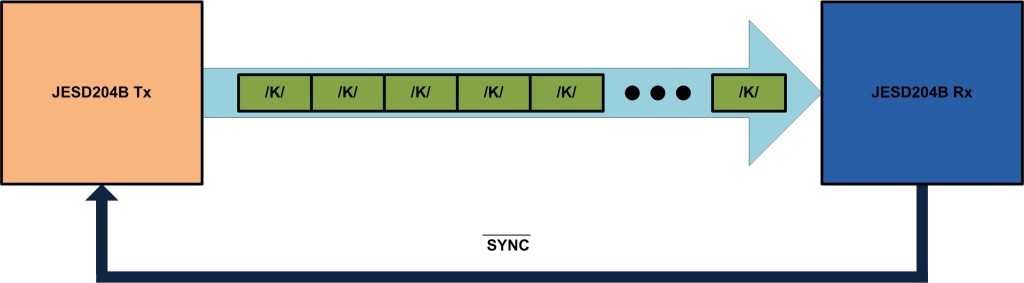

- 代码组同步(CGS)

在代码组同步(Code Group Synchronization,CGS)期间,各接收器(FPGA)必须利用时钟和数据恢复(CDR)技术,在ADC传来的输入数据流中找到K28.5字符。一旦在所有链路通道上检测到某一数量的连续K28.5字符,接收器模块就会解除置位送至发送器模块的SYNC~ 信号。在发送端捕获到SYNC~ 的变化后,JESD204A和JESD204B的处理会略有不同。在JESD204A中,发送模块捕捉SYNC~ 信号的变化,经过固定数量的帧时钟之后,ILAS就会启动。在JESD204B中,发送模块捕捉SYNC~ 信号的变化,并在下一个本地多帧时钟(LMFC)边界上启动ILAS。

- 初始通道对齐序列(ILAS)

ILAS(Initial Lane Alignment Sequence)的主要作用是对齐链路的所有通道,验证链路参数,以及确定帧和多帧边界在接收器的输入数据流中的位置。

ILAS由4个或更多多帧组成。第一、第三和第四个多帧以/R/字符开始,以/A/字符结束。第二个多帧包含/R/和/Q/字符,随后是链路参数。/Q/字符表示之后的数据是链路配置参数。如果接收器需要,ILAS可以添加其它多帧。最后一个ILAS多帧的最后一个/A/字符出现后,用户数据开始。

- 用户数据

在这一阶段,用户数据根据发送器(ADC)中定义并转发到接收器(FPGA)的链路参数,以流形式从发送器传输到接收器。达到用户数据阶段后,如果需要,通过数据链路中的字符替换可以监视并纠正帧和通道对齐。

如下图所示,为整个链路层数据链路建立的图示。实际上链路层除了要理解协议之外,还有理解对齐过程中各信号的时序关系,包括SYNC~ 、 LMFC,后面有时间再专门梳理指示信号和同步时钟的关系。

2.4 物理层(Physical Layer)

在物理层中,数据进行串行化,8B/10B编码数据以线路速率发送和接收。JESD204的物理层实际上就是SerDes结构,具体可参见《SerDes基础知识总结》。在物理层主要是要关注电气特性,通过眼图来测量信号完整性。

3. 总结

这篇博客基本上我是看了很多资料,稍微对JESD204B有一定的理解之后,从参考文献1中筛选出来的有助的快速入门的内容。实际上理解透JESD204B还有很多知识点要学习,并且结合实际调试观察信号和数据变化。接下来需要学习的是JESD204B的三个子类(相当于三种模式)的特点,通过各个时钟和信号之间的关系来确定延迟(这也是B修正版中的重要内容,这一方面还没理解透),以及通过信号关系对错误的表征等,后面有机会再慢慢展开。

参考文献

- 《了解JESD204B规范的各层——从高速ADC的角度出发》_ADI

- JESD204B:适合您吗?

- Link synchronization and alignment in JESD204B: Understanding control characters

浙公网安备 33010602011771号

浙公网安备 33010602011771号